## **BM T43 - DIGITAL LOGIC THEORY AND DESIGN**

## UNIT – 1

## PART – A

#### 1. State De-Morgan's Theorems. (May 2016, May 2019)

#### **De-Morgan's Theorems:**

- Two theorems that are an important part of Boolean algebra were proposed by De-Morgan.

- The first theorem states that the complement of a product is equal to the sum of the complements.

| (AB)' = A' + B' |

|-----------------|

|-----------------|

The second theorem states that the complement of a sum is equal to the product of the complements.

$$(A+B)' = A'. B'$$

## 2. Compare two main features of TTL and CMOS logic gates. (May 2016)

- 1. For TTL it is 4.75 V to 5.25 V while for CMOS it ranges between 0 to 1/3 VDD at a low level and 2/3VDD to VDD at high levels.

- 2. CMOS technology is **more economical** and preferred more as compared to the TTL logic.

- 3. The current requirements of the CMOS are low compared to TTL and thus **power consumption is limited**. Therefore it is easier for the circuits to be designed with the best power management.

3. Write the maxterms corresponding to the logical expression. Y = (A + B + C') (A + B' + C') (A' + B' + C). (Nov. 2016)

Y = (A + B + C')(A + B' + C')(A' + B' + C)

=M1.M3.M6

$= \prod M(1,3,6)$

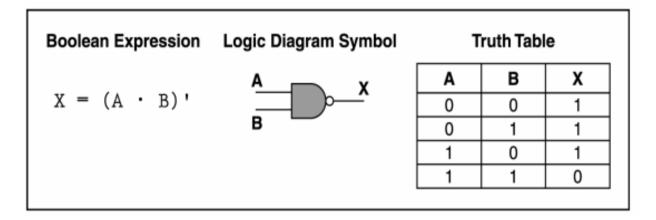

## 4. Why NAND and NOR gates are called as universal gates? (Nov. 2016)

The NAND and NOR gates are known as universal gates, since any logic function can be implemented using NAND or NOR gates.

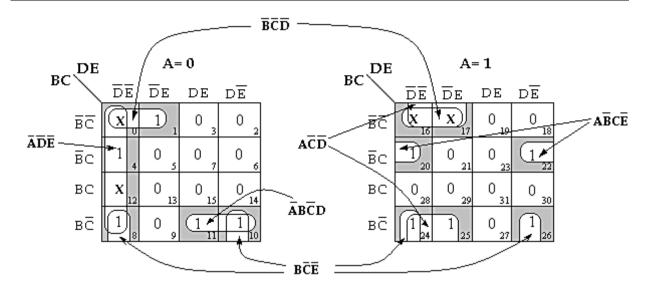

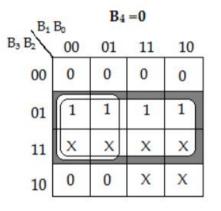

5. Minimize the Boolean expression F (A, B, C, D, E) = ∑m (1, 4, 8, 10, 11, 20, 22, 24, 25, 26)+∑d (0, 12, 16, 17) by k-map method. (May 2017)

Soln:

F(A, B, C, D, E) = B'C'D' + A'D'E' + BC'E' + A'BC'D + AC'D' + AB'CE'

## 6. What is a Hamming code? (May 2017)

Hamming code is a set of error-correction codes that can be used to detect and correct the errors that can occur when the data is moved or stored from the sender to the receiver.

Hamming code can be generated using 'even parity' or 'odd parity'.

## 7. State duality principle. (Dec. 2017)

Duality property states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged. If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

## 8. What are universal gates? (Dec. 2017)

- 1. NAND gate

- 2. NOR gate

## 9. Convert the following binary code into gray code. 1010111000<sub>2</sub> (May 2018)

Gray Code = 1111100100

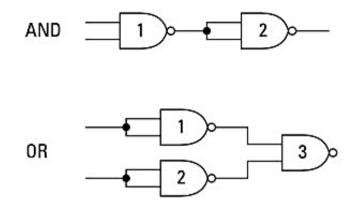

## 10. Construct OR gate and AND gate using NAND gate. (May 2018)

## 11. Convert decimal 25 to XS3 and to gray. (May 2019)

25 in XS3

According to excess-3 code we need to add 3 to both digit in the decimal number then convert into 4-bit binary number for result of each digit. Therefore, 25 + 33 = 58 = BCD value

#### XS3 of 25 is 0101 1000

25 in gray code

Divide 25 by 2 = 1212 divide by 2 = 66 divide by 2 = 33 divide by 2 = 1I divide by 2 = 0The remainder is 10011 rewrite in reverse order 11001 Perform the EX-OR operation for each term in binary

| Binary | Gray code             |

|--------|-----------------------|

| 1 ]    | 1                     |

| 1 -    | 1 1 = 0               |

| 0      | 10 = 1                |

| 0      | $\rightarrow 0 0 = 0$ |

| 1      | 0 1 =1                |

Gray code 25=10101

## 12. Determine the decimal value of the fractional binary number 0.10101. (Dec. 2019)

$\begin{array}{l} 0\cdot 2^{0} + 1\cdot 2^{-1} + 0\cdot 2^{-2} + 1\cdot 2^{-3} + 0\cdot 2^{-4} + 1\cdot 2^{-5} = 0\cdot 1 + 1\cdot 0.5 + 0\cdot 0.25 + 1\cdot 0.125 + 0\cdot 0.0625 + 1\cdot 0.03125 \\ = 0 + 0.5 + 0 + 0.125 + 0 + 0.03125 \\ = 0.65625_{10} \end{array}$

$0.10101_2 = \!\! 0.65625_{10}$

## 13. Prove that X(X +Z) =X, using Boolean algebra. (Dec. 2019)

X(X + Z) = X L.H.S. = X (X + Z) = X X + XZ = X + XZ, = X + XZ, = X (1 + Z), = X (1 + Z), = X + Z = 1 = X + Z = 1 = X + Z = 1

L.H.S. = R.H.S.

#### PART - B

## **1.** Generate hamming code for a 4-bit excess-3 message to detect and correct single bit errors. (May 2016)

Hamming code is a set of error-correction codes that can be used to detect and correct the errors that can occur when the data is moved or stored from the sender to the receiver.

Hamming code can be generated using 'even parity' or 'odd parity'.

A detailed explanation of generating a Hamming code is given below.

Given that;

To generate Hamming code for a 4-bit excess 3 code.

An excess 3 code is nothing but the adding of a binary 3 to the binary code.

| Decimal | Binary code(BCD) | Excess-3 code |

|---------|------------------|---------------|

|         | 8 4 2 1          | BCD + 011     |

| 0       | 0 0 0 0          | 0 0 1 1       |

|         | 0 0 0 0          |               |

|         | +                |               |

|         | 0 0 1 1          |               |

|         | 0 0 1 1          |               |

| 1 | 0 | 0 | 0 | 1 |  | 0 | 1 | 0 | 0 |

|---|---|---|---|---|--|---|---|---|---|

| 2 | 0 | 0 | 1 | 0 |  | 0 | 1 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 |  | 0 | 1 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 |  | 0 | 1 | 1 | 1 |

| 5 | 0 | 1 | 0 | 1 |  | 1 | 0 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 |  |   |   |   |   |

| 7 | 0 | 1 | 1 | 1 |  |   |   |   |   |

|   |   |   |   |   |  |   |   |   |   |

#### Picking a 4-bit excess 3 code message;

Let the message  $m = (0 \ 1 \ 0 \ 1)$

#### Generating a Hamming code (using even parity):

Message  $(m) = (0\ 1\ 0\ 1)$

To determine the parity bits:

$2^{P} > or = P+m+1$

Here m = 4 (Given it is 4-bit message)

Let P = 1

$2^{1} > or = 1 + 4 + 1$ ? No

Let P = 2

$2^2 > or = 2 + 4 + 1$ ? No

## Let P = 3

$2^{3} > \text{or} = 3 + 4 + 1$ ? Yes

So, the number of parity bits = 3 (P1, P2, P3)

Hence, the Hamming code consists of m+P = 4+3 = 7 bits

#### Hamming code:

| 1  | 2  | 3  | 4  | 5  | 6  | 7  |

|----|----|----|----|----|----|----|

| P1 | P2 | m1 | P3 | m2 | m3 | m4 |

| P1 | P2 | 0  | P3 | 1  | 0  | 1  |

Parity bits lie in the power of 2 positions  $(2^{0}, 2^{1}, ....)$

We simply fill the message bits in the remaining positions.

## Finding the parity bits (using even parity):

## $P1 \longrightarrow 1 \ 3 \ 5 \ 7 \longrightarrow P1 \ 0 \ 1 \ 1 \Longrightarrow P1 = 0$

## **Explanation:**

P1 is the first parity bit.

We need to pick the bits from the positions 1 3 5 7. This is because these digits in binary format contain a 1 in the 1st position.

- 1. 0001

- 3. 0011

- 5. 0101

- 7. 0111

So we get, (P1 0 1 1).

Since, we are considering even parity, P1 = 0, so that there are even number of 1's.

Similarly, we determine other values of P

#### $P2 \longrightarrow 2 \ 3 \ 6 \ 7 \longrightarrow P2 \ 0 \ 0 \ 1 \implies P2 = 1$

[2, 3, 6, 7 contain a 1 in the 2nd position]

$P3 \longrightarrow 4 5 6 7 \longrightarrow P3 1 0 1 \implies P3 = 0$

[4, 5, 6, 7 contain a 1 in the 3rd position]

Now, we have the parity bits and the message bits.

The generated hamming code is;

(P1 P2 m1 P3 m2 m3 m4)

0 1 0 0 1 0 1

2. Simplify the expression Y = ABCD + AB'C'D' + AB'C +AB. Convert this expression into a minterm SOP form and then simplify using Karnaugh Map. (May 2016, May 2019, Sept. 2020)

Y = ABCD + AB'C'D' + AB'C + AB

= ABCD + AB'C'D' + AB'C (D+D') + AB (C+C') (D+D')

= ABCD + AB'C'D' + AB'CD + AB'CD' + (ABC + ABC') (D + D')

= ABCD+ AB'C'D'+ AB'CD+ AB'CD'+ ABCD+ ABCD'+ ABC'D+ ABC'D'

= ABCD+ AB'C'D'+ AB'CD+ AB'CD'+ ABCD'+ ABC'D+ ABC'D'

= m15 + m8 + m11 + m10 + m14 + m13 + m12

$= \sum m (8, 10, 11, 12, 13, 14, 15)$

Therefore, Y= AB+ AC+ AD'

## 3. Determine the prime implicants of the following function and verify using K map F (A, B, C, D) = $\sum (0, 2, 3, 5, 7, 8, 9, 10, 11, 13, 15)$ . (Nov. 2016)

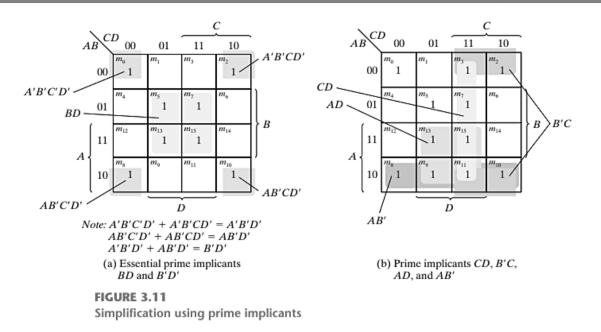

The prime implicant is essential if it is the only prime implicant that covers the minterm. The minterms of the function are marked with 1's in the maps of Fig. 3.11. The partial map (Fig. 3.11(a)) shows two essential prime implicants, each formed by collapsing four cells into a term having only two literals.

One term is essential because there is only one way to include minterm m0 within four adjacent squares. These four squares define the term BD. Similarly, there is only one way that minterm m5 can be combined with four adjacent squares, and this gives the second term B'D'.

The two essential prime implicants cover eight minterms. The three minterms that were omitted from the partial map (m3, m9, and m11) must be considered next. Figure 3.11 (b) shows all possible ways that the three minterms can be covered with prime implicants.

Minterm m3 can be covered with either prime implicant CD or prime implicant B'C. Minterm m9 can be covered with either AD or AB'. Minterm m11 is covered with any one of the four prime implicants. The simplified expression is obtained from the logical sum of the two essential prime implicants and any two prime implicants that cover minterms m3, m9, and m11. There are four possible ways that the function can be expressed with four product terms of two literals each:

$$F = BD + B'D' + CD + AD$$

$$= BD + B'D' + CD + AB'$$

$$= BD + B'D' + B'C + AD$$

$$= BD + B'D' + B'C + AB'$$

The previous example has demonstrated that the identification of the prime implicants in the map helps in determining the alternatives that are available for obtaining a simplified expression. The procedure for finding the simplified expression from the map requires that we first determine all the essential prime implicants. The simplified expression is obtained from the logical sum of all the essential prime implicants, plus other prime implicants that may be needed to cover any remaining minterms not covered by the essential prime implicants. Occasionally, there may be more than one way of combining squares, and each combination may produce an equally simplified expression.

## 4. Explain the digital logic families: (a) CMOS logics (b) TTL. (Nov. 2016, Dec. 2019)

## **Digital Logic Family**

There are various logic families namely – Diode logic (DL) Resistor-Transistor logic (RTL) Diode-Transistor logic (DTL) Emitter coupled logic (ECL) Logic families can be classified broadly according to the technologies they are built with Emitter coupled logic (ECL) Transistor-Transistor logic (TTL) CMOS logic TTL and CMOS logic family is most widely used IC technologies. Within each family, several subfamilies of logic types are available, with different rating for speed, power consumption, temperature range, voltage level and current level.

## (a) CMOS (Complementary Metal Oxide Semiconductor)

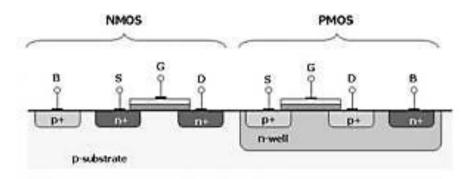

The main <u>advantage of CMOS over NMOS</u> and BIPOLAR technology is the much smaller power dissipation. Unlike NMOS or BIPOLAR circuits, a Complementary MOS circuit has almost no static power dissipation. Power is only dissipated in case the circuit actually switches. This allows integrating more CMOS gates on an IC than in NMOS or <u>bipolar technology</u>, resulting in much better performance. Complementary Metal Oxide Semiconductor transistor consists of P-channel MOS (PMOS) and N-channel MOS (NMOS). Please refer to the link to know more about <u>the fabrication process of CMOS transistor</u>.

CMOS (Complementary Metal Oxide Semiconductor)

## NMOS

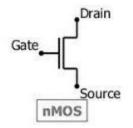

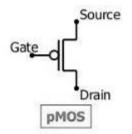

NMOS is built on a p-type substrate with n-type source and drain diffused on it. In NMOS, the majority of carriers are electrons. When a high voltage is applied to the gate, the NMOS will conduct. Similarly, when a low voltage is applied to the gate, NMOS will not conduct. NMOS is considered to be faster than PMOS, since the carriers in NMOS, which are electrons, travel twice as fast as the holes.

NMOS Transistor

#### PMOS

P- channel MOSFET consists of P-type Source and Drain diffused on an N-type substrate. The majority of carriers are holes. When a high voltage is applied to the gate, the PMOS will not conduct. When a low voltage is applied to the gate, the PMOS will conduct. The PMOS devices are more immune to noise than NMOS devices.

**PMOS** Transistor

## **CMOS Working Principle**

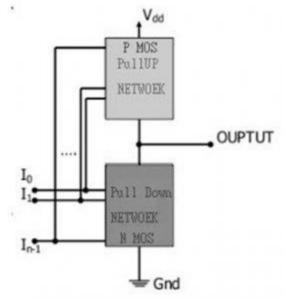

In CMOS technology, both N-type and P-type transistors are used to design logic functions. The same signal which turns ON a transistor of one type is used to turn OFF a transistor of the other type. This characteristic allows the design of logic devices using only simple switches, without the need for a pull-up resistor.

In CMOS <u>logic gates</u> a collection of n-type MOSFETs is arranged in a pull-down network between the output and the low voltage power supply rail (Vss or quite often ground). Instead of the load resistor of NMOS logic gates, CMOS logic gates have a collection of p-type MOSFETs in a pull-up network between the output and the higher-voltage rail (often named Vdd).

CMOS using Pull Up & Pull Down

Thus, if both a p-type and n-type transistor have their gates connected to the same input, the p-type MOSFET will be ON when the n-type MOSFET is OFF, and vice-versa. The networks are arranged such that one is ON and the other OFF for any input pattern as shown in the figure.

CMOS offers relatively high speed, low power dissipation, high noise margins in both states, and will operate over a wide range of source and input voltages (provided the source voltage is fixed). Furthermore, for a better understanding of the Complementary Metal Oxide Semiconductor working principle, we need to discuss in brief CMOS logic gates as explained below.

#### Which Devices use CMOS?

Technology like CMOS is used in different chips like microcontrollers, microprocessors, SRAM (static RAM) & other digital logic circuits. This technology is used in a wide range of analog circuits which includes data converters, image sensors & highly incorporated transceivers for several kinds of communication.

## **CMOS Inverter**

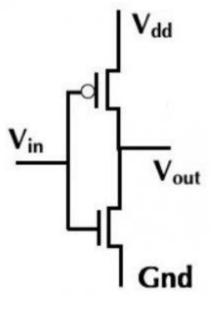

The inverter circuit as shown in the figure below. It consists of <u>PMOS and NMOS</u> <u>FET</u>. The input A serves as the gate voltage for both transistors.

The NMOS transistor has input from Vss (ground) and the PMOS transistor has input from Vdd. The terminal Y is output. When a high voltage (~ Vdd) is given at input terminal (A) of the inverter, the PMOS becomes an open circuit, and NMOS switched OFF so the output will be pulled down to Vss.

**CMOS** Inverter

When a low-level voltage (<Vdd, ~0v) applied to the inverter, the NMOS switched OFF and PMOS switched ON. So the output becomes Vdd or the circuit is pulled up to Vdd.

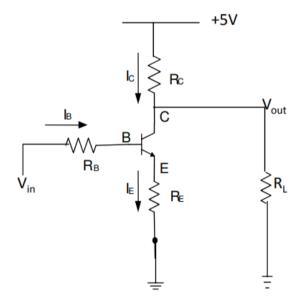

#### (b) TTL (Transistor-Transistor logic)

Transistor Transistor Logic (TTL) Family One basic function of TTL IC is as a complimenting switch or inverter. When Vin equals 1 (+5V), the transistor is turned on (saturation) and Vout equals 0 (0V). When Vin equals 0 (0V), the transistor is turned off and Vout equals 1 (5V), assuming RL > R C

$$V_{out} = V_{CC} \frac{R_L}{(R_C + R_L)}$$

Thus level 1 of inverter output is very much dependent on RL , which can typically vary by factor of 10. Thus we need very small R C compared to RL i.e. RL >> RC.

But when transistor is saturated (Vout = 0V), IC will be very large if RC is very small. Thus we need large RC when transistor is in saturation and small RC when transistor is off.

The idea of variable R C is accommodated by TTL IC.

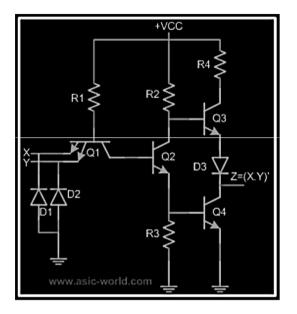

Transistor Transistor Logic (TTL) Family Q3 is cutoff (act like a high RC ) when output transistor Q4 is saturated and Q3 is saturated (act like a low RC ) when output transistor Q4 is cutoff .

Thus one transistor is ON at one time. The combination of Q3 and Q4 is called The idea of variable R C is accommodated by TTL IC. It uses another transistor Q3 in place of R C to act like a varying resistance. The combination of Q3 and Q4 is called totem pole arrangement. Q1 is called input transistor, which is multi-emitter transistor, that drive transistor Q2 which is used to control Q3 and Q4. Diode D1 and D2 is used to protect Q1 from unwanted negative voltages and diode D3 ensures when Q4 is ON, Q3 is OFF. Multi-emitter input transistor is a striking feature of TTL logic family.

## 5. With the necessary circuit diagram, explain the features and working of TTL NAND gate. (May 2017, Sept. 2020)

TTL gates use a  $5V(\pm 0.25V)$  supply, and are capable of high-speed operation. Over 600 different logic ICs are available, covering a very wide range of digital functions. Due to the use of bipolar transistors, TTL has much higher power consumption than similar CMOS types, when working at relatively low frequencies. As the frequency of signals handled increases however, this difference decreases as the power consumption of CMOS increases and TTL power consumption remains nearly constant.

## TTL NAND gate

This circuit looks similar to those found in analogue push pull amplifiers, except that the transistors here are driven either into cut-off or saturation, rather than working in their linear operating condition. Also, being constucted within an IC, it can use a device not normally found in conventional analogue amplifiers, a multi emitter transistor.

- R1 is a low value resistor (about 4K) and as the base current of T1 is small, the base voltage is about +5V. If both emitters of T1 are at logic 1, (also around +5V), there will be very little potential difference between base and emitter, and T1 will be turned off. As T1 is not conducting, its collector will also be at about 5V, and due to this high potential, T2 base will have a higher potential than its emitter, which will cause T2 to conduct heavily and go into saturation.

- T2 collector will therefore fall to a low potential, and the emitter voltage of T2 will rise due to the current flow through R3. The voltage across R3 will rise to a sufficient level (about 0.7V) to fully turn on T3. As T3 saturates, its collector voltage will fall to about 0.2V, thus giving a logic 0 state at the output terminal.

- > T4 emitter voltage is made up of T3 V<sub>CE</sub> (about 0.2V) plus the forward voltage drop across D1, which will be about 0.7V, giving an emitter potential of 0.2V + 0.7V = 0.9V, the same as its base voltage.

Schematic diagram of a TTL NAND Gate

- > The base potential of T4 is made up of T3 base/emitter potential  $V_{BE}$  (about 0.7V), plus the collector/emitter, potential ( $V_{CE}$ ) of T2, (about 0.2V), giving a base voltage for T4 of about 0.9V. Therefore the base and emitter voltages on T4 are approximately equal, so T4 will be turned off.

- With BOTH input terminals are at logic 1 therefore, the output terminal will be at logic 0, the correct operation for a NAND gate.

- If either one of the inputs is taken to logic 0 however, this will make T1 conduct, as the emitter that is at logic 0 will be at a lower voltage than that supplied to the base by R1. This will cause T1 to saturate, taking its collector to a low potential (less than 0.8V) and as this is also connected to T2 base T2 will turn off, making its collector voltage and T4 base voltage, rise to very nearly +Vcc.

- ➤ As virtually no current ( $I_{CE}$ ) is flowing through T2 collector/emitter circuit, practically no voltage is developed across the emitter resistor R3, reducing T3 base voltage to 0V, and so T3 is turned off. However, sufficient current will be flowing out of the output terminal (feeding the next gate input circuit) to cause T4 emitter to be held at about 4.1V. This is 0.9V below +Vcc, made up of the voltage across D1 (0.7V) plus the saturation voltage V<sub>CE</sub> of T4 (0.2V). This places about 4V or logic 1 (between 2.4V and 5V) on the output terminal.

6. (a) Draw the logic symbol and construct the truth table for each of the following gates: (i) Two input NAND gate (ii) Three input OR gate (iii) NOT gate. (May 2017)

NAND GATE

OR GATE

**Boolean Expression:** X = A + B + C

|         |   | TR | UTH TAB | ILE.   |

|---------|---|----|---------|--------|

|         |   |    | 3       | OUTPUT |

| OR Gate | w | x  | Y       | Z      |

|         | 0 | 0  | 0       | 0      |

| Z=W+X+Y | 0 | 0  | 1       | 1      |

| 3       | о | 1  | О       | 1      |

| 2       | 0 | 1  | 1       | 1      |

|         | 1 | 0  | 0       | 1      |

|         | 1 | 0  | 1       | 1      |

|         | 1 | 1  | 0       | 1      |

|         | 1 | 1  | 1       | 1      |

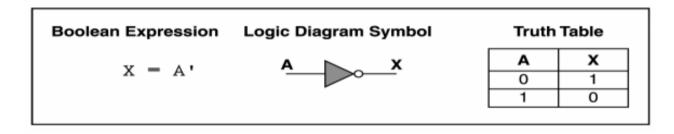

NOT GATE

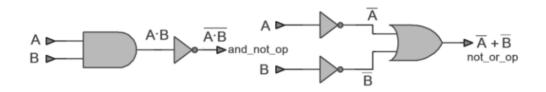

## 6. (b) State and explain De-Morgan's Theorem. (May 2017)

#### **De-Morgan's Theorem**

De-Morgan was a great logician and mathematician. He had contributed much to logic. Among his contribution the following two theorems are important.

#### **De-Morgan's First Theorem**

It States that —The complement of the sum of the variables is equal to the product of the complement of each variable. This theorem may be expressed by the following Boolean expression.

$$(AB)' = A' + B'$$

## **Digital Circuit**

**Truth table**

| Α | В | Ā | B | A·B | A·B | $\overline{A} + \overline{B}$ |

|---|---|---|---|-----|-----|-------------------------------|

| 0 | 0 | 1 | 1 | 0   | 1   | 1                             |

| 0 | 1 | 1 | 0 | 0   | 1   | 1                             |

| 1 | 0 | 0 | 1 | 0   | 1   | 1                             |

| 1 | 1 | 0 | 0 | 1   | 0   | 0                             |

#### **De-Morgan's Second Theorem**

It states that the —Complement of the product of variables is equal to the sum of complements of each individual variable. Boolean expression for this theorem is

| (A+B)' = A'. B' |

|-----------------|

|                 |

## **Digital Circuit**

## Truth table

| Α | В | Ā | B | A+B | A+B | Ā·B |

|---|---|---|---|-----|-----|-----|

| 0 | 0 | 1 | 1 | 0   | 1   | 1   |

| 0 | 1 | 1 | 0 | 1   | 0   | 0   |

| 1 | 0 | 0 | 1 | 1   | 0   | 0   |

| 1 | 1 | 0 | 0 | 1   | 0   | 0   |

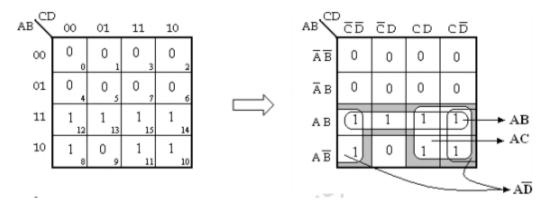

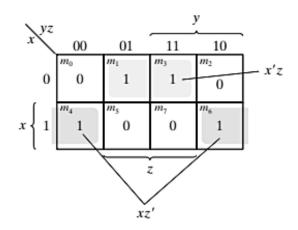

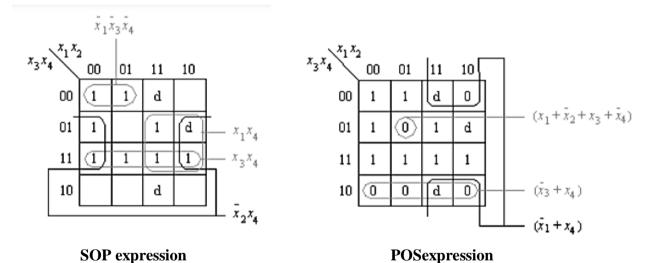

7. Using K-map reduce the following Boolean expression and realize it in both POS and SOP form. F (A, B, C, D) = (0, 1, 2, 5, 8, 9, 10).(Dec. 2017)

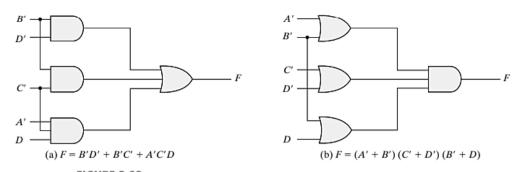

The 1's marked in the map represent all the minterms of the function. The squares marked with 0's represent the minterms not included in F and therefore denote the complement of F. Combining the squares with 1's gives the simplified function in sum-of-products form:

(a) F = B'D' + B'C' + A'C'D

If the squares marked with 0's are combined, as shown in the diagram, we obtain the simplified complemented function:

$$F' = AB + CD + BD'$$

Applying DeMorgan's theorem, we obtain the simplified function in product of-sums form:

(b)

$$F = (A' + B') (C' + D') (B' + D)$$

F(A, B, C, D) = (0, 1, 2, 5, 8, 9, 10) = B'D' + B'C' + A'C'D = (A' + B')(C' + D')(B' + D)

FIGURE 3.13 Gate implementations of the function of Example 3.7

| Table 3.1<br>Truth Table of Function F |   |   |   |  |  |  |

|----------------------------------------|---|---|---|--|--|--|

| x                                      | y | z | F |  |  |  |

| 0                                      | 0 | 0 | 0 |  |  |  |

| 0                                      | 0 | 1 | 1 |  |  |  |

| 0                                      | 1 | 0 | 0 |  |  |  |

| 0                                      | 1 | 1 | 1 |  |  |  |

| 1                                      | 0 | 0 | 1 |  |  |  |

| 1                                      | 0 | 1 | 0 |  |  |  |

| 1                                      | 1 | 0 | 1 |  |  |  |

| 1                                      | 1 | 1 | 0 |  |  |  |

The gate-level implementation of the simplified expressions are obtained. The sumof-products expression is implemented in (a) with a group of AND gates, one for each AND term. The outputs of the AND gates are connected to the inputs of a single OR gate. The same function is implemented in (b) in its product-of-sums form with a group of OR gates, one for each OR term. The outputs of the OR gates are connected to the inputs of a single AND gate.

In each case, it is assumed that the input variables are directly available in their complement, so inverters are not needed. The configuration pattern established in Fig is the general form by which any Boolean function is implemented when expressed in one of the standard forms. AND gates are connected to a single OR gate when in sum-of-products form; OR gates are connected to a single AND gate when in product-of-sums form.

Either configuration forms two levels of gates. Thus, the implementation of a function in a standard form is said to be a two-level implementation. The two-level implementation may not be practical, depending on the number of inputs to the gates. The procedure is also valid when the function is originally expressed in the product-of-maxterms canonical form. Consider, for example, the truth table that defines the function F in Table.

In sum-of-minterms form, this function is expressed as F(x, y, z) = (1, 3, 4, 6)

K – map for the above truth table

In product-of-maxterms form, it is expressed as F(x, y, z) = (0, 2, 5, 7)

In other words, the 1's of the function represent the minterms and the 0's represent the maxterms. The map for this function is shown in fig .

One can start simplifying the function by first marking the 1's for each minterm that the function is a 1. The remaining squares are marked by 0's. If, instead, the product of maxterms is initially given, one can start marking 0's in those squares listed in the function; the remaining squares are then marked by 1's.

Once the 1's and 0's are marked, the function can be simplified in either one of the standard forms.

For the sum of products, we combine the 1's to obtain

$$\mathbf{F} = \mathbf{x'z} + \mathbf{xz'}$$

For the **product of sums**, we combine the **0's** to obtain the simplified complemented function

$$\mathbf{F} = \mathbf{x}\mathbf{z} + \mathbf{x'}\mathbf{z'}$$

which shows that the exclusive-OR function is the complement of the equivalence function.

Taking the complement of F, we obtain the simplified function in product-of-sums form:

$$\mathbf{F} = (\mathbf{x}^2 + \mathbf{z}^2)(\mathbf{x} + \mathbf{z})$$

To enter a function expressed in product-of-sums form into the map, use the complement of the function to find the squares that are to be marked by 0's.

For example, the function

F = (A' + B' + C')(B + D)

can be entered into the map by first taking its complement, namely,

## $\mathbf{F} = \mathbf{ABC} + \mathbf{B'D'}$

and then marking 0's in the squares representing the minterms of F. The remaining squares are marked with 1's.

## 8. Reduce the following logic function using Quine – McClusky method. $f(W,X,Y,Z)=\sum m(2,6,8,9,10,11,14,15)$ .(Dec. 2017)

Procedure of Quine-McCluskey Tabular Method

Follow these steps for simplifying Boolean functions using Quine-McClukey tabular method.

Step 1 – Arrange the given min terms in an **ascending order** and make the groups based on the number of ones present in their binary representations. So, there will be **at most 'n+1' groups** if there are 'n' Boolean variables in a Boolean function or 'n' bits in the binary equivalent of min terms.

Step 2 – Compare the min terms present in successive groups. If there is a change in only one-bit position, then take the pair of those two min terms. Place this symbol '\_' in the differed bit position and keep the remaining bits as it is.

Step 3 – Repeat step2 with newly formed terms till we get all prime implicants.

Step 4 – Formulate the prime implicant table. It consists of set of rows and columns. Prime implicants can be placed in row wise and min terms can be placed in column wise. Place '1' in the cells corresponding to the min terms that are covered in each prime implicant.

**Step 5** – Find the essential prime implicants by observing each column. If the min term is covered only by one prime implicant, then it is **essential prime implicant**. Those essential prime implicants will be part of the simplified Boolean function.

**Step 6** – Reduce the prime implicant table by removing the row of each essential prime implicant and the columns corresponding to the min terms that are covered in that essential prime implicant. Repeat step 5 for Reduced prime implicant table. Stop this process when all min terms of given Boolean function are over.

## $f(W,X,Y,Z)=\sum m(2,6,8,9,10,11,14,15)$ using Quine-McClukey tabular method.

The given Boolean function is in **sum of min terms** form. It is having 4 variables W, X, Y & Z. The given min terms are 2, 6, 8, 9, 10, 11, 14 and 15. The ascending order of these min terms based on the number of ones present in their binary equivalent is 2, 8, 6, 9, 10, 11, 14 and 15. The following table shows these **min terms and their equivalent binary** representations.

| Group Name | Min terms | W | Х | Y | Z |

|------------|-----------|---|---|---|---|

| GA1        | 2         | 0 | 0 | 1 | 0 |

|     | 8  | 1 | 0 | 0 | 0 |

|-----|----|---|---|---|---|

|     | 6  | 0 | 1 | 1 | 0 |

| GA2 | 9  | 1 | 0 | 0 | 1 |

|     | 10 | 1 | 0 | 1 | 0 |

| GA3 | 11 | 1 | 0 | 1 | 1 |

|     | 14 | 1 | 1 | 1 | 0 |

| GA4 | 15 | 1 | 1 | 1 | 1 |

The given min terms are arranged into 4 groups based on the number of ones present in their binary equivalents. The following table shows the possible **merging of min terms** from adjacent groups.

| Group Name | Min terms | W | X | Y | Z |

|------------|-----------|---|---|---|---|

|            | 2,6       | 0 | _ | 1 | 0 |

| GB1        | 2,10      | - | 0 | 1 | 0 |

|            | 8,9       | 1 | 0 | 0 | - |

|            | 8,10      | 1 | 0 | _ | 0 |

| GB2        | 6,14      | - | 1 | 1 | 0 |

|            | 9,11      | 1 | 0 | - | 1 |

|     | 10,11 | 1 | 0 | 1 | - |

|-----|-------|---|---|---|---|

|     | 10,14 | 1 | - | 1 | 0 |

| GB3 | 11,15 | 1 | - | 1 | 1 |

|     | 14,15 | 1 | 1 | 1 | - |

The min terms, which are differed in only one-bit position from adjacent groups are merged. That differed bit is represented with this symbol, '-'. In this case, there are three groups and each group contains combinations of two min terms. The following table shows the possible **merging of min term pairs** from adjacent groups.

| Group Name | Min terms   | W | X | Y | Z |

|------------|-------------|---|---|---|---|

|            | 2,6,10,14   | - | - | 1 | 0 |

| GB1        | 2,10,6,14   | - | - | 1 | 0 |

|            | 8,9,10,11   | 1 | 0 | _ | - |

|            | 8,10,9,11   | 1 | 0 | _ | _ |

| GB2        | 10,11,14,15 | 1 | - | 1 | - |

|            | 10,14,11,15 | 1 | - | 1 | - |

The successive groups of min term pairs, which are differed in only one-bit position are merged. That differed bit is represented with this symbol, '-'. In this case, there are two groups and each group contains combinations of four min terms. Here, these combinations of 4 min terms are available in two rows. So, we can remove the repeated rows. The reduced table after removing the redundant rows is shown below.

| Group Name | Min terms   | W | X | Y | Z |

|------------|-------------|---|---|---|---|

| GC1        | 2,6,10,14   | - | - | 1 | 0 |

|            | 8,9,10,11   | 1 | 0 | _ | - |

| GC2        | 10,11,14,15 | 1 | - | 1 | - |

Further merging of the combinations of min terms from adjacent groups is not possible, since they are differed in more than one-bit position. There are three rows in the above table. So, each row will give one prime implicant. Therefore, the **prime implicants** are YZ', WX' & WY.

The **prime implicant table** is shown below.

| Min terms / Prime<br>Implicants | 2 | 6 | 8 | 9 | 10 | 11 | 14 | 15 |

|---------------------------------|---|---|---|---|----|----|----|----|

| YZ'                             | 1 | 1 |   |   | 1  |    | 1  |    |

| WX'                             |   |   | 1 | 1 | 1  | 1  |    |    |

| WY                              |   |   |   |   | 1  | 1  | 1  | 1  |

The prime implicants are placed in row wise and min terms are placed in column wise. 1s are placed in the common cells of prime implicant rows and the corresponding min term columns.

The min terms 2 and 6 are covered only by one prime implicant **YZ'**. So, it is an **essential prime implicant**. This will be part of simplified Boolean function. Now, remove this prime implicant row and the corresponding min term columns. The reduced prime implicant table is shown below.

| Min terms / Prime<br>Implicants | 8 | 9 | 11 | 15 |

|---------------------------------|---|---|----|----|

| -                               |   |   |    |    |

| WX' | 1 | 1 | 1 |   |

|-----|---|---|---|---|

| WY  |   |   | 1 | 1 |

The min terms 8 and 9 are covered only by one prime implicant **WX'**. So, it is an **essential prime implicant**. This will be part of simplified Boolean function. Now, remove this prime implicant row and the corresponding min term columns. The reduced prime implicant table is shown below.

| Min terms / Prime<br>Implicants | 15 |

|---------------------------------|----|

| WY                              | 1  |

The min term 15 is covered only by one prime implicant **WY**. So, it is an **essential prime implicant**. This will be part of simplified Boolean function.

In this example problem, we got three prime implicants and all the three are essential. Therefore, the **simplified Boolean function** is

$\mathbf{F}(\mathbf{W},\mathbf{X},\mathbf{Y},\mathbf{Z}) = \mathbf{Y}\mathbf{Z'} + \mathbf{W}\mathbf{X'} + \mathbf{W}\mathbf{Y}.$

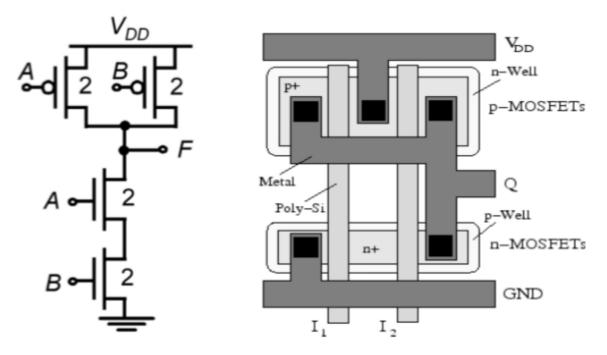

9. (a) Explain with an aid of circuit diagram the operation of 2 input CMOS NAND gate and list out its advantages over other logic families. (May 2018, Dec.2019)

## **CMOS Two-input NAND Gate**

The circuit diagram of the two input CMOS NAND gate is given in the figure below.

The principle of operation of the circuit is exact dual of the CMOS two input NOR operation. The n - net consisting of two series connected nMOS transistor creates a conducting path between the output node and the ground, if both input voltages are logic high. Both of the parallelly connected pMOS transistor in p-net will be off.

For all other input combination, either one or both of the pMOS transistor will be turn ON, while p – net is cut off, thus, creating a current path between the output node and the power supply voltage. The switching threshold for this gate is obtained as

$$V_{th}\left(NAND2

ight) = rac{V_{T,n} + 2\sqrt{rac{k_p}{k_n}(V_{DD} - |V_{T,p}|)}}{1 + 2\sqrt{rac{k_p}{k_n}}}$$

## The features of this layout are as follows -

- > Single polysilicon lines for inputs run vertically across both N and P active regions.

- Single active shapes are used for building both nMOS devices and both pMOS devices.

- > Power bussing is running horizontal across top and bottom of layout.

- > Output wires runs horizontal for easy connection to neighboring circuit.

#### Advantages

- The static power dissipation is more than double in case of NOR gate to that of NAND. This also depicts a slight increase in the dynamic power dissipation in case of NOR gate.

- > The comparison of rise time, fall time and delay show better results with NAND gate.

- > It is clearly shown that the delay is quite low for NAND gate.

> The area requirement is also lesser for NAND out of the other gates.

## 9. (b) Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction. (May 2018)

(a) X - Y and

(b) Y - X using 2's complements.

**a**)

$$X = 1010100$$

2's complement of Y = +0111101

-----

Sum = 10010001

Discard end carry

Answer: X - Y = 0010001

**b**) Y = 1000011

2's complement of X = +0101100

Sum = 1101111

\_\_\_\_\_

There is no end carry,

Therefore the answer is Y-X = -(2's complement of 1101111) = -0010001

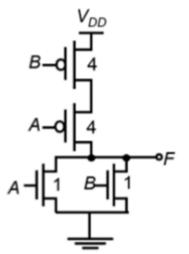

## 10. (a) Draw the CMOS logic circuit for NOR gate and explain its operation. (May 2017, May 2018, Dec. 2019, Sept. 2020)

## **CMOS Logic Circuits**

## **CMOS Two input NOR Gate**

The circuit consists of a parallel-connected n-net and a series-connected complementary p-net. The input voltages  $V_X$  and  $V_Y$  are applied to the gates of one nMOS and one pMOS transistor.

When either one or both inputs are high, i.e., when the n-net creates a conducting path between the output node and the ground, the p-net is cut—off. If both input voltages are low, i.e., the n-net is cut-off, then the p-net creates a conducting path between the output node and the supply voltage.

For any given input combination, the complementary circuit structure is such that the output is connected either to  $V_{DD}$  or to ground via a low-resistance path and a DC current

path between the  $V_{DD}$  and ground is not established for any input combinations. The output voltage of the CMOS, two input NOR gate will get a logic-low voltage of  $V_{OL} = 0$  and a logic-high voltage of  $V_{OH} = V_{DD}$ . The equation of the switching threshold voltage  $V_{th}$  is given by

$$V_{th}\left(NOR2

ight) = rac{V_{T,n} + rac{1}{2}\sqrt{rac{k_p}{k_n}(V_{DD} - |V_{T,p}|)}}{1 + rac{1}{2}\sqrt{rac{k_p}{k_n}}}$$

Layout of CMOS 2-input NOR Gate

The figure shows a sample layout of CMOS 2-input NOR gate, using single-layer metal and single-layer polysilicon. The features of this layout are -

- Single vertical polylines for each input

- Single active shapes for N and P devices, respectively

- Metal buses running horizontal

The stick diagram for the CMOS N0R2 gate is shown in the figure given below; which corresponds directly to the layout, but does not contain W and L information. The diffusion areas are depicted by rectangles, the metal connections and solid lines and circles, respectively represent contacts, and the crosshatched strips represent the polysilicon columns. Stick diagram is useful for planning optimum layout topology.

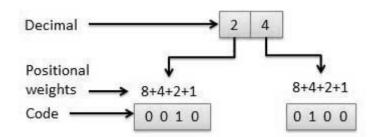

## 10. (b) Briefly discuss weighted binary code. (May 2018)

## **Classification of binary codes**

The codes are broadly categorized into following four categories.

- Weighted Codes

- Non-Weighted Codes

- Binary Coded Decimal Code

- Alphanumeric Codes

- Error Detecting Codes

- Error Correcting Codes

## Weighted Codes

Weighted binary codes are those binary codes which obey the positional weight principle. Each position of the number represents a specific weight. Several systems of the codes are used to express the decimal digits 0 through 9. In these codes each decimal digit is represented by a group of four bits.

1. The main characteristic of a weighted code is, each binary bit is assigned by a "weight" and values depend on the position of the binary bit.

- 2. The sum of the weights of these binary bits, whose value is 1 is equal to the decimal digit which they represent.

- 3. In other words, if w1, w2, w3 and w4 are the weights of the binary digits, and x1, x2, x3 and x4 are the corresponding bit values, then the decimal digit N=w4x4 + w3x3+w2x2+w1x1 is represented by the binary sequence x4x3x2x1.

- 4. A sequence of binary bits which represents a decimal digit is called a "code word".

- 5. Thus x4x3x2x1 is a code word of N.

- 6. Example of these codes is: BCD, 8421, 6421, 4221, 5211, 3321 etc.

- 7. Weighted codes are used in:

- a) Data manipulation during arithmetic operation.

- b) For input/output operations in digital circuits.

- c) To represent the decimal digits in calculators, volt meters etc.

In the example 4782 = number 3210 = positional values, the positional assignments 0 through 3 can be the weighted values of their assigned digits. So the weight of the 4 is 3 and the weight of the 7 is 2. The weight of a number comes into play when converting from any base numbering system to the decimal (base 10) numbering system.

One formula for converting a weighted number is to multiply each digit by its base to the power of its position, and then add all the resulting digits. In the example below, 100101, which is a binary base 2 number, is converted to a decimal (base 10) number.

100101 = Binary (base 2) number 543210 = positional weights (1 x 2^5) + (0 x 2^4) + (0 x 2^3) + (1 x 2^2) + (0 x 2^1) + (1 x 2^0) = 32 + 0 + 0 + 4 + 0 + 1 = 37 37 base 10 = decimal conversion

Other weighted methods include BCD and 2421, each of which uses a similar formula to assign weights and convert to decimal.

# 11. Use Karnaugh maps to find the minimum-cost SOP and POS expressions for the function

f(x1,...,x4) = x1x3x4 + x3x4 + x1x2x4 + x1x2x3x4 assuming that there are also don't-cares defined as D = (9, 12, 14). (May 2019)

## Solution:

The Karnaugh map is derived by placing 1s that correspond to each product term in the expression used to specify f. The term x1x3x4 corresponds to minterms 0 and 4. The term x3x4 represents the third row in the map, comprising minterms 3, 7, 11, and 15.

The term x1x2x4 specifies minterms 1 and 3. The fourth product term represents the minterm 13. The map also includes the three don't-care conditions. To find the desired SOP expression, we must find the least-expensive set of prime implicants that covers all 1s in the map.

The term x3x4 is a prime implicant which must be included because it is the only prime implicant that covers the minterm 7; it also covers minterms 3, 11, and 15. Minterm 4 can be covered with either x1x3x4 or x2x3x4.

Both of these terms have the same cost; we will choose  $x_1x_3x_4$  because it also covers the minterm 0. Minterm 1 may be covered with either  $x_1x_2x_3$  or  $x_2x_4$ ; we should choose the latter because its cost is lower. This leaves only the minterm 13 to be covered, which can be done with either  $x_1x_4$  or  $x_1x_2$  at equal costs. Choosing  $x_1x_4$ , **the minimum-cost SOP expression is**

#### f = x3x4 + x1x3x4 + x2x4 + x1x4

The sum term (x3 + x4) covers the 0s in the bottom row. To cover the 0 in square 8 we must include (x1 + x4). The remaining 0, in square 5, must be covered with (x1 + x2 + x3 + x4). Thus, **the minimum-cost POS expression is**

$$\mathbf{f} = (\mathbf{x}3 + \mathbf{x}4)(\mathbf{x}1 + \mathbf{x}4)(\mathbf{x}1 + \mathbf{x}2 + \mathbf{x}3 + \mathbf{x}4)$$

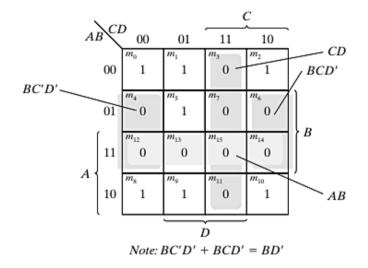

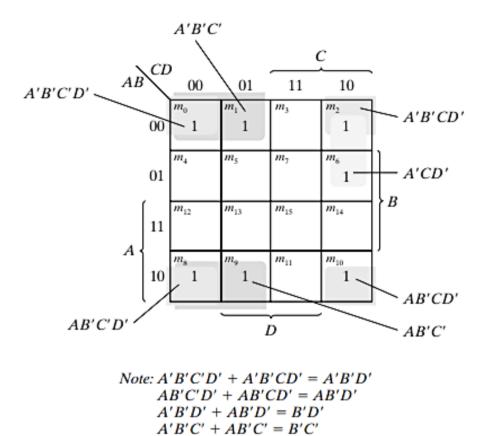

12. Reduce the following function using K map F = A'B'C' + B'CD' + A'BCD' + AB'C'. (Dec. 2019)

F = A'B'C' + B'CD' + A'BCD' + AB'C'

#### From k - map figure: A'B'C' + B'CD' + A'BCD' + AB'C' = B'D' + B'C' + A'CD'

The area in the map covered by this function consists of the squares marked with 1's. The function has four variables and, as expressed, consists of three terms with three literals each and one term with four literals. Each term with three literals is represented in the map by two squares. For example, A'B'C' is represented in squares 0000 and 0001. The function can be simplified in the map by taking the 1's in the four corners to give the term B'D'. This is possible because these four squares are adjacent when the map is drawn in a surface with top and bottom edges, as well as left and right edges, touching one another. The two left-hand 1's in the top row are combined with the two 1's in the bottom row to give the term B'C'. The remaining 1 may be combined in a two square area to give the term A'CD'.

The simplified function is **F** = **B'D'** + **B'C'** + **A'CD'**

## **BM T43-DIGITAL LOGIC THEORY AND DESIGN**

## UNIT 2

## PART – A

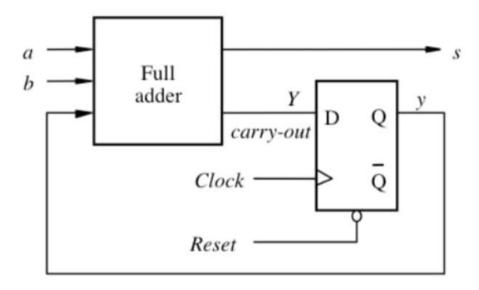

#### 1. Mention the types of adders. (May 2016)

- > Adder

- ➢ Half adder

- ➢ Full adder

- ➢ Ripple-carry adder

- ➢ Carry-look ahead adder

- ➢ Brent-Kung adder

- ➢ Kogge-Stone adder

- ➢ Carry-save adder

## 2. Which gate is suitable for building a comparator and why? (May 2016)

An EX-NOR gate is suitable for building a comparator because, an ex-nor outputs high for an even number of 1's or all 0's and outputs low for otherwise. Thus, an ex-nor gate is a basic comparator, because its output is "1" only if its two input bits are equal.

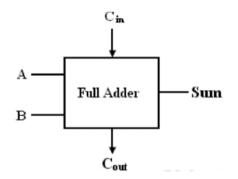

#### 3. Draw the structure of a full adder using two half adders (Nov. 2016)

#### 4. Mention the difference between demultiplexer and multiplexer. (Nov. 2016)

The major factor that differentiates multiplexer and demultiplexer is their ability to accept multiple input and single input respectively. The multiplexer also known as **MUX** operates on several inputs but provide a single output. As against demultiplexer also known as **DEMUX** simply reverses the operation of MUX and operates on single input but transmits the data on multiple outputs.

## 5. Design a single-bit magnitude comparator. (Nov. 2017)

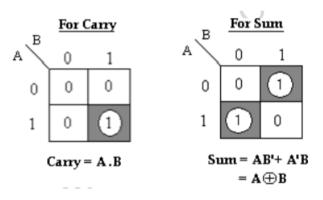

## 6. Write the expression for sum and carry for half adder (May 2017, Sep. 2020)

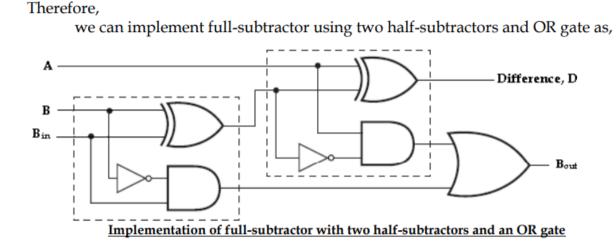

## 7. Implement a full adder using two half adders. (Nov. 2017)

#### 8. How does an encoder differ from a decoder (Nov. 2018, Nov. 2019)

Encoder circuit basically converts the applied information signal into a coded digital bit stream. Decoder performs reverse operation and recovers the original information signal from the coded bits. In case f encoder, the applied signal is the active signal input. Decoder accepts coded binary data as its input.

## 9. Draw 2-bit comparator using logic gates. (Nov. 2018)

10. Design half subtractor using basic gates. (May 2019)

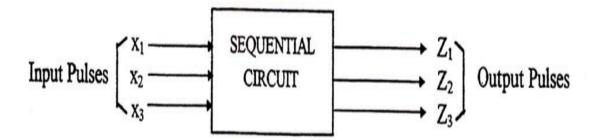

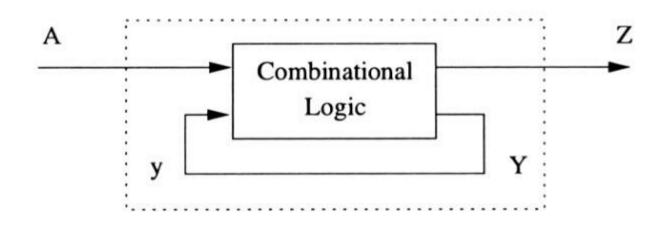

11. What do you mean by combinational circuits? Give example (Nov. 2019)

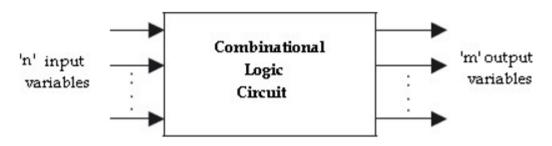

A combinational circuit consists of input variables, logic gates, and output variables. The logic gates accept signals from inputs and output signals are generated according to the logic circuits employed in it. Binary information from the given data transforms to desired output data in this process. Both input and output are obviously the binary signals, i.e., both the input and output signals are of two possible states, logic 1 and logic 0.

For n number of input variables to a combinational circuit, 2n possible combinations of binary input states are possible. For each possible combination, there is one and only one possible output combination. A combinational logic circuit can be described by m Boolean functions and each output can be expressed in terms of n input variables.

## **12.** Convert the given expression in canonical SOP form Y = AC+AB+BC (Nov. 2018)

$$Y (A, B, C) = AC + AB + BC$$

= AC (B+ B')+ AB (C+ C')+ BC (A+ A')

= ABC+ AB'C+ ABC+ ABC'+ ABC+ A'BC

= ABC+ AB'C+ ABC'+ A'BC

=  $\sum m (3, 5, 6, 7).$

## PART - B

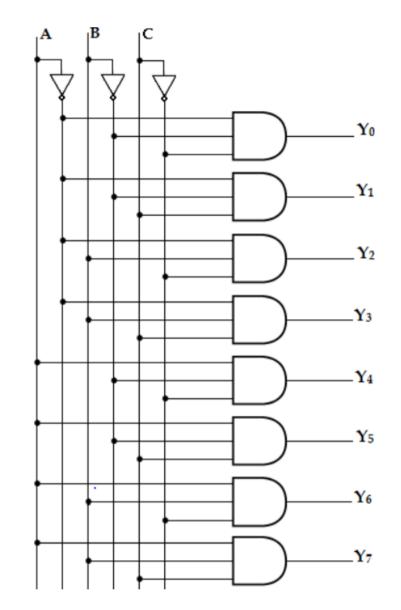

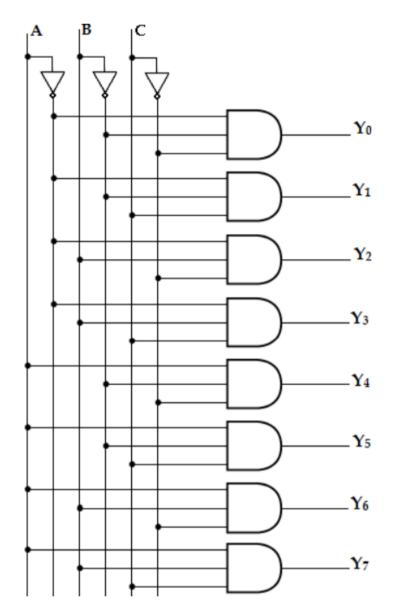

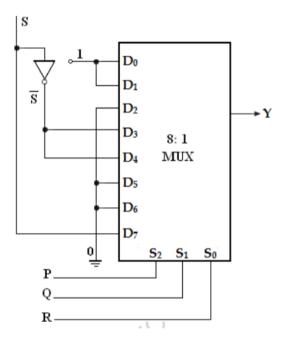

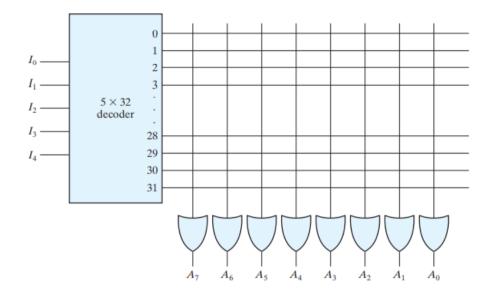

## 1. Design a 3 to 8 decoder. (May 2016, Sep. 2020)

A 3-to-8 line decoder has three inputs (A, B, C) and eight outputs (Y0- Y7). Based on the 3 inputs one of the eight outputs is selected. The three inputs are decoded into eight outputs, each output representing one of the minterms of the 3-input variables. This decoder is used for binary-to-octal conversion. The input variables may represent a binary number and the outputs will represent the eight digits in the octal number system. The output variables are mutually exclusive because only one output can be equal to 1 at any one time. The output line whose value is equal to 1 represents the minterms equivalent of the binary number presently available in the input lines.

|   | Inputs |   |                |                       |                | Out                   | puts |                       |                |                       |

|---|--------|---|----------------|-----------------------|----------------|-----------------------|------|-----------------------|----------------|-----------------------|

| Α | В      | С | Y <sub>0</sub> | <b>Y</b> <sub>1</sub> | Y <sub>2</sub> | <b>Y</b> <sub>3</sub> | Y4   | <b>Y</b> <sub>5</sub> | Y <sub>6</sub> | <b>Y</b> <sub>7</sub> |

| 0 | 0      | 0 | 1              | 0                     | 0              | 0                     | 0    | 0                     | 0              | 0                     |

| 0 | 0      | 1 | 0              | 1                     | 0              | 0                     | 0    | 0                     | 0              | 0                     |

| 0 | 1      | 0 | 0              | 0                     | 1              | 0                     | 0    | 0                     | 0              | 0                     |

| 0 | 1      | 1 | 0              | 0                     | 0              | 1                     | 0    | 0                     | 0              | 0                     |

| 1 | 0      | 0 | 0              | 0                     | 0              | 0                     | 1    | 0                     | 0              | 0                     |

| 1 | 0      | 1 | 0              | 0                     | 0              | 0                     | 0    | 1                     | 0              | 0                     |

| 1 | 1      | 0 | 0              | 0                     | 0              | 0                     | 0    | 0                     | 1              | 0                     |

| 1 | 1      | 1 | 0              | 0                     | 0              | 0                     | 0    | 0                     | 0              | 1                     |

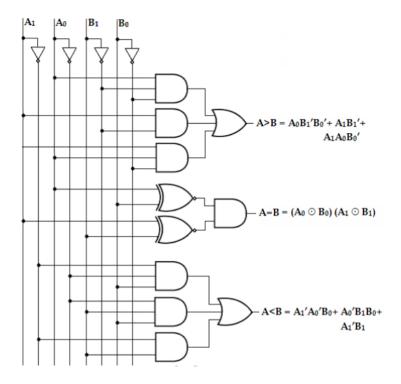

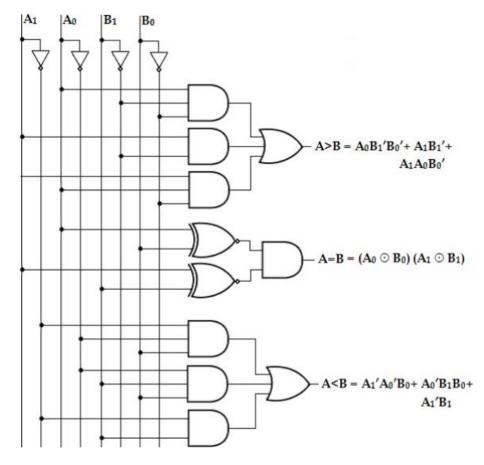

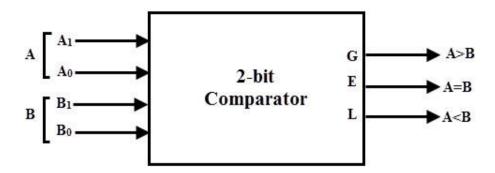

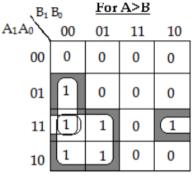

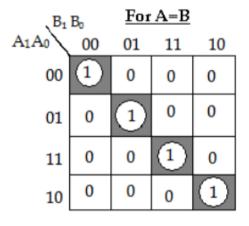

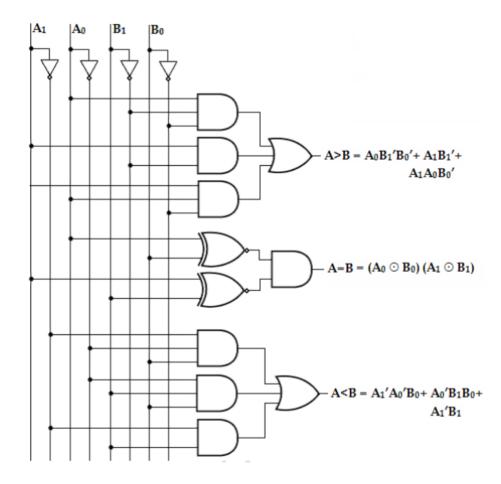

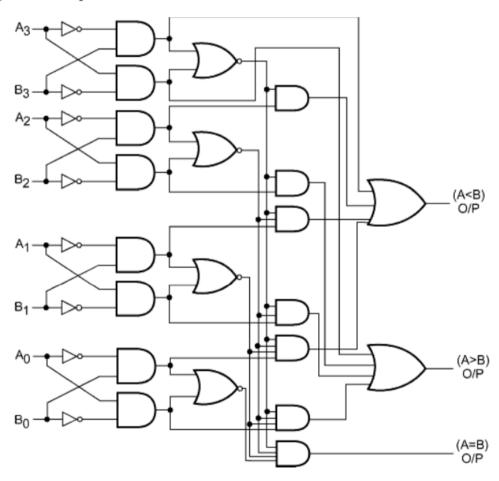

#### 2. Design a 2-bit magnitude comparator (May 2016)

**Magnitude Comparator:** A magnitude comparator is a combinational circuit that compares two given numbers (A and B) and determines whether one is equal to, less than or greater than the other. The output is in the form of three binary variables representing the conditions A = B, A>B and A<B, if A and B are the two numbers being compared.

For comparison of two n-bit numbers, the classical method to achieve the Boolean expressions requires a truth table of  $2^{2n}$  entries and becomes too lengthy and cumbersome.

#### 2- Bit Magnitude Comparator:

The truth table of 2-bit comparator is given in table below:

| Co    | ontrol |            | ıp)            |           | put signa |                      |

|-------|--------|------------|----------------|-----------|-----------|----------------------|

|       | sig    |            |                |           | ferent po |                      |

| $A_1$ | $A_0$  | <b>B</b> 1 | B <sub>0</sub> | Port Port |           | Port                 |

|       |        |            |                | Y1        | Y2        | Y3                   |

|       |        |            |                | (A=B)     | (A>B)     | (A <b)< th=""></b)<> |

| 0     | 0      | 0          | 0              | 1         | 0         | 0                    |

| 0     | 0      | 0          | 1              | 0         | 0         | 1                    |

| 0     | 0      | 1          | 0              | 0         | 0         | 1                    |

| 0     | 0      | 1          | 1              | 0         | 0         | 1                    |

| 0     | 1      | 0          | 0              | 0         | 1         | 0                    |

| 0     | 1      | 0          | 1              | 1         | 0         | 0                    |

| 0     | 1      | 1          | 0              | 0         | 0         | 1                    |

| 0     | 1      | 1          | 1              | 0         | 0         | 1                    |

| 1     | 0      | 0          | 0              | 0         | 1         | 0                    |

| 1     | 0      | 0          | 1              | 0         | 1         | 0                    |

| 1     | 0      | 1          | 0              | 1         | 0         | 0                    |

| 1     | 0      | 1          | 1              | 0         | 0         | 1                    |

| 1     | 1      | 0          | 0              | 0         | 1         | 0                    |

| 1     | 1      | 0          | 1              | 0         | 1         | 0                    |

| 1     | 1      | 1          | 0              | 0         | 1         | 0                    |

| 1     | 1      | 1          | 1              | 1         | 0         | 0                    |

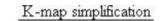

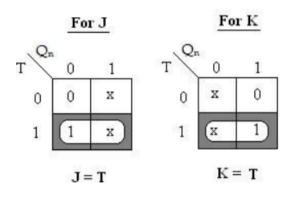

#### **K-MAP SIMPLIFICATION**

$A > B = A_0 B_1' B_0' + A_1 B_1' + A_1 A_0 B_0'$

$\begin{array}{l} \mathbf{A} = \mathbf{B} = \mathbf{A}_{1}'\mathbf{A}_{0}'\mathbf{B}_{1}'\mathbf{B}_{0}' + \mathbf{A}_{1}'\mathbf{A}_{0}\mathbf{B}_{1}'\mathbf{B}_{0} + \\ \mathbf{A}_{1}\mathbf{A}_{0}\mathbf{B}_{1}\mathbf{B}_{0} + \mathbf{A}_{1}\mathbf{A}_{0}'\mathbf{B}_{1}\mathbf{B}_{0}' \\ = \mathbf{A}_{1}'\mathbf{B}_{1}'\left(\mathbf{A}_{0}'\mathbf{B}_{0}' + \mathbf{A}_{0}\mathbf{B}_{0}\right) + \mathbf{A}_{1}\mathbf{B}_{1}\left(\mathbf{A}_{0}\mathbf{B}_{0} + \mathbf{A}_{0}'\mathbf{B}_{0}'\right) \\ = \left(\mathbf{A}_{0}\odot\mathbf{B}_{0}\right)\left(\mathbf{A}_{1}\odot\mathbf{B}_{1}\right) \end{array}$

#### LOGIC DIAGRAM:

#### EXAMPLE INPUTS

| Ing      | outs     | Outputs                                      |     |     |  |  |

|----------|----------|----------------------------------------------|-----|-----|--|--|

| A        | В        | A <b< td=""><td>A=B</td><td>A&gt;B</td></b<> | A=B | A>B |  |  |

| 00001100 | 00001100 | 0                                            | 1   | 0   |  |  |

| 00001010 | 00010001 | 1                                            | 0   | 0   |  |  |

| 00001111 | 00000101 | 0                                            | 0   | 1   |  |  |

| 00011000 | 00011000 | 0                                            | 1   | 0   |  |  |

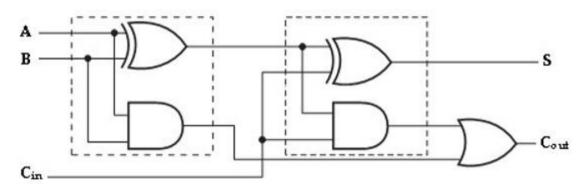

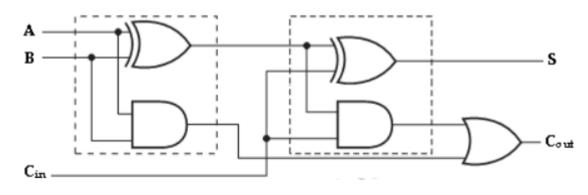

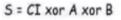

#### 3. Design a full adder and a half subtractor (Nov. 2016)

#### Full Adder:

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of 3 inputs and 2 outputs. Two of the input variables, represent the significant bits to be added. The third input represents the carry from previous lower significant position. The block diagram of full adder is given by,

The full adder circuit overcomes the limitation of the half-adder, which can be used to add two bits only. As there are three input variables, eight different input combinations are possible.

#### **Truth Table:**

|   | Inputs | Outputs |     |       |

|---|--------|---------|-----|-------|

| Α | В      | Cin     | Sum | Carry |

| 0 | 0      | 0       | 0   | 0     |

| 0 | 0      | 1       | 1   | 0     |

| 0 | 1      | 0       | 1   | 0     |

| 0 | 1      | 1       | 0   | 1     |

| 1 | 0      | 0       | 1   | 0     |

| 1 | 0      | 1       | 0   | 1     |

| 1 | 1      | 0       | 0   | 1     |

| 1 | 1      | 1       | 1   | 1     |

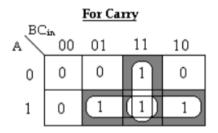

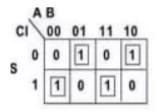

To derive the simplified Boolean expression from the truth table, the Karnaugh map method is adopted as,

$Carry, C_{out} = AB + AC_{in} + BC_{in}$

Sum,  $S = A'B'C_{in} + A'BC'_{in} + AB'C'_{in} + ABC_{in}$

The Boolean expressions for the SUM and CARRY outputs are given by the equations,

**Sum**,  $S = A'B'C_{in} + A'BC'_{in} + AB'C'_{in} + ABC_{in}$

Carry,  $C_{out} = AB + AC_{in} + BCi_{n.}$

The logic diagram for the above functions is shown as,

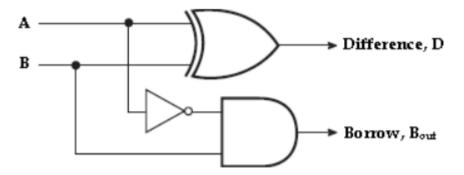

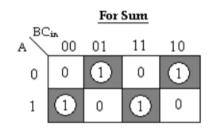

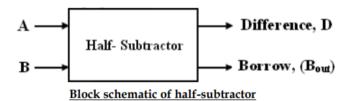

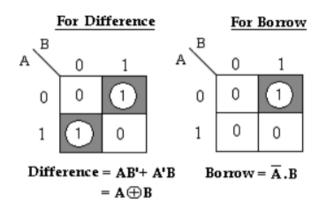

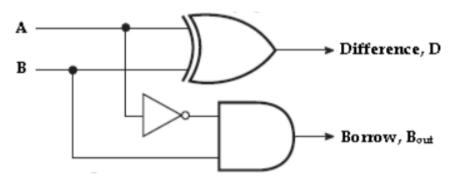

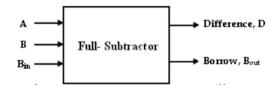

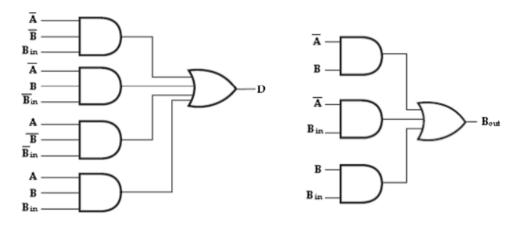

#### Half Subtractor:

A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a DIFFERENCE output and a BORROW output. The BORROW output here specifies whether a \_1' has be en borrowed to perform the subtraction.

The truth table of half-subtractor, showing all possible input combinations and the corresponding outputs are shown below.

| In | put | Output         |               |  |  |  |  |

|----|-----|----------------|---------------|--|--|--|--|

| Α  | В   | Difference (D) | Borrow (Bout) |  |  |  |  |

| 0  | 0   | 0              | 0             |  |  |  |  |

| 0  | 1   | 1              | 1             |  |  |  |  |

| 1  | 0   | 1              | 0             |  |  |  |  |

| 1  | 1   | 0              | 0             |  |  |  |  |

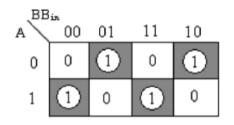

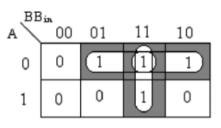

#### K-map Simplification:

The Boolean expressions for the DIFFERENCE and BORROW outputs are given by the equations,

Difference,  $D = A'B + AB' = A \oplus B$

Borrow, Bout = A'. B

The first one representing the DIFFERENCE (D)output is that of an exclusive-OR gate, the expression for the BORROW output (Bout) is that of an AND gate with input A complemented before it is fed to the gate.

#### Logic Diagram:

Comparing a half-subtractor with a half-adder, we find that the expressions for the SUM and DIFFERENCE outputs are just the same. The expression for BORROW in the case of the half-subtractor is also similar to what we have for CARRY in the case of the half-adder. If the input A, ie., the minuend is complemented, an AND gate can be used to implement the BORROW output.

#### 4. Explain the working principle of following combinational circuits(May 2017)

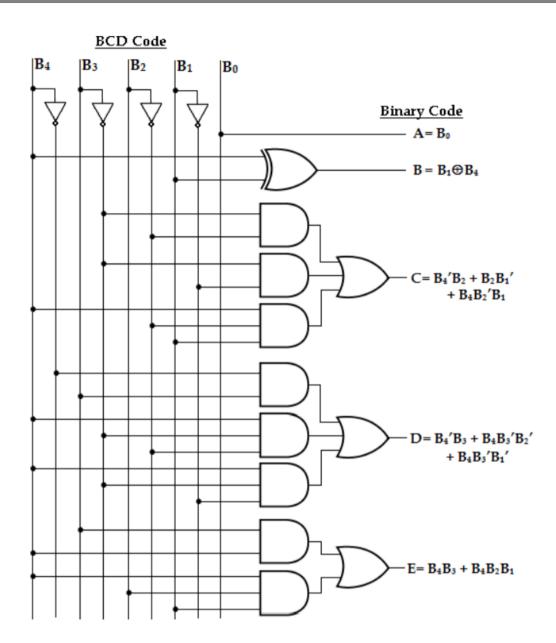

#### a) BCD to binary converter

The steps involved in the BCD-to-binary conversion process are as follows:

1. The value of each bit in the BCD number is represented by a binary equivalent or weight.

2. All the binary weights of the bits that are 1's in the BCD are added.

3. The result of this addition is the binary equivalent of the BCD number.

Two-digit decimal values ranging from 00 to 99 can be represented in BCD by two 4bit code groups. For example, 1910 is represented as,

The left-most four-bit group represents 10 and right-most four-bit group represents 9. The binary representation for decimal 19 is  $19_{10} = 1100_{12}$ .

|                       | B                     | CD Cod                | le                    |                | Binary |   |   |   |   |  |

|-----------------------|-----------------------|-----------------------|-----------------------|----------------|--------|---|---|---|---|--|

| <b>B</b> <sub>4</sub> | <b>B</b> <sub>3</sub> | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | B <sub>0</sub> | E      | D | C | B | Α |  |

| 0                     | 0                     | 0                     | 0                     | 0              | 0      | 0 | 0 | 0 | 0 |  |

| 0                     | 0                     | 0                     | 0                     | 1              | 0      | 0 | 0 | 0 | 1 |  |

| 0                     | 0                     | 0                     | 1                     | 0              | 0      | 0 | 0 | 1 | 0 |  |

| 0                     | 0                     | 0                     | 1                     | 1              | 0      | 0 | 0 | 1 | 1 |  |

| 0                     | 0                     | 1                     | 0                     | 0              | 0      | 0 | 1 | 0 | 0 |  |

| 0                     | 0                     | 1                     | 0                     | 1              | 0      | 0 | 1 | 0 | 1 |  |

| 0                     | 0                     | 1                     | 1                     | 0              | 0      | 0 | 1 | 1 | 0 |  |

| 0                     | 0                     | 1                     | 1                     | 1              | 0      | 0 | 1 | 1 | 1 |  |

| 0                     | 1                     | 0                     | 0                     | 0              | 0      | 1 | 0 | 0 | 0 |  |

| 0                     | 1                     | 0                     | 0                     | 1              | 0      | 1 | 0 | 0 | 1 |  |

| 1                     | 0                     | 0                     | 0                     | 0              | 0      | 1 | 0 | 1 | 0 |  |

| 1                     | 0                     | 0                     | 0                     | 1              | 0      | 1 | 0 | 1 | 1 |  |

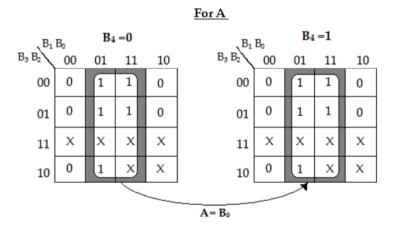

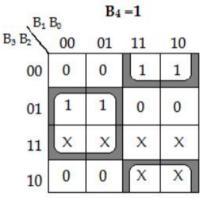

K-map simplification:

$C = B_4'B_2 + B_2B_1' + B_4B_2'B_1$ <u>For D</u>

$D = B_4'B_3 + B_4B_3'B_2' + B_4B_3'B_1'$

$E = B_4 B_3 + B_4 B_2 B_1$

From the above K-map,

$A = B_0$

- $B = B_1 B_4' + B_1' B_4$  $= B_1 \oplus B_4$

- $C = B_4'B_2 + B_2B_1' + B_4B_2'B_1$

- $D = B_4'B_3 + B_4B_3'B_2' + B_4B_3'B_1'$

$\mathbf{E} = \mathbf{B}_4 \mathbf{B}_3 + \mathbf{B}_4 \mathbf{B}_2 \mathbf{B}_1$

Logic Diagram:

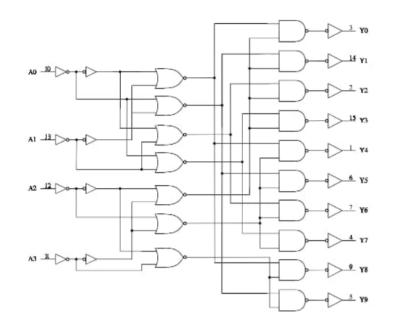

## **5.**With necessary diagram explain the working principle of the following comninational circuits

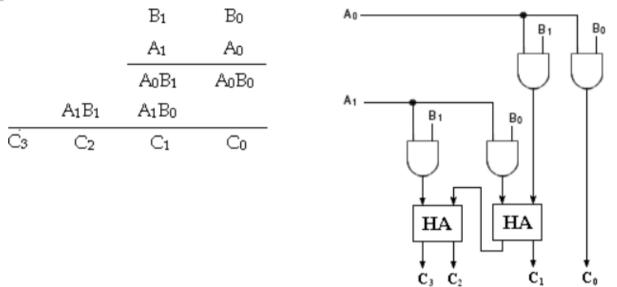

#### a) Binary multiplier using shift method(May 2017)

Multiplication of binary numbers is performed in the same way as in decimal numbers. The multiplicand is multiplied by each bit of the multiplier starting from the least significant bit. Each such multiplication forms a partial product. Such partial products are shifted one position to the left. The final product is obtained from the sum of partial products.

Consider the multiplication of two 2-bit numbers. The multiplicand bits are B1 and B0, the multiplier bits are A1 and A0, and the product is C3, C2, C1 and C0. The first partial product is formed by multiplying A0 by B1B0. The multiplication of two bits such as A0 and

B0 produces a 1 if both bits are 1; otherwise, it produces a 0. This is identical to an AND operation. Therefore, the partial product can be implemented with AND gates as shown in the diagram below.

The second partial product is formed by multiplying A1 by B1B0 and shifted one position to the left. The two partial products are added with two half adder (HA) circuits.

Usually there are more bits in the partial products and it is necessary to use full adders to produce the sum of the partial products. The least significant bit of the product does not have to go through an adder since it is formed by the output of the first AND gate.

A combinational circuit binary multiplier with more bits can be constructed in a similar fashion. A bit of the multiplier is ANDed with each bit of the multiplicand in as many levels as there are bits in the multiplier.

The binary output in each level of AND gates are added with the partial product of the

previous level to form a new partial product. The last level produces the product. For J multiplier bits and K multiplicand bits we need  $(J \times K)$  AND gates and (J-1) k-bit adders to produce a product of J+K bits.

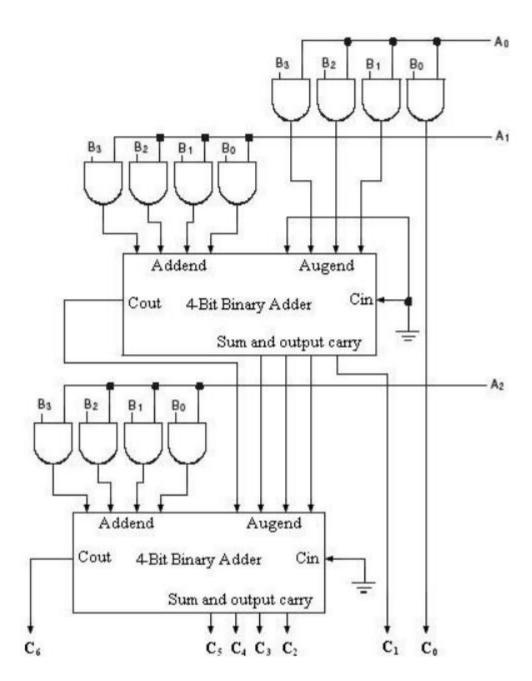

Consider a multiplier circuit that multiplies a binary number of four bits by a number of three bits. Let the multiplicand be represented by B3, B2, B1, B0 and the multiplier by A2, A1, and A0. Since K= 4 and J= 3, we need 12 AND gates and two 4-bit adders to produce a product of seven bits. The logic diagram of the multiplier is shown below.

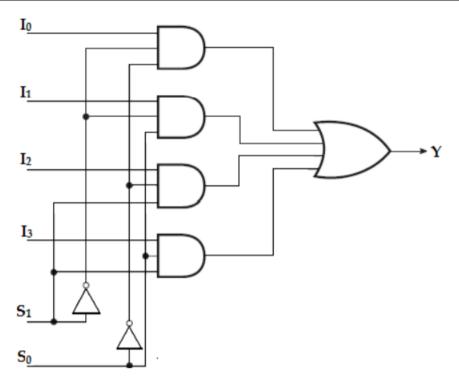

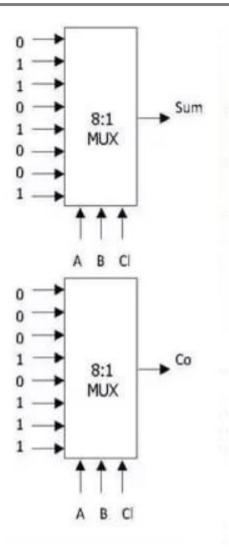

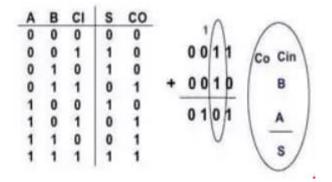

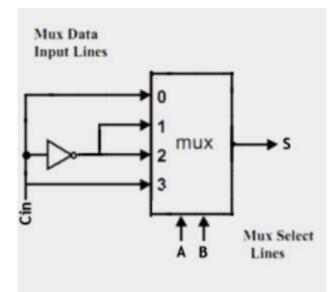

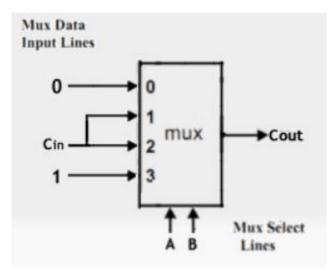

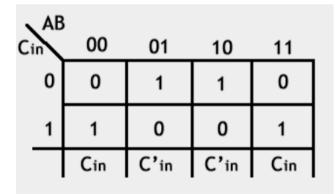

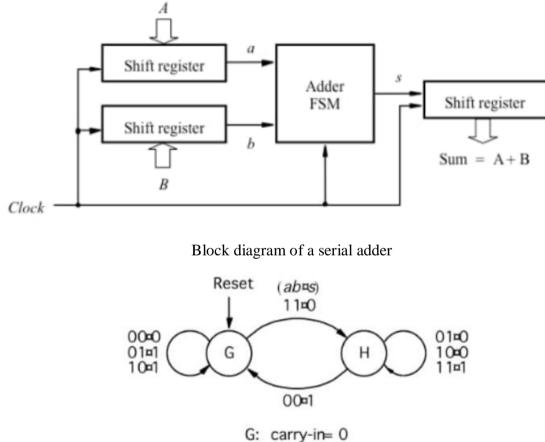

#### 5. b) 4 to 1 multiplexer

A 4-to-1-line multiplexer has four (2n) input lines, two (n) select lines and one output line. It is the multiplexer consisting of four input channels and information of one of the channels can be selected and transmitted to an output line according to the select inputs combinations.

Selection of one of the four input channel is possible by two selection inputs. Each of the four inputs I0 through I3, is applied to one input of AND gate. Selection lines S1 and S0 are decoded to select a particular AND gate. The outputs of the AND gate are applied to a single OR gate that provides the 1-line output.

#### **Function table:**

| S <sub>1</sub> | S <sub>0</sub> | Y              |

|----------------|----------------|----------------|

| 0              | 0              | I <sub>0</sub> |

| 0              | 1              | I1             |

| 1              | 0              | I <sub>2</sub> |

| 1              | 1              | $I_3$          |

To demonstrate the circuit operation, consider the case when S1S0=10. The AND gate associated with input I2 has two of its inputs equal to 1 and the third input connected to I2. The other three AND gates have atleast one input equal to 0, which makes their outputs equal to 0. The OR output is now equal to the value of I2, providing a path from the selected input to the output.

The data output is equal to I0 only if S1=0 and S0=0; Y=I0S1 'S0'.

The data output is equal to I1 only if S1=0 and S0=1; Y=I1S1'SO.

The data output is equal to I2 only if S1=1 and S0=0;  $Y=I2S1S0^{\circ}$ .

The data output is equal to I3 only if S1=1 and S0=1; Y=I3S1S0.

When these terms are ORed, the total expression for the data output is,

Y= I0S1'S0'+ I1S1'S0 +I2S1S0'+ I3S1S0.

As in decoder, multiplexers may have an enable input to control the operation of the unit. When the enable input is in the inactive state, the outputs are disabled, and when it is in the active state, the circuit functions as a normal multiplexer.

#### 6. Design the following circuit (Nov. 2017)

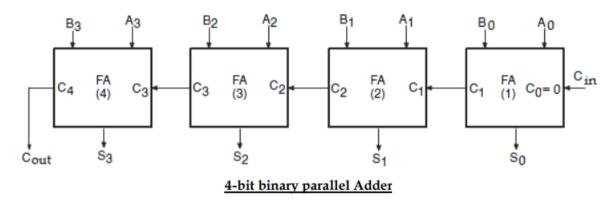

#### a) 4-bit parallel adder

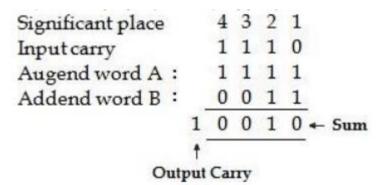

The 4-bit binary adder using full adder circuits is capable of adding two 4-bit numbers resulting in a 4-bit sum and a carry output as shown in figure below.

Since all the bits of augend and addend are fed into the adder circuits simultaneously and the additions in each position are taking place at the same time, this circuit is known as parallel adder.

Let the 4-bit words to be added be represented by, A3A2A1A0= 1111 and B3B2B1B0= 0011.

The bits are added with full adders, starting from the least significant position, to form the sum it and carry bit. The input carry C0 in the least significant position must be 0. The carry output of the lower order stage is connected to the carry input of the next higher order stage. Hence this type of adder is called ripple-carry adder.

In the least significant stage, A0, B0 and C0 (which is 0) are added resulting in sum S0 and carry C1. This carry C1 becomes the carry input to the second stage. Similarly, in the second stage, A1, B1 and C1 are added resulting in sum S1 and carry C2, in the third stage, A2, B2 and C2 are added resulting in sum S2 and carry C3, in the third stage, A3, B3 and C3

are added resulting in sum S3 and C4, which is the output carry. Thus, the circuit results in a sum (S3S2S1S0) and a carry output (Cout).

Though the parallel binary adder is said to generate its output immediately after the inputs are applied, its speed of operation is limited by the carry propagation delay through all stages. However, there are several methods to reduce this delay. One of the methods of speeding up this process is look-ahead carry addition which eliminates the ripple-carry delay.

#### 6. b) binary to octal decoder (Nov. 2017)

A 3-to-8 line decoder has three inputs (A, B, C) and eight outputs (Y0- Y7). Based on the 3 inputs one of the eight outputs is selected. The three inputs are decoded into eight outputs, each output representing one of the minterms of the 3-input variables. This decoder is used for binary-to-octal conversion.

The input variables may represent a binary number and the outputs will represent the eight digits in the octal number system. The output variables are mutually exclusive because only one output can be equal to 1 at any one time. The output line whose value is equal to 1 represents the minterm equivalent of the binary number presently available in the input lines.

|   | Inputs |   | Outputs        |            |                |            |            |            |            |                       |

|---|--------|---|----------------|------------|----------------|------------|------------|------------|------------|-----------------------|

| Α | В      | С | Y <sub>0</sub> | <b>Y</b> 1 | Y <sub>2</sub> | <b>Y</b> 3 | <b>Y</b> 4 | <b>Y</b> 5 | <b>Y</b> 6 | <b>Y</b> <sub>7</sub> |

| 0 | 0      | 0 | 1              | 0          | 0              | 0          | 0          | 0          | 0          | 0                     |

| 0 | 0      | 1 | 0              | 1          | 0              | 0          | 0          | 0          | 0          | 0                     |

| 0 | 1      | 0 | 0              | 0          | 1              | 0          | 0          | 0          | 0          | 0                     |

| 0 | 1      | 1 | 0              | 0          | 0              | 1          | 0          | 0          | 0          | 0                     |

| 1 | 0      | 0 | 0              | 0          | 0              | 0          | 1          | 0          | 0          | 0                     |

| 1 | 0      | 1 | 0              | 0          | 0              | 0          | 0          | 1          | 0          | 0                     |

| 1 | 1      | 0 | 0              | 0          | 0              | 0          | 0          | 0          | 1          | 0                     |

| 1 | 1      | 1 | 0              | 0          | 0              | 0          | 0          | 0          | 0          | 1                     |

## 7. Develop a code converter circuit that converts four-bit data into gray code (Nov. 2017)

The truth table for bcd to gray code converter is,

| I                     | BCD Coo               | de (8421   | )              | Gray code |                |    |                |  |  |

|-----------------------|-----------------------|------------|----------------|-----------|----------------|----|----------------|--|--|

| <b>B</b> <sub>3</sub> | <b>B</b> <sub>2</sub> | <b>B</b> 1 | B <sub>0</sub> | G3        | G <sub>2</sub> | G1 | G <sub>0</sub> |  |  |

| 0                     | 0                     | 0          | 0              | 0         | 0              | 0  | 0              |  |  |

| 0                     | 0                     | 0          | 1              | 0         | 0              | 0  | 1              |  |  |

| 0                     | 0                     | 1          | 0              | 0         | 0              | 1  | 1              |  |  |

| 0                     | 0                     | 1          | 1              | 0         | 0              | 1  | 0              |  |  |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

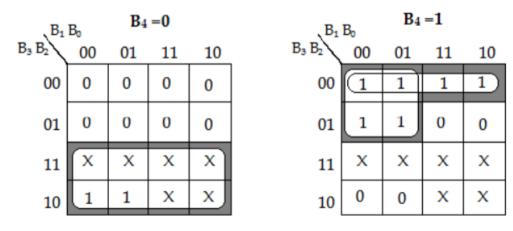

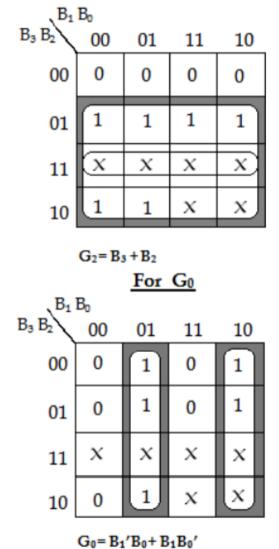

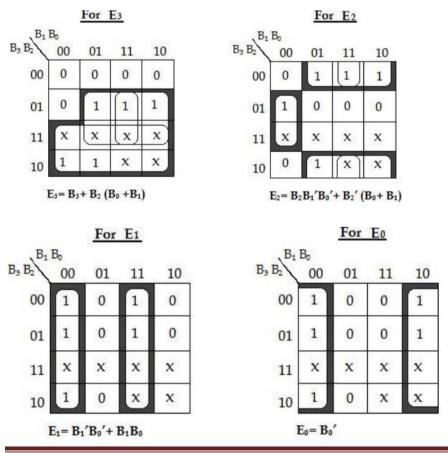

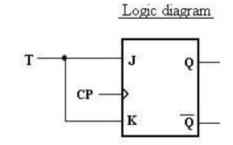

K-map simplification:

For G<sub>3</sub>

For G<sub>2</sub>

#### Logic diagram:

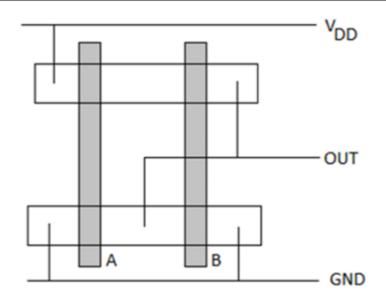

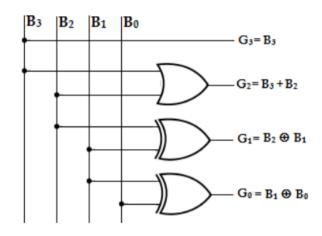

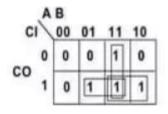

#### 8. Draw the circuit of a BCD adder and explain it. (May 2018)

(or)

#### Design a 4-bit decimal adder using a 4-bit binary adder (Nov. 2019)

The digital system handles the decimal number in the form of binary coded decimal numbers (BCD). A BCD adder is a circuit that adds two BCD bits and produces a sum digit also in BCD.

Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 9+9+1 = 19; the 1 is the sum being an input carry. The adder will form the sum in binary and produce a result that ranges from 0 through 19.

These binary numbers are labeled by symbols K, Z8, Z4, Z2, Z1, K is the carry. The columns under the binary sum list the binary values that appear in the outputs of the 4- bit binary adder. The output sum of the two decimal digits must be represented in BCD.

| ] | Bina | ary S                 | bum          |   |   | BC         | DS                    | um           |   | Decimal |

|---|------|-----------------------|--------------|---|---|------------|-----------------------|--------------|---|---------|

| К | Z8   | <b>Z</b> 4 <b>Z</b> 2 | 2 <b>Z</b> 1 |   | С | <b>S</b> 8 | <b>S</b> 4 <b>S</b> 2 | 2 <b>S</b> 1 |   | Decimai |

| 0 | 0    | 0                     | 0            | 0 | 0 | 0          | 0                     | 0            | 0 | 0       |

| 0 | 0    | 0                     | 0            | 1 | 0 | 0          | 0                     | 0            | 1 | 1       |

| 0 | 0    | 0                     | 1            | 0 | 0 | 0          | 0                     | 1            | 0 | 2       |

| 0 | 0    | 0                     | 1            | 1 | 0 | 0          | 0                     | 1            | 1 | 3       |

| 0 | 0    | 1                     | 0            | 0 | 0 | 0          | 1                     | 0            | 0 | 4       |

| 0 | 0    | 1                     | 0            | 1 | 0 | 0          | 1                     | 0            | 1 | 5       |

| 0 | 0    | 1                     | 1            | 0 | 0 | 0          | 1                     | 1            | 0 | 6       |

| 0 | 0    | 1                     | 1            | 1 | 0 | 0          | 1                     | 1            | 1 | 7       |

| 0 | 1    | 0                     | 0            | 0 | 0 | 1          | 0                     | 0            | 0 | 8       |

| 0 | 1    | 0                     | 0            | 1 | 0 | 1          | 0                     | 0            | 1 | 9       |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 10 |

|---|---|---|---|---|---|---|---|---|---|----|

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 11 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 12 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 13 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 14 |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 15 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 16 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 17 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 18 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 19 |

In examining the contents of the table, it is apparent that when the binary sum is equal to or less than 1001, the corresponding BCD number is identical, and therefore no conversion is needed. When the binary sum is greater than 9 (1001), we obtain a nonvalid BCD representation. The addition of binary 6 (0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required.

The logic circuit to detect sum greater than 9 can be determined by simplifying the boolean expression of the given truth table.

|            | Inj                   | Output |                |   |

|------------|-----------------------|--------|----------------|---|

| <b>S</b> 3 | <b>S</b> <sub>2</sub> | $S_1$  | S <sub>0</sub> | Ŷ |

| 0          | 0                     | 0      | 0              | 0 |

| 0          | 0                     | 0      | 1              | 0 |

| 0          | 0                     | 1      | 0              | 0 |

| 0          | 0                     | 1      | 1              | 0 |

| 0          | 1                     | 0      | 0              | 0 |

| 0          | 1                     | 0      | 1              | 0 |

| 0          | 1                     | 1      | 0              | 0 |

| 0          | 1                     | 1      | 1              | 0 |

| 1          | 0                     | 0      | 0              | 0 |

| 1          | 0                     | 0      | 1              | 0 |

| 1          | 0                     | 1      | 0              | 1 |

| 1          | 0                     | 1      | 1              | 1 |

| 1          | 1                     | 0      | 0              | 1 |

| 1          | 1                     | 0      | 1              | 1 |

| 1          | 1                     | 1      | 0              | 1 |

| 1          | 1                     | 1      | 1              | 1 |

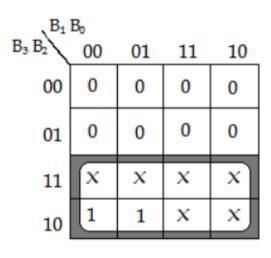

| <b>S</b> 1 | S <sub>0</sub> |    |    |    |  |

|------------|----------------|----|----|----|--|

| S3 S2 S1   | 00             | 01 | 11 | 10 |  |

| 00         | 0              | 0  | 0  | 0  |  |

| 01         | 0              | 0  | 0  |    |  |

| 11         | 1              | 1  | 1  | 1  |  |

| 10         | 0              | 0  | 1  | 1  |  |

|            |                |    |    |    |  |

$Y = S_3S_2 + S_3S_1$

To implement BCD adder we require:

- 4-bit binary adder for initial addition

- Logic circuit to detect sum greater than 9 and

- One more 4-bit adder to add 01102 in the sum if the sum is greater than 9 or carry is 1.

The two decimal digits, together with the input carry, are first added in the top4- bit binary adder to provide the binary sum. When the output carry is equal to zero, nothing is added to the binary sum. When it is equal to one, binary 0110 is added to the binary sum through the bottom 4-bit adder. The output carry generated from the bottom adder can be ignored, since it supplies information already available at the output carry terminal. The output carry from one stage must be connected to the input carry of the next higher-order stage.

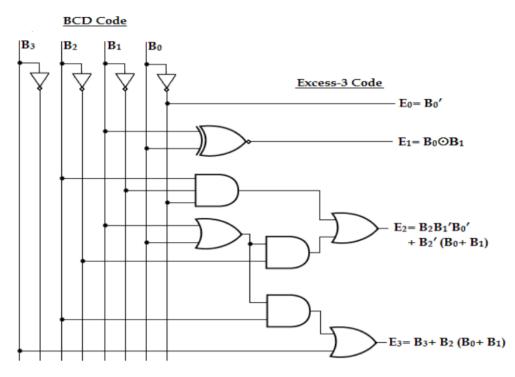

#### 9. Design a BCD to Excess 3 code converter (May 2018)

#### (or)

## Illustrate BCD to Excess code converter using minimum number of NAND gates. (May 2019, Nov. 2019)

Excess-3 is a modified form of a BCD number. The excess-3 code can be derived from the natural BCD code by adding 3 to each coded number. For example, decimal 12 can be represented in BCD as 0001 0010. Now adding 3 to each digit we get excess-3 code as 0100 0101 (12 in decimal). With this information the truth table for BCD to Excess-3 code converter can be determined as,

| BCD no  | EXCESS-3 NO |

|---------|-------------|

| ABCD    | WXYZ        |

| 0000    | 0011        |

| 0 0 0 1 | 0100        |

| 0010    | 0101        |

| 0011    | 0110        |

| 0100    | 0111        |

| 0101    | 1000        |

| 0110    | 1001        |

| 0111    | 1010        |

| 1000    | 1011        |

| 1001    | 1100        |

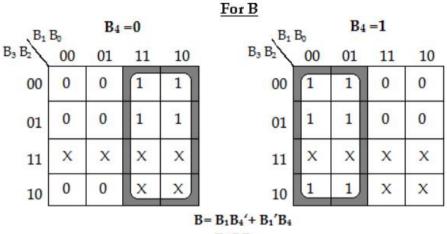

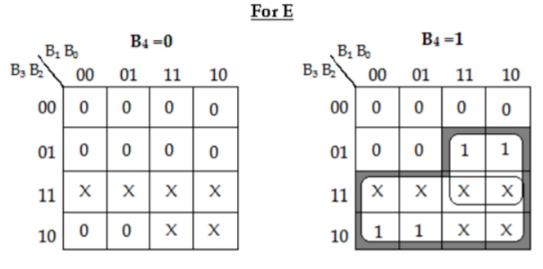

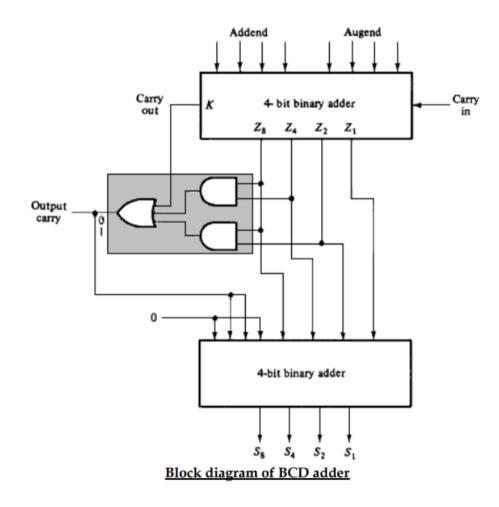

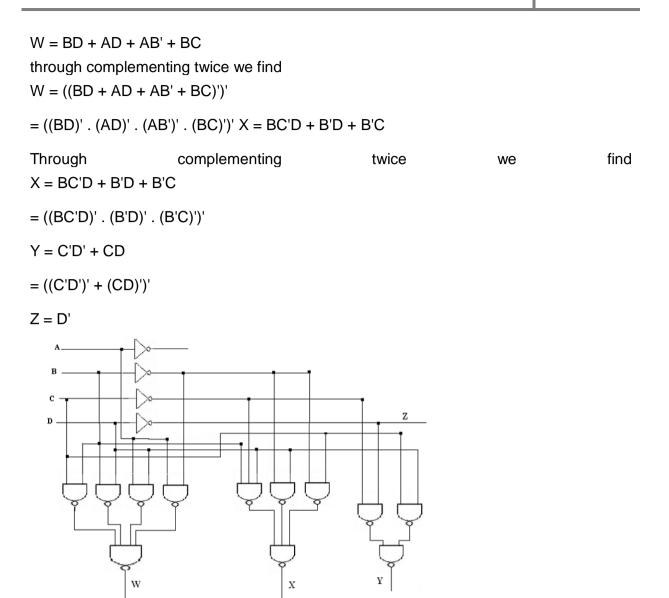

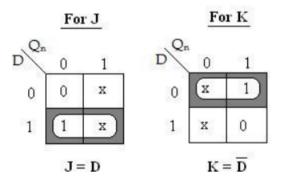

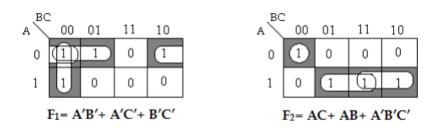

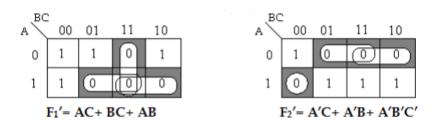

After that by using K maps we can get simplified functions for w, x, y, z shown below as:

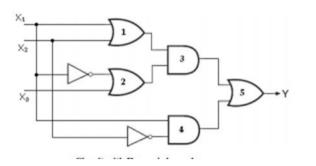

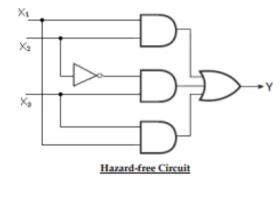

NAND gate implementation for simplified function

Logic diagram for BCD to excess 3 code converter using minimum number of NAND gates

Truth table:

| Decimal | Binay (BCD) | Excess-3 |

|---------|-------------|----------|

|         | 8421        | Code     |

| 0       | 0 0 0 0     | 0011     |

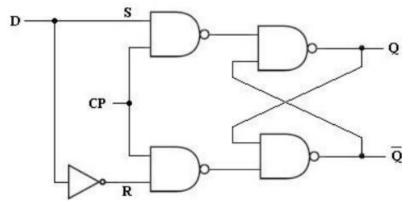

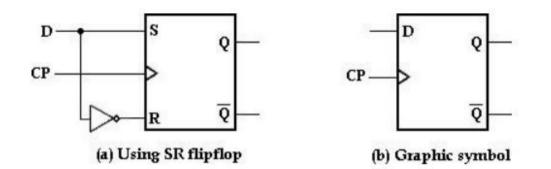

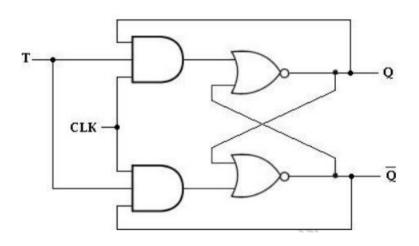

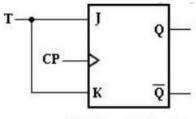

| 1       | 0001        | 0100     |