# DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING

Subject Name: ELECTRONIC DEVICES AND CIRCUITS

# Subject Code: EE T34

# UNIT –I SEMICONDUCTOR THEORY AND PN DIODES

Introduction to Semiconductor materials-atomic theory-energy band structure of insulators, conductors and semiconductors-intrinsic and extrinsic semiconductors-N-type and P-type semiconductors.

# SEMICONDUCTOR DIODES:

Construction – forward and reverse bias operation – mathematical model of a PN diode–Silicon versus Germanium diodes – Effects of temperature on diode operation– Static and dynamic resistances–Diode equivalent models– Specification sheets–Transition and diffusion capacitances– Diode switching-reverse recovery time–Diode applications.

# (11 MARKS)

# 1. Explain the behavior of insulators, conductors and semiconductors by drawing the energy band structure. [Nov/Dec 2014] [Nov 2013]

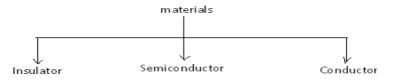

Based on the electrical conductivity all the materials in nature are classified as insulators, semiconductors, and conductors.

#### **Insulator**:

- An insulator is a material that offers a very low level (or negligible) of conductivity when voltage is applied. Eg: Paper, Mica, glass, quartz.

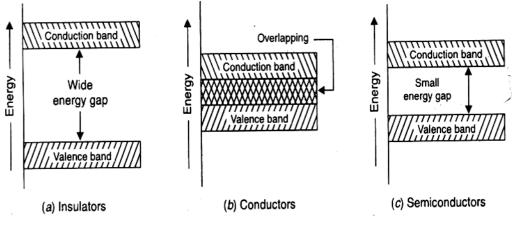

- The energy band structure of an insulator is shown in the fig.1.1. Band structure of a material defines the band of energy levels that an electron can occupy. Valance band is the range of electron energy where the electron remains bonded to the atom and do not contribute to the electric current.

- Conduction band is the range of electron energies higher than valance band where electrons are free to accelerate under the influence of external voltage source resulting in the flow of charge.

- The energy band between the valance band and conduction band is called as forbidden band gap. It is the energy required by an electron to move from balance band to conduction band i.e. the energy required for a valance electron to become a free electron.

1

$$eV = 1.6 \times 10^{-19} J$$

- For an insulator, as shown in the fig.1.1 there is a large forbidden band gap of greater than 15ev.

- Because of this large gap there a very few electrons in the CB and hence the Conductivity of insulator is poor.

- > Thus insulators have very high resistivity a room temperature

- > Typical resistivity level of an insulator is of the order of  $10^{10}$  to  $10^{12} \Omega$ -cm.

- However if the temperature is raised ,some of the valence electrons may acquire energy and jump into the conduction band

- > It causes the resistivity of the insulators to decrease.

- > Therefore insulators have negative temperature coefficient of resistance.

#### **Conductors:**

- A conductor is a material which supports a generous flow of charge when a voltage is applied across its terminals. i.e. it has very high conductivity. Eg: Copper, Aluminum, Silver, and Gold.

- > The resistivity of a conductor is in the order of  $10^{-4}$  and  $10^{-6} \Omega$ -cm.

- The Valance and conduction bands overlap (fig1.1) and there is no energy gap for the electrons to move from valance band to conduction band.

- This implies that there are free electrons in Conduction Band even at absolute zero temperature (0K).

- Therefore at room temperature when electric field is applied large current flows through the conductor.

#### Semiconductor:

- A semiconductor is a material that has its conductivity somewhere between the insulator and conductor.

- Two of the most commonly used semiconductors are Silicon (Si=14 atomic no.) and germanium (Ge=32 atomic no.). Both have 4 valance electrons.

- > The resistivity level is in the range of 10 and  $10^4$  Ω-cm.

- The forbidden band gap is in the order of 1eV. For eg,the energy gap for Si, Ge and Ga As is 1.21, 0.785 and 1.42 eV, respectively at absolute zero temperature (0K).

- A small energy gap means that a small amount of energy is required to free the electrons from valence band to conduction band.

- At 0K and at low temperatures, the valance band electrons do not have sufficient energy to move to Conduction Band.

- Thus semiconductors act as insulators at 0K. As the temperature increases, a large number of valance electrons acquire sufficient energy to leave the Valence Band, cross the forbidden energy gap and reach Conduction Band.

- > These are now free electrons as they can move freely under the influence of electric field.

- At room temperature there are sufficient electrons in the Conduction Band and hence the semiconductor is capable of conducting some current at room temperature.

- Semiconductors also have negative temperature coefficient of resistance .It means the conductivity of semiconductor increases with the increase in temperature.

| Insulator                 | Semiconductor                    | Conductor                  |

|---------------------------|----------------------------------|----------------------------|

| $10^{-6} \Omega$ -cm (Cu) | 50Ω-cm (Ge)                      | $10^{12} \Omega\text{-cm}$ |

|                           |                                  | (mica)                     |

|                           | $50 \times 10^3 \Omega$ -cm (Si) |                            |

Typical resistivity values

Semiconductors are classified in to two types

(i) Intrinsic Semiconductors (ii) Exterinsic semi-conductors

a. n-type semi-conductorsb. p-type semi-conductors

#### 2. Explain the operation of N type extrinsic semiconductor.[April 2015]

- Intrinsic semiconductor has very limited applications as they conduct very small amount of current at room temperature. The current conduction capability of intrinsic semiconductor can be increased significantly by adding small amounts of impurity to the intrinsic semiconductor.

- > By adding impurities it becomes impure or extrinsic semiconductor.

- > This process of adding impurities is called as doping.

- > The amount of impurity is added at a rate of only one atom of impurity per  $10^6$  to  $10^{10}$  semiconductor atoms.

- The purpose of adding impurity is to increase either the number of free electrons or holes in semiconductor.

#### N type semiconductor:

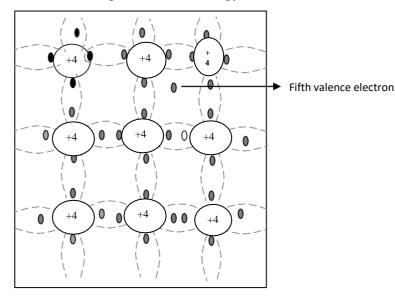

- If the added impurity is a pentavalent atom then the resultant semiconductor is called N-type semiconductor. Examples of pentavalent impurities are Phosphorus, Arsenic, Bismuth, Antimony etc.

- A pentavalent impurity has five valance electrons. Fig 1.2a shows the crystal structure of N-type semiconductor material where four out of five valance electrons of the impurity atom(antimony) forms covalent bond with the four intrinsic semiconductor atoms.

- The fifth electron is loosely bound to the impurity atom. This loosely bound electron can be easily excited from the valance band to the conduction band by the application of electric field or increasing the thermal energy.

Fig. 1.2a Crystal structure of N type Semiconductor

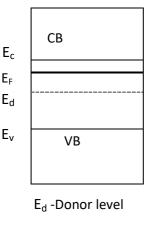

E<sub>F</sub>\_Fermi level

Fig. 1.2bEnergy band diagram of N type

- The energy required to detach the fifth electron form the impurity atom is very small of the order of 0.01ev for Ge and 0.05 eV for Si.

- The effect of doping creates a discrete energy level called donor energy level in the forbidden band gap with energy level E<sub>d</sub> slightly less than the conduction band.

- The difference between the energy levels of the conducting band and the donor energy level is the energy required to free the fifth valence electron (0.01 eV for Ge and 0.05 eV for Si).

- At room temperature almost all the fifth electrons from the donor impurity atom are raised to conduction band and hence the number of electrons in the conduction band increases significantly.

- > Thus every antimony atom contributes to one conduction electron without creating a hole.

- Because of the greater number of electrons in the conduction band than that of holes in the valence band and hence the Fermi level shifts upwards below the conduction band.

- After the donation, the impurity atom becomes a positively charged ion and is known as donor ion.

- > The position of the donor ion is fixed in the crystal lattice and these are known as immobile ions.

- Thus current in N type semiconductor is dominated by electrons which are referred to as majority carriers and holes as minority carriers.

Fig. 1.2c Crystal Structure of N Type Semiconductor

#### 3. Explain the operation of P type extrinsic semiconductor.[April 2015]

- Intrinsic semiconductor has very limited applications as they conduct very small amount of current at room temperature. The current conduction capability of intrinsic semiconductor can be increased significantly by adding a small amounts impurity to the intrinsic semiconductor.

- By adding impurities it becomes impure or extrinsic semiconductor. This process of adding impurities is called as doping.

- > The amount of impurity is added at a rate of only one atom of impurity per  $10^6$  to  $10^{10}$  semiconductor atoms.

The purpose of adding impurity is to increase either the number of free electrons or holes in semiconductor.

#### P type semiconductor:

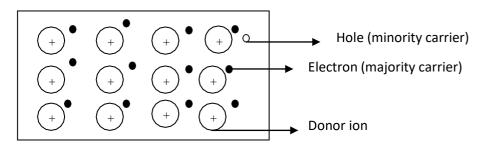

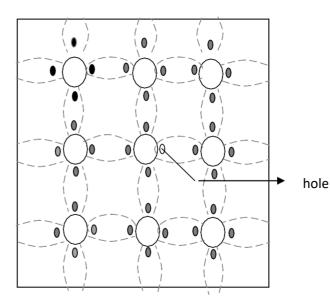

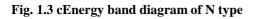

- If the added impurity is a trivalent atom then the resultant semiconductor is called P-type semiconductor. Examples of trivalent impurities are Boron, Gallium, indium, Aluminium.

- The crystal structure of P type semiconductor is shown in the fig1.3a. The three valance electrons of the impurity (boron) forms three covalent bonds with the neighbouring atoms and a vacancy exists in the fourth bond giving rise to the holes.

- > The hole is ready to accept an electron from the neighboring atoms.

- Each trivalent atom contributes to one hole generation and thus introduces a large no. of holes in the valance band.

- At the same time the no. electrons are decreased compared to those available in intrinsic semiconductor because of increased recombination due to creation of additional holes.

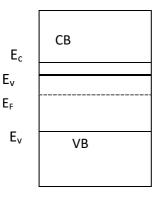

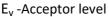

E<sub>F</sub>\_Fermi level

Fig. 1.3b crystal structure of P type semiconductor

- The fifth electron is loosely bound to the impurity atom. This loosely bound electron can be easily excited from the valance band to the conduction band by the application of electric field or increasing the thermal energy.

- The energy required to detach the fifth electron form the impurity atom is very small of the order of 0.01ev for Ge and 0.05 eV for Si.

- > The number of electrons in the conduction band decreases below a level.

- Because of the greater number of holes in the valence band than that of electrons in conduction band, the Fermi level shifts downwards towards top of the valence band.

- > As hole moves away from the parent atom, it acquires a negative charge.

- This negative charged atom is known as acceptor ion. These does not take place in conduction and it becomes an immobile ion.

- > Thus in P type semiconductor, holes are majority carriers and electrons are minority carriers.

- Since each trivalent impurity atoms are capable accepting an electron, these are called as acceptor atoms. The following fig 1.3b shows the pictorial representation of P type semiconductor.

- The conductivity of N type semiconductor is greater than that of P type sc as the mobility of electron is greater than that of hole.

- For the same level of doping in N type semiconductor and P type semiconductor, the conductivity of an N type semiconductor is around twice that of a P type semiconductor.

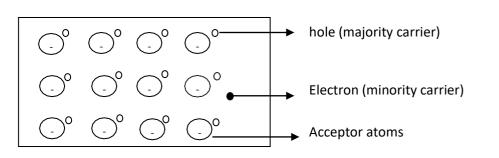

#### 4. Explain the operation of intrinsic semiconductor.

- The materials whose electrical properties lie between those of conductors and insulators are known as semiconductors.

- At absolute zero temperature (i.e) at 0K there are no electrons in the conduction band of semiconductors and valence band is completely filled. Thus the semiconductors behave like perfect insulators at 0K.

- However if the temperature is increased, the width of the energy gap reduces and consequently some of the electrons jump into conduction band.

- > The electrical conductivity of semiconductors lies in the range of  $10^{-3}$  to  $10^{-6}$  per ohm per cm.

- A pure form of semiconductors is called as intrinsic semiconductor. Conduction in intrinsic semiconductor is either due to thermal excitation or crystal defects. Si and Ge are the two most important semiconductors used. Other examples include Gallium arsenide GaAs, Indium Antimonide (InSb) etc.

- > For germanium, the impurity level is less than 1 part in  $10^8$  parts. For silicon it is less than 1 part in  $10^{12}$  parts

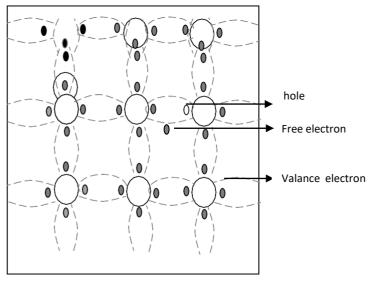

- Let us consider the structure of Si. A Si atomic no. is 14 and it has 4 valance electrons.

- These 4 electrons are shared by four neighboring atoms in the crystal structure by means of covalent bond. Fig. 1.4a shows the crystal structure of Si at absolute zero temperature (0K).

- In that structure all the valence electrons are tightly held by the parent atoms and through covalent bonds by other atoms

- Hence a pure Semiconductor acts has poor conductivity (due to lack of free electrons) at low or absolute zero temperature.

- At room temperature some of the covalent bonds break up to thermal energy as shown in fig 1.4b.

- The valance electrons that jump into conduction band are called as free electrons that are available for conduction.

#### Fig. 1.4b crystal structure of Si at room temperature0K

- The energy required to break the covalent bond is equal to band gap energy. The value of E<sub>G</sub> is 1.1 eV and 0.72 eV for germanium.

- $\succ$  The vacancy of an incomplete covalent bond left behind the dislodged electron is hole. The absence of electrons in covalent bond is represented by a small circle usually referred to as hole which is of positive charge.

- Even a hole serves as carrier of electricity in a manner similar to that of free electron.

- > The combination of such a free electron and a hole is called electron hole pair.

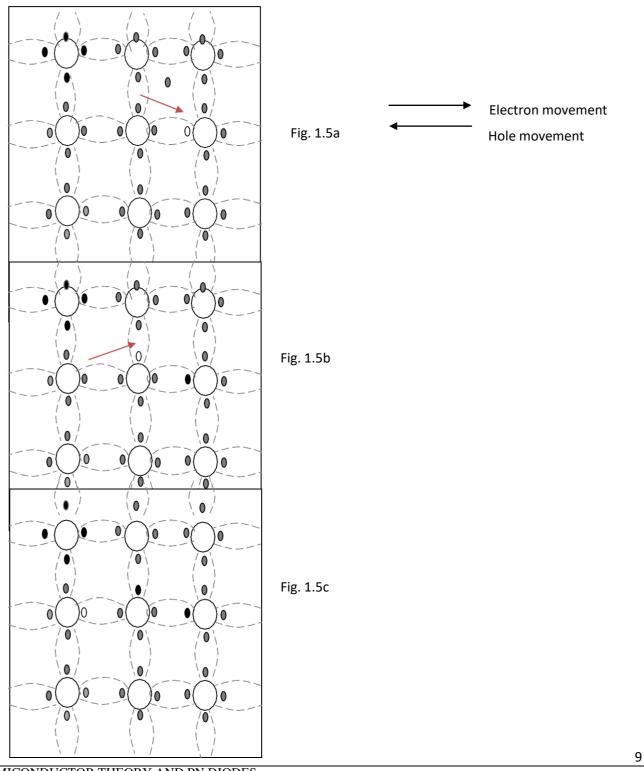

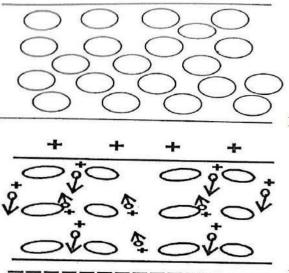

The mechanism by which a hole contributes to conductivity is explained as follows:

➤ When a bond is in complete so that a hole exists, it is relatively easy for a valance electron in the neighboring atom to leave its covalent bond to fill this hole. An electron moving from a bond to fill a hole moves in a direction opposite to that of the electron.

➤ This hole, in its new position may now be filled by an electron from another covalent bond and the hole will correspondingly move one more step in the direction opposite to the motion of electron.

Here we have a mechanism for conduction of electricity which does not involve free electrons. This phenomenon is illustrated in fig1.5

- Fig 1.5a show that there is a hole at ion 6.Imagine that an electron from ion 5 moves into the hole at ion 6 so that the configuration of 1.5b results.

- If we compare both fig1.5a &fig 1.5b, it appears as if the hole has moved towards the left from ion6 to ion 5.

- Further if we compare fig 1.5b and fig 1.5c, the hole moves from ion5 to ion 4. This discussion indicates the motion of hole is in a direction opposite to that of motion of electron.

- > Hence we consider holes as physical entities whose movement constitutes flow of current.

- > In a pure semiconductor, the number of holes is equal to the number of free electrons.

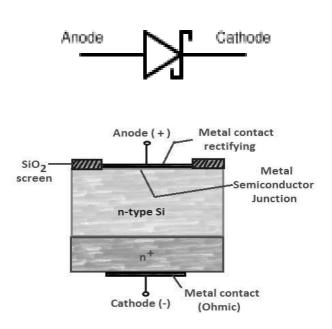

- 5. Explain the construction and working of PN diode with a neat sketch. [Nov/Dec 2014] [April 2015]

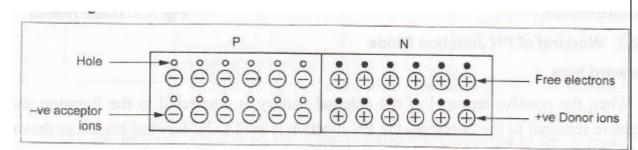

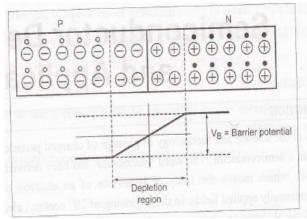

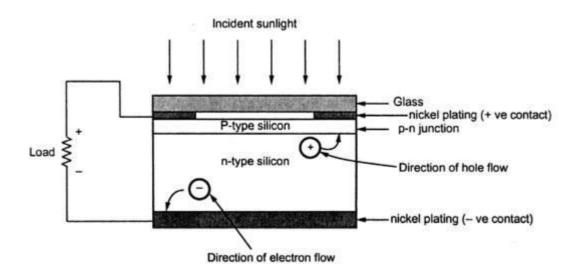

- A PN junction is formed from a piece of semiconductor (Ge or Si) by diffusing p-type material (Acceptor impurity Atoms) to one half side and N type material to (Donar Impurity Atoms) other half side. The plane dividing the two zones is known as 'Junction'.

- > The p region is called the anode and n region is called the cathode.

- The P-region of the semiconductor contains a large number of holes and N region, contains a large number of electrons. A PN junction just immediately formed is shown in Fig.

- When PN junction is formed, there is a tendency for the electrons in the N-region to diffuse into the p-region, and holes from P-region to N-region. This process is called diffusion.

- While crossing the junction, the electrons and holes recombines with each other, leaving the immobile ions in the neighbourhood of the junction unneutralized as shown in Fig.

These immobile + ve and -ve ions, set up a potential across the junction. This potential is called potential barrier or junction barrier.

- Due to the potential barrier no further diffusion of electrons and holes takes place across the junction.

- Potential barrier is defined as a potential difference built up across the PN junction which restricts further movement of charge carriers across the junction.

- The potential barrier for a silicon PN junction is about 0.7 volt, whereas for Germanium PN junction is approximately 0.3 volt.

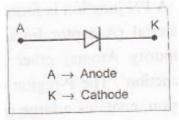

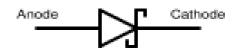

# **Symbol of Diode:**

The symbol of PN junction diode is shown in Fig .The P-type and N-type regions are referred to as Anode and Cathode respectively. The arrowhead shows the conventional direction of current flow when the diode is forward biased.

#### **Working of PN Junction Diode:**

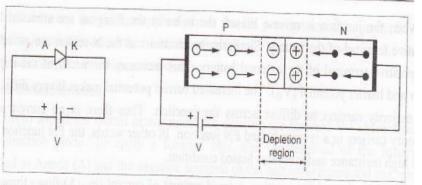

#### **Forward Bias:**

When the positive terminal of the external battery is connected to the P-region and negative terminal to the N-region, the PN junction is said to be forward biased as shown in Fig.

- When the junction is forward biased, the holes in the p-region are repelled by the positive terminal of the battery and are forced to move towards the junction.

- Similarly the electrons in the N-region are repelled by the negative terminal of the battery and are forced to move towards the-junction.

- This reduces the width of the depletion layer and barrier potential. If the applied voltage is greater than the potential barrier v<sub>r</sub>, then the majority carriers namely holes in P-region and electrons in N-region cross the barrier. During crossing some of the charges get neutralized the remaining charges after crossing, reach the other side and constitute current in the forward direction. The PN junction offers very low resistance under forward biased condition.

- Since the barrier potential is very small (nearly 0.7 V for silicon and 0.3 V for Germanium junction), a small forward voltage is enough to completely eliminate the barrier. Once the

potential barrier is eliminated by the forward voltage, a large current starts flowing through the PN junction.

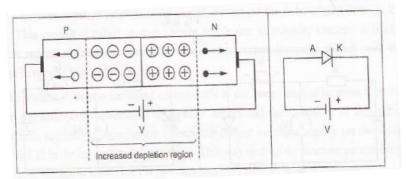

# **Reverse Bias:**

- ➤ When the positive terminal of the external battery is connected to the N-region and negative terminal to the p-region, the PN junction is said to be reverse biased.

- When the junction is reverse biased, the holes in the P-region are attracted by the negative terminal of the battery. Similarly the electrons in the N-region are attracted by the positive terminal of the external battery.

- > This increases the width of the depletion layer and barrier potential (Vs).

- The increased barrier potential makes it very difficult for the majority carriers to diffuse across the junction. Thus there is no current due to majority carriers in a reverse biased PN junction. In other words, the PN junction offers very high resistance under reverse biased condition.

- In a reverse biased PN junction, a small amount of current (in µA) flows through the junction because of minority carriers. ( i.e., electrons in the P-region and holes in the N region). The reverse current is small because the number of majority carrier in both regions is small.

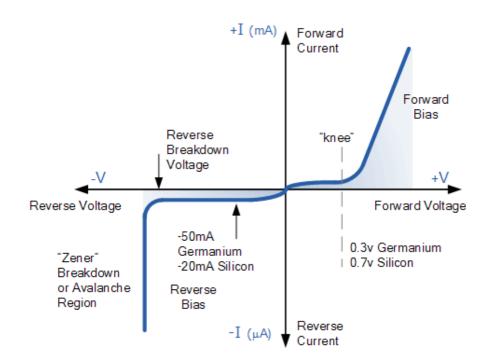

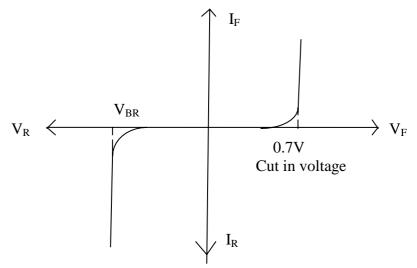

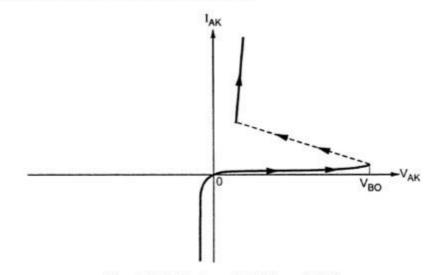

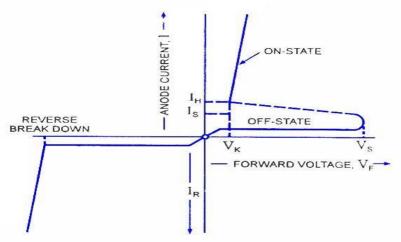

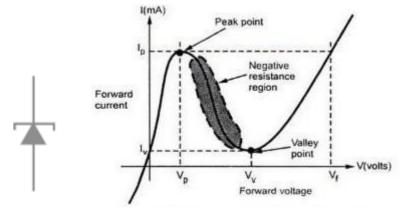

# > V-l characteristics of PN-Junction Diode:

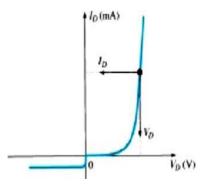

A graph between the voltage applied across the PN junction and the current flowing through the junction is called the V-I characteristics of PN junction diode. Fig. shows the V-I characteristics of PN junction diode.

# **Forward Characteristics:**

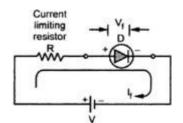

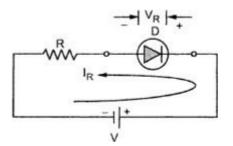

- Fig. shows the circuit arrangement for drawing the forward V-I characteristics of PN junction diode. To apply a forward bias, the +ve terminal of the battery is connected to Anode (A) and the negative terminal of the battery is connected to Cathode (K). Now, when supply voltage is increased the circuit current increases very slowly and the curve is non linear

- The slow rise in current in this region is because the external applied voltage is used to overcome the barrier potential (0.7 V for Si; 0.3V for Ge) of the PN junction' However once the potential barrier is eliminated and the external supply voltage is increased further, the current flowing through the PN junction diode increases rapidly. This region of the curve is almost linear. The applied voltage should not be increased beyond a certain safe limit, otherwise the diode will burnout.

- > The forward voltage at which the current through the PN junction starts increasing rapidly is called by **knee voltage**. It is denoted by the letter  $V_B$ .

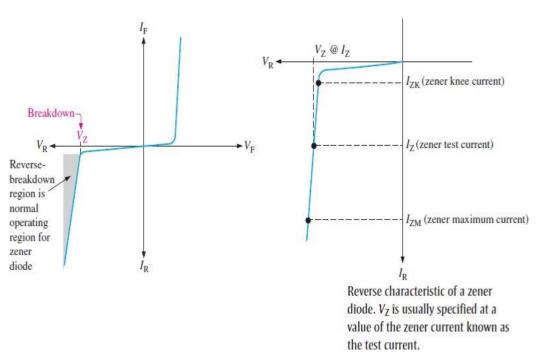

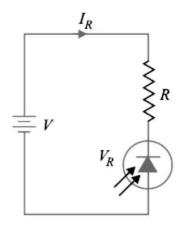

#### **Reverse Characteristics:**

- Fig shows the circuit arrangement for drawing the reverse V-I characteristics of PN junction diode. To apply a reverse bias, the +ve terminal of the battery is connected to cathode (K) and ve terminal of the battery is connected to anode (A).

- Under this condition the potential buried at the junction is increased. Therefore the junction resistance becomes very high and practically no. current flows through the circuit. However in actual practice, a very small current (of the order of µA) flows in the circuit. This current is called reverse current and is due to minority carriers. It is also called as reverse saturation current (I). The reverse current increases slightly with the increase in reverse bias supply voltage.

- ➢ If the reverse voltage is increased continuously at one state breakdown of junction occurs and the resistance of the barrier regions falls suddenly. Consequently the reverse current increases rapidly to a large value. This may destroy the junction permanently. The reverse voltage at which the PN junction breaks is called as break down voltage.

#### 6. Explain the temperature effects on characteristics. [Nov/Dec 2014][April 2015]

Diode terminal characteristics equation for diode junction current:

$$I = I_0 (e^{\frac{v}{\eta v_T}} - 1)$$

Where  $V_T = Volt$ -equivalent of temperature. Its value is given by the relation, T/11600 where T is absolute temperature. At room temperature  $V_T$  is equal to 26 mV;

V-External voltage. It is positive for forward bias and negative for reverse bias

- Io-Reverse saturation current, A

- k Boltzmann's constant (1.38x 10<sup>-23</sup>J/K)

- q electron charge  $1.6 \times 10^{-19}$  C

- $\eta$  = empirical constant, 1 for Ge and 2 for Si

At room temperature,  $V_T$  is equal to 26 mV, substituting the value of  $V_T$  is

$$I = I_0 (e^{\frac{40\nu}{\eta}} - 1)$$

When  $\eta = 1$

$$I = I_0 \left( e^{\frac{40\nu}{2}} - 1 \right)$$

η=2

$$I = I_0 (e^{\frac{20v}{-1}} - 1)$$

When diode is reverse biased,

$$I = I_0 (e^{\frac{-V}{\eta v_T}} - 1)$$

$$\approx I_0$$

#### **Temperature Effects on Diode**

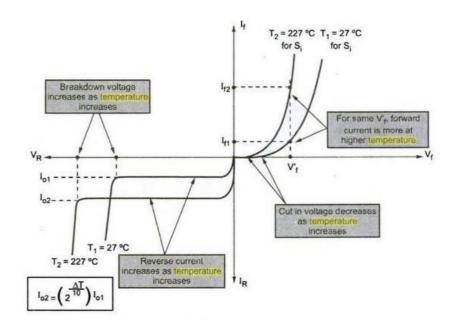

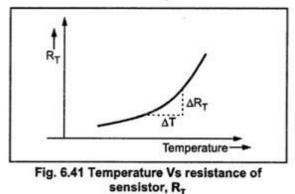

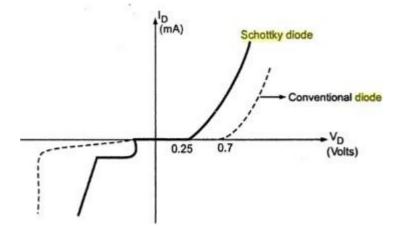

Temperature can have a marked effect on the characteristics of a silicon semiconductor diode as shown in Fig. 1.6. Temperature has following effects on the diode parameters,

- The cut in voltage decreases as the temperature increases. The diode conducts at smaller voltages at large temperature.

- The reverse saturation current increases as temperature increases.

It has been found experimentally that the reverse saturation current Io will just about double in magnitude for every 10°C increase in temperature

$$I_{02} = 2^{\left(\frac{\Delta T}{10}\right)} I_{01}$$

$I_{01}$ ,  $I_{02}$  are the reverse current at  $T_1^{\circ}C$ ,  $T_2^{\circ}C$

$\Delta T = T_2 - T_{1.}$

- The voltage equivalent of temperature V<sub>T</sub> also increases as temperature increases.

- The reverse breakdown voltage increases as temperature increases

- It is not common for a germanium diode with an Io in the order of 1 or 2 A at 25°C to have a leakage current of 100 A \_ 0.1 mA at a temperature of 100°C.

- Typical values of Io for silicon are much lower than that of germanium for similar power and current levels.

- The result is that even at high temperatures the levels of Io for silicon diodes do not reach the same high levels obtained. For germanium—a very important reason that silicon devices enjoy a significantly higher level of development and utilization in design.

- Fundamentally, the open-circuit equivalent in the reverse bias region is better realized at any temperature with silicon than with germanium.

- The increasing levels of Io with temperature account for the lower levels of threshold voltage, as shown in Fig above

- Simply increase the level of Io in and not rise in diode current. Of course, the level of TK also will be increase, but the increasing level of Io will overpower the smaller percent change in TK.

- ➤ As the temperature increases the forward characteristics are actually becoming more -ideal, ||

# 7. Explain static and dynamic resistance of diode [Nov/Dec 2015]

# DC or Static Resistance

- A real diode does not behave a perfect insulator when reverse biased and does not behave as perfect conductor when forward biased.

- > It means that diode has a definite value of resistance when forward biased.

- The application of a dc voltage to a circuit containing a semiconductor diode will result in an operating point on the characteristic curve that will not change with time.

> The resistance of the diode at the operating point can be found simply by finding the corresponding levels of  $V_D$  and  $I_D$  as shown in Fig. below and applying the following Equation:

$$R_{D = \frac{V_{D}}{I_{D}}}$$

- The dc resistance levels at the knee and below will be greater than the resistance levels obtained for the vertical rise section of the characteristics.

- The resistance levels in the reverse-bias region will naturally be quite high. Since ohmmeters typically employ a relatively constant-current source, the resistance determined will be at a preset current level (typically, a few mill amperes).

Figure 1.7 determining the dc resistance of a diode at a particular operating point.

#### AC or Dynamic Resistance

- It is obvious from Equation that the dc resistance of a diode is independent of the shape of the characteristic in the region surrounding the point of interest.

- > If a sinusoidal rather than dc input is applied, the situation will change completely.

- The varying input will move the instantaneous operating point up and down a region of the characteristics and thus defines a specific change in current and voltage as shown in Fig. 1.7.

- With no applied varying signal, the point of operation would be the Q-point appearing on Fig.

1.7 determined by the applied dc levels.

- ➤ The designation Q-point is derived from the word quiescent, which means -still or unvarying.

- A straight-line drawn tangent to the curve through the Q-point will define a particular change in voltage and current that can be used to determine the ac or dynamic resistance for this region of the diode characteristics.

In equation form,

$$r \xrightarrow{\Delta v_d} d = \Delta I_d$$

Where  $\Delta$  is finite change in quantity.

- In addition to the forward resistance, the diode also possesses reverse resistance which is very large when compared to the forward resistance.

- ➢ Its value is in several meghohms.

The a.c resistance can be determined from the following:

#### **Bulk resistance:**

The resistance of the P and N type semiconductor materials of which diode is made of is known as body or bulk resistance. It also includes resistance introduced by the connection between the semiconductor material and the external metallic conductor also called contact resistance.

$$r_B = r_P + r_N$$

where

$r_P$ -ohmic resistance of the P type semiconductor

$r_N$ -ohmic resistance of the N type semiconductor

This typically ranges from 0.1 ohm for high power devices to 2 ohm for low power device. Junction resitance:

$r_{j} = 26/I_{F}$

where  $I_F$  is forward current in milliamperes.

From the relation it is observed that junction resistance is variable resistance.

The a.c resitance will be equal to the sum of junction and bulk resistance.

$$R_{ac}=r_{\rm j}+r_B$$

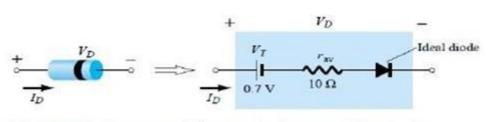

# 8. Explain equivalent circuit of diode in detail.

- An equivalent circuit is a combination of elements properly chosen to best represent the actual terminal characteristics of a device, system, or such in a particular operating region.

- In other words, once the equivalent circuit is defined, the device symbol can be removed from a schematic and the equivalent circuit inserted in its place without severely affecting the actual behaviour of the system.

- The result is often a network that can be solved using traditional circuit analysis techniques.

Piecewise-Linear Equivalent Circuit

- One technique for obtaining an equivalent circuit for a diode is to approximate the characteristics of the device by straight-line segments.

- The resulting equivalent circuit is naturally called the piecewise-linear equivalent circuit. It should be obvious that the straight-line segments do not result in an exact duplication of the actual characteristics, especially in the knee region.

- However, the resulting segments are sufficiently close to the actual curve to establish an equivalent circuit that will provide an excellent first approximation to the actual behaviour of the device.

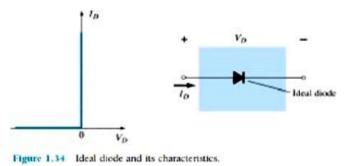

- The ideal diode is included to establish that there is only one direction of conduction through the device, and a reverse-bias condition will result in the open- circuit state for the device.

- Since a silicon semiconductor, diode does not reach the conduction state until  $V_D$  reaches 0.7 V with a forward bias, a battery  $V_T$  opposing the conduction direction must appear in the equivalent circuit as shown in Fig. 1.32.

- The battery simply specifies that the voltage across the device must be greater than the threshold battery voltage before conduction through the device in the direction dictated by the ideal diode can be established.

- > When conduction is established, the resistance of the diode will be the specified value of  $r_{av}$ .

Figure 1.32 Components of the piecewise-linear equivalent circuit.

The approximate level of r<sub>av</sub> can usually be determined from a specified operating point on the specification sheet. For instance, for a silicon semiconductor diode, if I<sub>F</sub> \_ 10 mA (a forward conduction current for the diode) at V<sub>D</sub> \_ 0.8 V, we know for silicon that a shift of 0.7 V is required before the characteristics rise.

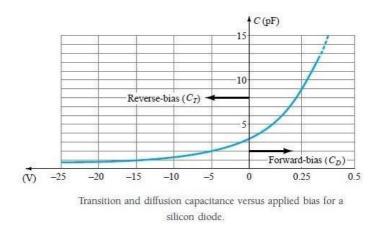

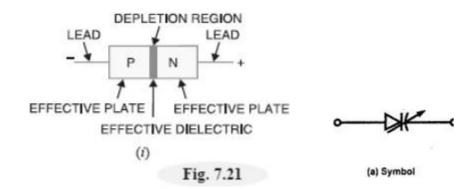

# 9. Explain transition and diffusion capacitance in detail

- Electronic devices are inherently sensitive to very high frequencies. Most shunt capacitive effects can be ignored at lower frequencies because the reactance  $X_C=1/2\pi fC$  is very large (open-circuit equivalent).

- > This, however, cannot be ignored at very high frequencies.  $X_C$  will become sufficiently small due to the high value of **f** to introduce a low-reactance –shorting || path.

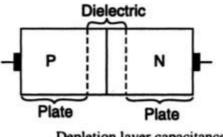

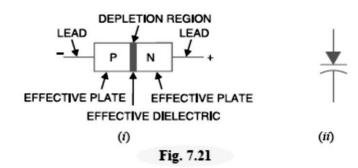

- Capacitors store electric charge in the form of electric field. This charge storage is done by using two electrically conducting plates (placed close to each other) separated by an insulating material called dielectric.

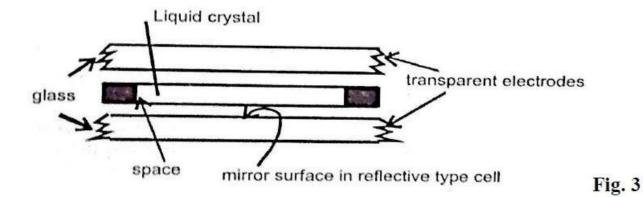

- The depletion region of the p-n junction diode has high resistance. Hence, the depletion region acts like the dielectric or insulating material. Thus, p-n junction diode can be considered as a parallel plate capacitor.

- > In the p-n semiconductor diode, there are two capacitive effects to be considered.

- > In the reverse-bias region we have the transition- or depletion region capacitance ( $C_T$ ), while in the forward-bias region we have the diffusion ( $C_D$ ) or storage capacitance.

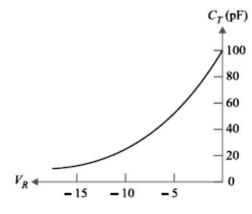

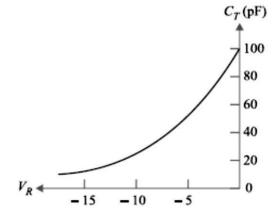

# Transition capacitance (C<sub>T</sub>):

- When a PN junction is formed, a layer of positive and negative impurity ions called depletion layer is formed on either side of the junction.

- > The depletion layer acts as dielectric medium between P region & N region.

- The P & N region on either side of the junction acts as two plates of a capacitor separated by a dielectric i.e. depletion layer.

Depletion layer capacitance.

- > The capacitance formed in a junction area is called depletion layer capacitance.

- It is also called depletion region capacitance, space charge capacitance, transition region capacitance.

- > The capacitance of parallel plate capacitor is given by  $C_T = \frac{CA}{W}$

$\mathcal{E} = Permittivity of material$

$A = cross \ section \ area \ of \ junction$

- *W* = *Width of depletion layer*

- > When no external voltage is applied, the width of depletion region of PN diode is of the order of 0.5 microns with a capacitance of  $C_T = 20 pF$ .

- When reverse bias voltage applied to the p-n junction diode is increased, a large number of holes (majority carriers) from p-side and electrons (majority carriers) from n-side are moved away from the p-n junction. As a result, the width of depletion region increases whereas the size of p-type and n-type regions (plates) decreases.

- > The capacitance of the reverse bias p-n junction diode decreases when voltage increases.

- > The value of  $C_T$  ranges from 5 to 200pF.

- Since the thickness of depletion layer depends on the amount of reverse bias, CT can be controlled with the help of applied bias.

- > This property of variable capacitance is used in varicap or varactor diode.

- > This capacitance is voltage dependent and is given by

$$C_{T=\frac{k}{Vk+VR}}$$

Where,  $V_{K}$ = Knee voltage,  $V_{R}$ = Applied reverse voltage K = Constant depending on semiconductor,

> N=1/2 for alloy junction = 1/3 for diffused junction

#### **Diffusion capacitance (CD):**

- The capacitance that exists in a forward biased junction is called diffusion capacitance or storage capacitance, whose value is usually much larger than C<sub>T</sub> which exists in a reverse biased junction.

- When forward bias voltage is applied to the p-n junction diode, electrons (majority carriers) in the n-region will move into the p-region and recombines with the holes. In the similar way, holes in the p-region will move into the n-region and recombines with electrons. As a result, the width of depletion region decreases.

- This depletion region acts like dielectric or insulator of the capacitor and charge stored at both sides of the depletion layer acts like conducting plates of the capacitor.

- > Diffusion capacitance is proportional to diode forward current, I.

- > The diffusion capacitance is given by  $C_D = \frac{I}{\eta V_T}$

$\tau$  = the mean life time for holes & electrons

The diffusion capacitance at low frequencies is given by the formula:

$C_D = \tau^* g/2$  (low frequency)

The diffusion capacitance at high frequencies is inversely proportional to the frequency and is given by the formula:

$C_D = g(\tau/2\omega)^{\frac{1}{2}}$

Diffusion capacitance is also defined as rate of change of injected charge with applied voltage i.e. C<sub>D</sub> = dQ/dV, where dQ represents the change in the number of minority carriers stored outside the depletion region when a change in voltage across the diode dV is applied.

- > The effect of  $C_D$  is negligible for a reverse biased PN junction.

- As the value of C<sub>D</sub> is inversely proportional to frequency, it is high at low frequencies and it decreases with the increase in frequency.

- > The values of C<sub>D</sub> ranges from **10 to 1000 pF**.

# 10. Explain the drift and diffusion currents for PN diode. [April 2015]

#### **Drift Current:-**

In a conductor or Semiconductor, at room temperature, a free electron will move toward the positive terminal under the influence of electric field, But it will continually collide with atoms along the way. The presence of electric field does not stop the collisions and random motion, but it does cause the electron to drift in the direction of applied electric force. This current is known as Drift Current.

# **Diffusion Current:**

- Consider a piece of semiconductor which is non uniformly doped. Due to such doping, one type of charge carriers occurs at one end of a semiconductor.

- > The charge carriers are either electrons or holes. They have the same polarity or hence experience a force of repulsion between them.

- As a result the charge carriers move gradually from region of high carrier density to low carrier density. This process is called diffusion. The movement of charge carriers under the process of diffusion constitutes a current called diffusion current.

Without electric field non - uniform concentration of change

$J_p = -q D_p dp/dx$  $J_n = q D_n dn/dx$

Derive the current Equation of a Diode

$p_n(x) = P_{no} + P_n(o) e^{-x/LP}$

$p_n(x)$  = Concentration of holes at distance n

$p_{no} =$  Thermal Equilibrium value

$L_p$  = Diffusion length for holes in the a – material

$p_p \qquad = p_n \, e^{-Vj/VT}$

Law of function Derivation

$$\begin{array}{rcl} p_{po} &= p_{no}.e^{\ V0/VT} \\ p_{no} &= \ p_n(0) & e^{-V/VT} \\ p_n(o) &= p_{no}. \ e^{V/VT} \\ I_{pn} &(0) &= qA \ D_p. \ p_{no} \ /L_p[e^{\ V/VT}-1] \\ I_{np} &(0) &= qA \ Dp. \ n_{po}/L_n \ [e^{\ V/VT}-1] \\ I &= I_{np} \ (0) + I_{np} \ (0) \\ I &= I_0 \ [e \ V/V_T-1] \\ I_0 &= \ qA \ D_p. \ p_{no} \ /L_p \ + qA \ Dp. \ n_{po}/L_n \end{array}$$

# 11. Discuss the application of diode. [Nov/Dec 2014]

#### Signal rectifier

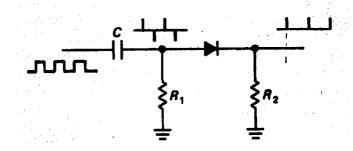

- If the input is not a sine wave, we usually do not think of it as a rectification in the sense as it was for power supply.

- For instance, we might want to have a series of pulses corresponding to the rising edge of a square wave (see Fig. 10, left hand side and right hand side of the capacitor C).

- While both, the rising and the falling, pulses are in the output after differentiation performed by CR circuit. The simplest way is to rectify the differentiated wave.

Fig.10. A series of pulses' rectifier.

We should remember about forward drop voltage of the diode: This circuit gives no output for signal for input smaller then, forward drop voltage, let us say 0.5 V pp (peak to peak). If this is a problem, there are various tricks that help to combat this limitation. For instance:

- 1. use Schottky diodes with smaller forward drop voltage (approximately 0.2V),

- 2. use so called circuit solution, which means modifying the circuit structure and compensating the drop,

- 3. Use matched-pair compensation, use transistors, FETs.

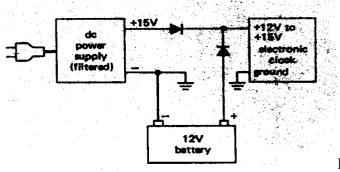

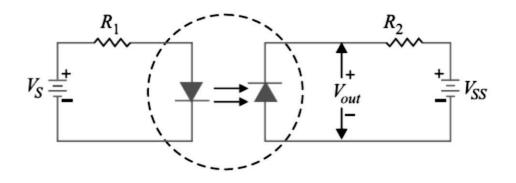

Diode gates

- > Another application of diode is to pass the higher of two voltages without affecting the lower.

- A good example is battery backup, a method of keeping s device running (for instance a precision electronic clock) in case of power failure. Figure 11 shows a circuit that does the job.

[**OR gate**: *The output of OR gate is HIGH if either input (or both) is HIGH. In general, gates can have any number of inputs. The output is LOW only if all inputs are LOW*].

- 1. The battery does nothing until the power fails.

- 2. Then the battery takes over the control, without interruption.

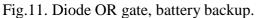

#### Diode clamps

Sometimes it is necessary to limit the range of signal (for instance not to exceed certain voltage limit and not to destroy a device). The circuit in Fig. 12 will accomplish this.

Fig.12. Diode voltage clamp.

- The diode prevents the output from exceeding  $\approx 5.6$ V, with no effect on voltages smaller than this, including negative voltages.

- The only limitation is that the input must not be so negative that the reverse breakdown voltage is exceeded. Diode clamps are the standard equipment on all inputs in the CMOS family of digital logic (Complementary Metal Oxide Semiconductor).

- > Without them, the delicate input circuits are easily destroyed by static electricity.

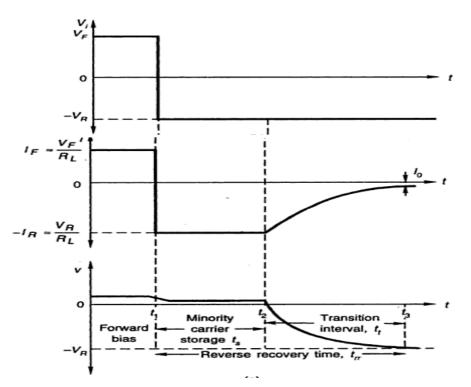

# 12. Describe diode switching with timing diagram. [Nov/Dec 2015]

Diodes are often used in a switching mode.

- When the diode is switched from F.B to R.B, it takes a finite time to attain a steady state. The time consists of transient and interval of time before diode attains steady state.

- > The behavior of diode during this time is called switching characteristics of diode.

- When the applied bias voltage to the PN diode is suddenly reversed in the opposite direction, the diode response reaches a steady state after an interval of time called *recovery time*.

- The *forward recovery time* (T<sub>fr</sub>) is defined as the time required for forward voltage or current to reach a value after switching diode from its reverse to forward biased state.

- The *reverse recovery time* (T<sub>rr</sub>) is defined as the time required for reverse voltage or current to reach a value after switching diode from its forward to reverse biased state.

- Most diodes switch very quickly into the forward biased condition; however there is a longer turnoff time owing to the junction diffusion in reverse biased condition.

- When the PN junction diode is forward biased, the minority electron concentration in the P region is approximately linear.

# Event 1:

Till  $t_1$ , the forward voltage  $V_F$  is applied and diode is forward biased.

# Event2:

The applied voltage is suddenly reversed and reverse voltage  $-V_R$  is applied.

- Because of stored electronic charge, the reverse current I<sub>R</sub> is initially of the same magnitude as the forward current I<sub>F</sub>.

- When the pulse switches from positive to negative, the diode conducts in reverse instead of switching off sharply.

- > The reverse current  $I_R$  initially equals the forward current  $I_F$ , then it gradually decreases towards zero.

- The high level of reverse of reverse current occurs because at the instant of reverse bias there are charge carriers crossing the junction depletion region, and these must be removed.

- During the interval from t<sub>1</sub> to t<sub>2</sub>, the injected minority carrier have remained stored & hence this time interval is called *storage time t<sub>s</sub>*

# Event 3:

- $\succ$  From T<sub>2</sub> onwards the diode voltage starts to reverse and the diode current starts decreasing.

- After the instant  $t = t_3$  the diode gradually recovers and ultimately reaches the steady state.

- The time interval between t<sub>2</sub> & t<sub>3</sub> when the diode has recovered nominally is called *transition time t<sub>t</sub>*.

- The total time required by the diode is the sum of storage time and transition time, to recover completely from change of state is called reverse recovery time. The typical values of reverse recovery time T<sub>rr</sub> for switching diode ranges from 4ns to 50ns.

# $T_{rr} = t_s + t_t$

> The switching time  $t_{rr}$  limits the operating frequency of the diode.

To minimize the effect of reverse current the time period of operating frequency should be at least ten times t<sub>rr</sub>

Figure: Switching characteristics of PN junction diode

#### (2marks)

#### 1. Define forbidden energy gap

The energy gap between the valence band and conduction band is defined as forbidden energy gap. For insulators. it is around 6ev, for semiconductors, its value is comparatively low. Germanium has energy gap 0.7ev and silicon has 1.1ev. For conductors, since conduction and valence bands are overlapping the energy gap is zero.

#### 2. What is doping? [Nov/Dec 2014]

The process of adding impurity to pure semiconductor is known as doping. As a result of it the characteristics of semiconductor is changed and hence the conductivity increases.

# 3. Define Fermi level. [Nov/Dec 2014]

The Fermi level is defined as the maximum energy level, which is occupied by electron at absolute zero temperature. In P- type semiconductor the Fermi level will be above the top of the valence band. In N-type it lies below the bottom of the conduction band.

# 4. What are donor and acceptor impurities?

Pentavalent impurities (Antimony, Arsenic) have five valence electrons. They can donate one excess electron to adjacent atoms to complete lattice structure, therefore they are called donor impurities.

Trivalent impurities (Indium, Gallium) has three valence electrons. They have tendency to accept one electron from adjacent atoms to complete lattice structure, therefore they are known as acceptor impurities.

# 5. State mass action law.

Mass action law states that in a semiconductor the product of the number of holes and the number of electrons is constant and is independent of the amount of donor and acceptor impurity doping.

$np = n_i^2$

where n= free electron concentration

p= hole concentration;  $n_i$  = intrinsic concentration

# 6. Define the term the drift current.

If a steady electric field is applied across a semiconductor, it causes the free electrons to move towards the positive terminal and the holes move towards the negative terminal of the battery. This combined effect causes a current flow in the semiconductor. The current produced in this manner is known as drift current.

Drift current density due to electrons

$J_n = q \ n \ \mu_n \ E$

Drift current density due to holes

$J_p = q p \mu_p E$

$J_n$  = Drift current density due to electrons

$J_p = Drift$  current density due to holes

q = Charge of the carrier

$\mu_n$  = Mobility of electrons

$\mu_p$  = Mobility of holes

E = Applied electric field strength.

# 7. What is diffusion current? (Nov 2014)

In a semiconductor it is possible to have a non uniform distribution of carriers. A concentration gradient exists if the number of either holes or electrons is greater in one region as compared to the rest of the region. The holes and electrons then tend to move from a region of higher concentration to lower concentration region.

This process is known as diffusion and the electric current produced due this process is known as diffusion current.

# 8. What is a PN junction diode? [Nov/Dec 2015]

A PN junction diode is a two terminal device consisting of a PN junction formed either of Germanium or Silicon crystal. A PN junction is formed by diffusing P type material to one half side and N type material to other half side.

# 9. Define and explain peak inverse voltage (PIV) (Nov 2013)

Peak inverse voltage is the maximum reverse voltage that can be applied to the PN junction without damage to the junction. If the reverse voltage across the junction exceeds to its peak inverse voltage, the junction may be destroyed due to excessive heat.

# 10. Differentiate drift and diffusion current

| Drift current                                         | Diffusion current                                                                       |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 1. Developed due to potential gradient                | Developed due to concentration gradient                                                 |

| 2. Phenomenon found both in semiconductors and metals | Only in semiconductros                                                                  |

| 3. $J_n = qn \mu_n E$                                 | $J_n = q D_n dn / dx$                                                                   |

| $J_p = q \ p \ \mu_p \ E$                             | $\mathbf{J}_{p} = \mathbf{q} \ \mathbf{D}_{p} \ \mathbf{d}p \ / \ \mathbf{d}\mathbf{x}$ |

# **11. Define valence electron.**

Electrons that are in shells close to nucleus are tightly bounced to the atom and have low energy. Whereas electrons that are in shells farther from the nucleus have large energy and less tightly bound to the atom. Electrons with highest energy level exist in the outermost shell of an atom. These electrons determine the electrical and chemical characteristic of each particular type of atom. These electrons are known as valence electrons.

# 12. What is meant by energy band?

In a single isolated atom, the electron in any orbit possesses define energy. Due to an interaction between atoms the electrons in a particular orbit of one atom have slightly different energy levels from electrons in the same orbit of an adjoining atom. This is due to the fact that no two electrons see exactly the same pattern of surrounding charges. Since there are billions of electrons in any orbit, slightly different energy levels form a cluster or band known as energy band.

#### 13. What are conductors, Insulators and semiconductors?

A conductor is a material, which easily allows the flow of electric current. The best conductors are copper, silver, gold and aluminum.

An Insulator is a material that does not conduct electric current. In these materials valence electrons are tightly bound to the atoms.

A semiconductor is a material that has an electrical conductivity that lies between conductors and insulators. A semiconductor in it's pure state is neither a good conductor not a good insulator. The most common semiconductors are silicon, Germanium, and carbon.

# 14. What are the classifications of semiconductors?

Semiconductors are classified as intrinsic and extrinsic semiconductors. A pure semiconductor is called intrinsic semiconductor. A doped semiconductor is called extrinsic semiconductor.

# 15. How the extrinsic semiconductors are classified?

(a) n-type semiconductor

(b) p-type semiconductor

#### 16. How an *n*-type semiconductor can be obtained?

A n-type semiconductor can be obtained by adding pentavalent impurities to an intrinsic semiconductor. These are atoms with five valence electrons. Typical examples for pentavalent atoms are Arsenic.Phosphorous, Bismuth and Antimony.

# 17. How a p-type semiconductor can be obtained?

A p-type semiconductor can be obtained by adding trivalent impurities to an intrinsic semiconductor. These are atoms with three valence electrons. Typical examples for trivalent atoms are boron(B),indium(In) and gallium(Ga).

#### **18.What is depletion region?**

When a pn junction is formed free electrons from the n-side diffuse across the junction, and fill the holes on the p-side and create positive ions. Similarly the holes from p-side diffuse across the junction and recombine with electrons in n-side and create negative ions. Since negative ions are created on p-side of the junction, the region close to the junction acquires a negative charge. Similarly the positive ions created on the n-side gives a positive charge near the junction. As these

charges build up a point is reached where the total negative charge in p-region repels any further diffusion of electrons (negatively charged particals) into the p-region (like charges repels) and the diffusion stops. At this point the positive ions on n-side and negative ions on p-side are immobile (fixed). They cannot serve as current carriers. That is the region is almost completely depleted of carriers. This region near the junction is called the depletion region. The width of the depletion region is about  $1_{\mu m}(10^{-6}m)$ .

#### **19.** What is barrier potential?

The intimate contact between p and n materials from a depletion layer near the junction. Since the depletion layer contains positive charges on the right side of the pn junction and negative ions on the left side of the pn-junction an electric field is formed. The electric field producers a barrier to the free flow of electrons in the n-region, and energy must be spent to move an electron through the electric field. That is an external energy must be applied to move an electro through the electric field. The external energy depends on the potential difference of the electric field across the depletion region. This potential difference which is required to move electrons through the electric field is known as barrier potential ( $V_{\circ}$ ) and it is expressed in volts.

#### 20.What is the barrier potential for Ge and Si?

The barrier potential for GE is 0.3V and for Si 0.7V.

#### 21. What is meant by forward bias?

When the positive terminal of a battery is connected to p- side of the device and the negative terminal is connected to n-side of the device then the device is said to be forward biased. At forward

bias, large current will flow in the range of milli amperes  $(10^{-3}A)$ . Forward bias is equivalent to short circuit

#### 22. What is meant by reverse bias?

When the negative terminal of a battery is connected to p-side device and positive terminal is connected to n-side then the device is said to be reverse biased. At reverse bias, small current will

flow in the range of micro amperes  $(10^{-6})$ . Reverse bias is equivalent to open circuit.

# 23. What is meant by break down voltage?

If the reverse biased voltage is increased, the velocity of minority charge carriers crossing the junction increases. These carriers acquire high kinetic energy and collide with the atom. As a result the valence electron in the atom observes sufficient energy and leave the parent atom. These additional carriers also get sufficient energy from the applied reverse biased and collide with other atom and generate some more carriers. This collision and generation of carriers is a cumulative effect, which result in large amount of reverse current. This phenomena, known as breakdown occurs at a particular reverse voltage for a pn junction. This known as reverse breakdown voltage.

#### 24. Draw the V-I characteristics of a diode.

25. Define static and dynamic resistance of a diode.

The static resistance  $R_F$  of a diode is defined as the ratio V/I of the voltage to the current that can be obtained by finding the reciprocal of the slope of a line joining the operating point to the orgin. But it is not a useful parameter as the resistance varies widely with V and I. The dynamic resistance is defined as the reciprocal of the slope of volt-ampere characteristics.

$$R_{F} = \frac{V_D}{I_D}$$

# 26. What are the applications of a diode.

In rectification, clampers, clippers, switching circuits, comparators, voltage doublers and diode gates.

#### 27. Explain how a reverse biased pn junction exhibits a capacitor?

The width of the depletion layer can be controlled using reverse biased voltage. Since the depletion layer is an insulator, the pn junction can be thought of as a parallel plate capacitor and p and n regions act like plates of a capacitor (p-region positive plate, n-region negative plate).

#### 28. Discuss how capacitance varies with reverse biased voltage.

The depletion region increases as reverse voltage applied to diode increases. Since capacitance varies inversely with dielectric thickness( $C_T = \frac{EA}{w}$ ; as w increases c decreases), the junction capacitance will

decrease as the voltage across pn junction increases.

#### 29. Define knee voltage.

It is the forward voltage of a PN diode at which the current thorough the junction starts increasing rapidly.

#### 30. Define breakdown voltage.

It is the reverse voltage of a PN junction diode at which the junction breaks down with sudden rise in the reverse current

# **31. Define transition capacitance of a diode.**

Transition Capacitance (CT) or Space-charge Capacitance: When a PN- junction is reverse-biased, the depletion region acts like an insulator or as a dielectric.

The P- and N-regions on either side have low resistance and act as the plates. Hence it is similar to a parallel-plate capacitor. This junction capacitance is called transition or space-charge capacitance ( $C_T$ ).

It is given by  $C_T = \varepsilon A/D$

Where, A = Cross-sectional area of depletion region.

D = Width (or) thickness of depletion region. Its typical value is 40 pF.

# **REFERENCE BOOKS:**

1. JacobMillmanandChristosC.Halkias,"ElectronicDevicesandCircuits",Tata-McGraw Hill, 2003.

2. Robert L. Boylestad and Louis Nashelsky, "Electronic Devices and Circuit Theory", Prentice-Hall India, 2009.

3. David A Bell, "Electronic Devices and Circuits", PHI, 4thEdition, 2006.

# DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING

#### Subject Name: ELECTRONIC DEVICES AND CIRCUITS

Subject Code: EE T34

#### **UNIT – II BIPOLARJUNCTION TRANSISTORS**

Construction and operation– NPN and PNP transistors– CB, CE and CC configurations– transistor characteristics and regions of operation–Specification sheet–Biasing of BJTs– operating point–stabilization of operating point–different biasing circuits and DC load line characteristics –Bias compensation techniques–thermal stability and thermal runaway.

#### (2 marks)

#### 1. Why base is made thin in BJT? [Nov/Dec 2014]

Transistor consists of three portions namely emitter, base and collector. Among them base forms the middle part. It is very thin and lightly doped because it allows most of the emitter current carriers towards the collector. Since base is acting as an interface it doesn't need more area.

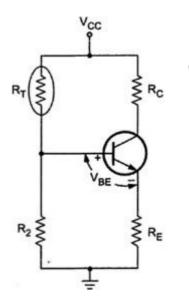

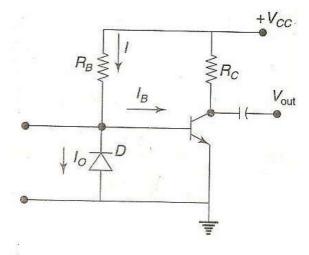

#### 2. What is meant by biasing a transistor? Why is it necessary?[Nov/Dec 2015]

For normal operation base emitter junction should be forward biased and collector base junction should be reverse biased .The proper flow of zero signal collector current and the maintenance of collector-emitter voltage during the passage of signal is called the transistor biasing. The amount of biasing required is significant for the establishment of the operating or Q-point which decides the mode of operation.

#### **3. Define the different operating regions of transistor.** . [Nov/Dec 2014]

Active region: It is defined in which transistor collector junction is biased in reverse direction and emitter junction in forward direction.

Cutoff region: The region in which the collector and emitter junctions are both reverse-biased

Saturation region : The region in which both the collector and emitter junctions are forward biased.

# 4. Define Base width modulation (Early effect) . [Nov 2013]

In a CB configuration, an increase in collector voltage increases the width of the depletion region at the output junction diode. This will decrease the effective width of the base. This is known as early effect. Due to this effect recombination rate reduces at the base region and charge gradient is increased within the base.

# 5. Explain the significance of Base width modulation (Early effect) . [Nov 2013]

a) It reduces the charges recombination of electrons with holes in the base region, hence the current gain increases with the increase in collector -base voltage

b) The charge gradient is increased within base; hence the current due to minority carriers injected across emitter junction increases.

# 6. What are the three types of configurations? [Nov/Dec 2015]

Common base configuration, Common emitter configuration Common collector configuration

# 7. Among CB, CE, CC which is most important?

The CE configuration is important. The reasons

- i) High current gain

- Output to input impedance ratio is moderate therefore easy coupling is possible between various transistor stages

- iii) It finds excellent usage in audio frequency applications hence used in receivers and transmitters

# 8. Give the advantages of CE configuration. . [Nov 2013]

- i. High output impedance

- ii. High current gain

- iii. High power gain

# 9. What is thermal runaway? [Nov 2013]

The reverse saturation current in a semiconductor doubles for every 100 C rise in temperature I as temperature increases the leakage current increases I and the collector current also increases. The increase in collector produces an increase in power dissipation at the collector - base junction. This I in turn further increases the temperature of the collector-base junction causing the collector current to further increase. This process may become cumulative and it is possible for the transistor to burn out. This process is known as Thermal runaway.

#### **10.** How thermal runaway can be avoided?

Thermal runaway can be avoided using a stabilization or heat sink with the transistor.

#### 11. How a transistor is used as a switch?

A transistor should be operated in saturation and cutoff regions to use it as a switch .While operating in saturation region transistor carry heavy current hence considered as ON state. In cutoff it doesn't carry current and it is equivalent to open switch.

# 13. Which configuration is known as emitter follower and why it is named so?

CC configuration is known as emitter follower, whatever may be the signal applied at the input, may produce same signal at the output. In other words, the gain of the circuit is unity. So that the common collector circuit - the so called emitter follower is named as emitter follower. (Output follows the input)

# 14. Why do the output characteristics of CB transistor have a slight upward slope?

The emitter and collector are forward biased under the saturation region. Hence a small change in collector voltage causes a significant change in collector current .Therefore a slight upward slope is found in the output characteristics.

# 15. Compare the performance of CE, CB, CC

| Parameters                          | СВ   | СЕ     | CC   |

|-------------------------------------|------|--------|------|

| Current gain (A <sub>i</sub> )      | Low  | High   | High |

| Voltage gain (V <sub>i</sub> )      | High | High   | Low  |

| Input resistance (R <sub>i</sub> )  | Low  | Medium | High |

| Output resistance (R <sub>o</sub> ) | High | Medium | Low  |

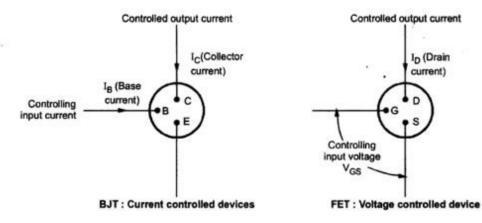

# **16.** Compare BJT and JFET (May 2010)

| BJT                   | JFET                 |

|-----------------------|----------------------|

| Low input impedance   | High input impedance |

| High Output impedance | Low output impedance |

| Bipolar device            | Unipolar device           |

|---------------------------|---------------------------|

| Noise is more             | Less noise                |

| Cheaper                   | Costlier                  |

| Gain is more              | Gain is less              |

| Current controlled device | Voltage controlled device |

# 17. Mention the advantages of FET over BJT? (Nov 2013)

i) The noise level is very low in FET since there are no junctions.

ii) FET has very high power gain iii) Offers perfect isolation between input and output since it has very high input impedance.

iv) FET is a negative temperature coefficient device hence avoids thermal runaway.

# 18. Explain why an ordinary transistor is called bipolar?

Because the transistor operation is carried out by two types of charge carriers(majority and minority carriers), an ordinary transistor is called bipolar.

#### 19. Why transistor is called current controlled device?

The output voltage, current and power is controlled by the input current in a transistor so it is called the current controlled device.

#### 20. Why silicon type transistors are more used than germanium type?

Because silicon transistor has smaller cutoff current  $I_{CBO}$ , small variations in  $I_{CBO}$  due to variations in temperature and high operating temperature as compared to those in case of germanium type.

#### 21. Why CC configuration is called a voltage buffer?

Because of its high input impedance and low output impedance, the common collector finds wide application as a buffer amplifier between a high impedance source and low impedance load. Its other name is emitter follower.

# 22. What do you mean by operating point?

Quiescent point is a point on the dc load line which represents  $V_{CE}$  and  $I_C$  in the absence of ac signal and variations in  $V_{CE}$  and  $I_C$  take place around this point where ac signal is applied.

**23. Why heat sinks are used in power amplifiers?** Heat sink is a specially designed metal sheet over which the power transistor is mounted so that it dissipates heat more effectively and protects the power transistor from overheating. It increases the area of contact with the atmosphere.

# (11 MARKS)

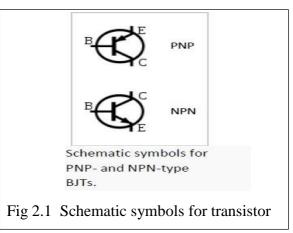

- 1. With diagram explain construction and operation of NPN transistor. [Nov/Dec 2015]

- A bipolar (junction) transistor (BJT) is a three-terminal electronic device constructed of doped semiconductor material and may be used in amplifying or switching applications.

- > Bipolar transistors are so named because their operation involves both electrons and holes.

- Charge flow in a BJT is due to bidirectional diffusion of charge carriers across a junction between two regions of different charge concentrations.

By design, most of the BJT collector current is due to the flow of charges injected from a high-concentration emitter into the base where there are minority carriers that diffuse towards the collector and so BJTs are classified as minority-carrier devices.

Construction:

$\triangleright$

- The BJT consists of silicon (or germanium) crystal in which a thin layer of **N type** silicon is **sandwiched between** two **layers of P type** silicon. This transistor is referred to as **PNP**.

- Alternatively in a NPN transistor, a layer of P type material is sandwiched between two layers of N type material.

- > The three terminals of the transistor are as follows:

**Emitter-Heavily doped** so that it can inject large charge carriers to the base.

**Base-It is lightly doped** and very thin and it passes most of the injected charge carriers from the emitter into the collector.

**Collector-It is moderately doped**

# **Operation**:

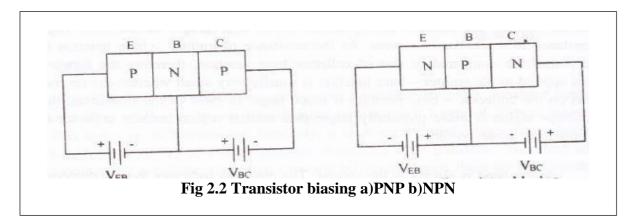

Applying external voltage to a transistor is called biasing. In order to operate transistor properly as an amplifier, it is necessary to correctly bias the two PN junctions with external voltages. Depending upon external bias voltage polarities used, the transistor works in one of the three regions.

| S.NO | REGION         | EMITTER BASE   | COLLECTOR BASE | OPERATION OF<br>TRANSISTOR |

|------|----------------|----------------|----------------|----------------------------|

| 1.   | Active region  | Forward biased | Reverse biased | Acts as an amplifier       |

| 2.   | Cut-off region | Reverse biased | Reverse biased | Acts as an open<br>switch  |

| 3 | 3. | Saturation region | Forward biased | Forward biased | Acts as a closed switch |

|---|----|-------------------|----------------|----------------|-------------------------|

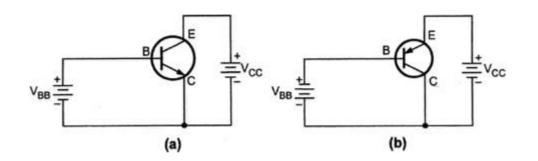

To bias the transistor in its active region the emitter base junction is forward biased, while the collector-base junction in reverse-biased as shown in Fig 2.2.Fig 2.2.shows the circuit connections for active region for both NPN and PNP transistors.

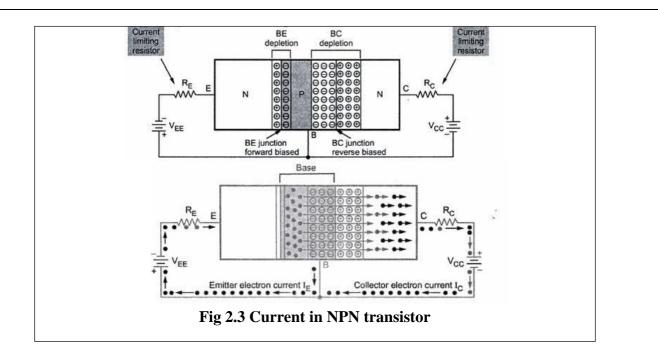

#### **Operation of NPN transistor:**

- As shown in fig 2.3 the NPN transistor is biased in the forward active mode. The emitter base junction is forward biased only if V<sub>EB</sub> is greater than barrier potential which is 0.7V for Si and 0.3 V for germanium.

- Forward bias applied to the emitter base junction of an NPN transistor causes a lot of electrons from the emitter region to cross over to the base region.

- $\succ$  This constitutes the emitter current I<sub>E</sub>

- As the base is lightly doped with P-type impurity, the number of holes in the base region is very small and hence the number of electrons that combine with holes in the P – type base region is also very small.

- $\blacktriangleright$  Hence a few electrons combine with holes to constitute a base current I<sub>B</sub>.

- > The remaining electrons (more than 95%) crossover into the collector region to constitute a collector current  $I_c$ .

- > Thus the base and collector current summed up give the emitter current i.e.  $I_E = (I_C + I_B)$ .

- This collector current is also called as injected current because this current is produced due to electrons injected from the emitter region.

- There is also another component of collector current due to thermally generated carriers. This is called reverse saturation current and is quite small.

- The equation gives the fundamental relationship between the currents in a bipolar transistor circuit.

- Also, this fundamental equation shows that there are current amplification factors  $\alpha$  and  $\beta$  in common base transistor configuration and common emitter transistor configuration respectively for the static (d.c) currents, and for small changes in the currents.

#### **Large** – signal current gain ( $\alpha$ ):

The large signal current gain of a common base transistor is defined as the ratio of the negative of the collector – current increment to the emitter – current change from cut off ( $I_E=0$ ) to  $I_E$ , i.e.

$$\alpha = -\frac{\left(I_{c} - I_{CBO}\right)}{I_{E} - 0}$$

where  $I_{CBO}$  (or  $I_{CO}$ ) is the reverse saturation current flowing through the reverse biased collector – base junction. i.e. the collector to base leakage current with emitter open.

As the magnitude of  $I_{CBO}$  is negligible when compared to  $I_E$ , the above expression can be written as

$$\alpha = \frac{I_{c}}{I_{E}}$$

- > Since  $I_C$  and  $I_E$  are flowing in opposite directions,  $\alpha$  is always positive.

- > Typical value of  $\alpha$  ranges from 0.90 to 0.995.

- > Also,  $\alpha$  is not a constant but varies with emitter current I<sub>E</sub>, collector voltage V<sub>CB</sub> and the temperature.

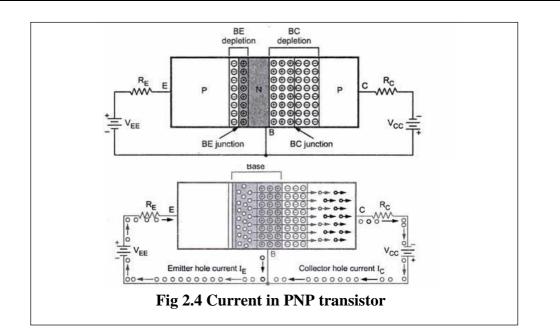

#### **Operation of PNP transistor:**

- As shown in fig.2.4 the forward bias applied to the emitter- base junction of a PNP transistor causes a lot of hoses from the emitter regions to cross over to the base region as the base is lightly doped with N-type impurity.

- > The number of electrons in the base regions is very small and hence the number of holes combined with electrons in the N type base region is also very small. Hence a few holes combined with electrons to constitute a base current  $I_B$ .

- The remaining holes (more than 95%) cross over in to the collector region to constitute a collector current  $I_C$ . Thus the collector and base current when summed up gives the emitter current. I.e.  $I_E = (I_C + I_B)$ .

- > In the external circuit of the PNP bipolar junction transistor, the magnitudes of the emitter current  $I_E$ , the base current  $I_B$  and the collector current  $I_C$  are related by

$$I_E = I_C + I_B$$

7

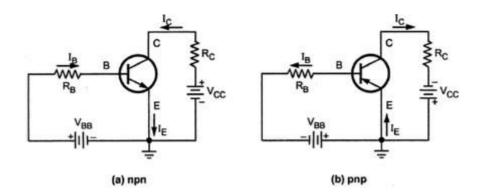

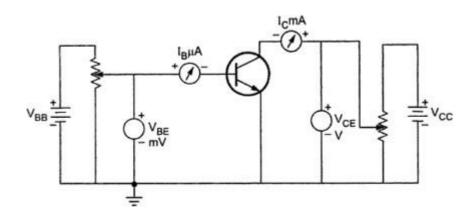

2. Explain the input and output of a transistor in CE configuration. Discuss the parameters and various regions involved in it.[Nov/Dec 2014]

The input is applied between base and emitter, and output is taken from collector and emitter. Here the emitter of transistor is common to both input and output circuits and hence the name common emitter configuration.

Here,

$$I_c = \beta_{dc}I_B + [1+\beta_{dc}]I_{CBO}$$

where  $\beta_{dc} = \frac{\alpha_{dc}}{1-\alpha_{dc}}$

The term " $(\beta_{dc}+1)I_{CBO}$ " is the **reverse leakage current** in common-emitter

configuration. It is designated as  $I_{CEO}$

$I_{CEO} = (\beta_{dc}+1)I_{CBO}$

Neglecting  $I_{CBO}$  we have

$I_C = \beta_{dc}I_B$  and  $I_E = I_B + I_C = (1+\beta_{dc})I_B$

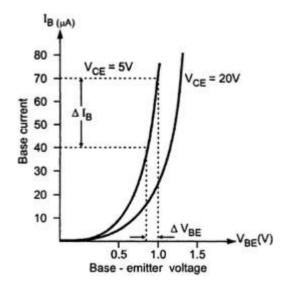

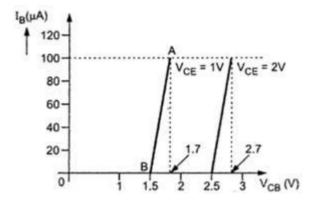

Input Characteristic:

- The curve between input current I<sub>B</sub> and input voltage V<sub>BE</sub> at constant collector emitter voltage V<sub>CE</sub>.

- After the cut in voltage the base current increases rapidly with small increase in base emitter voltage. It means the dynamic input resistance is small in CE configuration.

- > It is the ratio of change in emitter to base voltage ( $\Delta V_{BE}$ ) to the corresponding change in emitter current ( $\Delta I_B$ ) for a constant collector to base voltage ( $V_{CE}$ ).

$$R_{i} = \frac{\Delta V_{BE}}{\Delta I_{B}} \text{ at constant } V_{CE}$$

- > For a fixed value of  $V_{BE}$ , base current decreases as  $V_{CE}$  is increased. A larger value of  $V_{CE}$  results in large reverse bias at collector base p-n junction.

- This reduces the depletion region and reduces the effective width of the base. Hence there are fewer recombination in the base region reducing the base current.

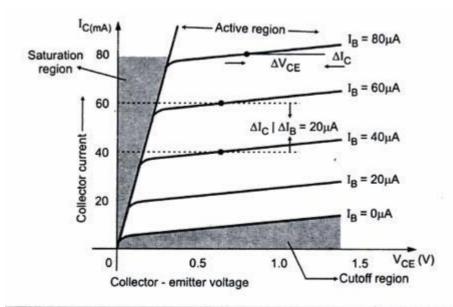

## **Output characteristics:**

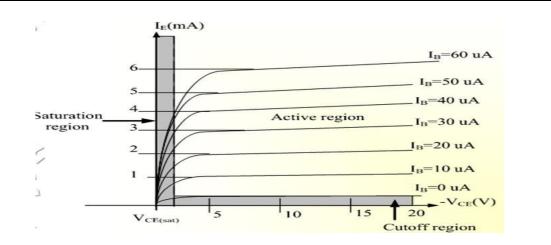

Fig. 5.28 Output characteristics of the transistor in CE configuration

2. The value of  $\beta$  of the transistor can be found at any point on the characteristics by taking the ratio I<sub>C</sub> to I<sub>B</sub> at that point, i.e.  $\beta = \beta_{dc} = \frac{I_C}{I_B}$ . This is known as DC beta

for the transistor. For a fixed value of  $V_{CE}$ , if we take the ratio of small change in  $I_C$ ,  $\Delta I_C$  to small change in  $I_B$ ,  $\Delta I_B$ , we get AC beta;

$$\beta_{ac} = \frac{\Delta I_C}{\Delta I_B} \bigg|_{\Delta V_{CE} = 0} \qquad \dots (5.19)$$

Generally dc and ac values of beta of the transistor are nearly equal.

3. From the output characteristics we can see that change in collector-emitter voltage ( $\Delta V_{CE}$ ) causes the little change in the collector current ( $\Delta I_C$ ) for constant base current  $I_B$ . Thus the output dynamic resistance is high in CE configuration.

$$r_{o} = \frac{\Delta V_{CE}}{\Delta I_{C}}\Big|_{I_{B} = \text{constant OR } \Delta I_{B} = 0} \qquad \dots (5.20)$$

The output characteristics of common emitter configuration consists of three regions : Active, Saturation, and Cut-off.

#### (1) Active Region:

Active region : The region where the curves are approximately horizontal is the "active" region of the CE configuration. In the active region, the collector junction is reverse biased. As  $V_{CE}$  is increased, reverse bias increases. This causes depletion region to spread more in base than in collector, reducing the chances of recombinations in the base. This increases the value of  $\alpha$ .

> If  $\alpha_{dc}$  is truly constant then I<sub>C</sub> would be independent of V<sub>CE</sub>.

- > But because of early effect,  $\alpha_{dc}$  increases by 0.1% (0.001) e.g. from 0.995 to 0.996 as  $V_{CE}$  increases from a few volts to 10V. Then  $\beta_{dc}$  increases from 0.995 / (1-0.995) = 200 to 0.996 / (1-0.996) = 250 or about 25%.

- This shows that small change in a reflects large change in b. Therefore the curves are subjected to large variations for the same type of transistors.

## (2) Cut Off:

> Cut off in a transistor is given by  $I_B = 0$ ,  $I_C = I_{CO}$ . A transistor is not at cut off if the base current is simply reduced to zero (open circuited) under this condition,

$$I_{\rm C} = I_{\rm E} = I_{\rm CO} / (1 - \alpha_{\rm dc}) = I_{\rm CEO}$$

- > The actual collector current with base open is designated as  $I_{CEO}$ . Since even in the neighborhood of cut off, a <sub>dc</sub> may be as large as 0.9 for Ge, then  $I_C=10 I_{CO}$ (approximately), at zero base current.

- Accordingly in order to cut off transistor it is not enough to reduce  $I_B$  to zero, but it is necessary to reverse bias the emitter junction slightly. It is found that reverse voltage of 0.1 V is sufficient for cut off a transistor. In Si, the  $\alpha_{dc}$  is very nearly equal to zero, therefore,  $I_C = I_{CO}$ .

- → Hence even with  $I_B = 0$ ,  $I_C = I_E = I_{CO}$  so that transistor is very close to cut off. In summary, cut off means  $I_E = 0$ ,  $I_C = I_{CO}$ ,  $I_B = -I_C = -I_{CO}$ , and  $V_{BE}$  is a reverse voltage whose magnitude is of the order of 0.1 V for Ge and 0 V for Si.

- > In this region both the junctions of the transistor are reverse biased.

## (3)Saturation Region:

- If V<sub>CE</sub> is reduced to a small value such as 0.2V, then collector base junction becomes forward biased ,since the emitter base junction is already F.B by 0.7V. When both the junctions are forward biased the transistor operates in this region and the value ranges between 0.1 V to 03 V.

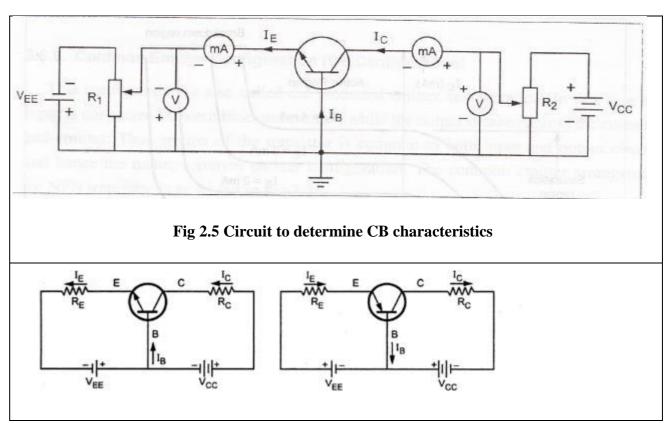

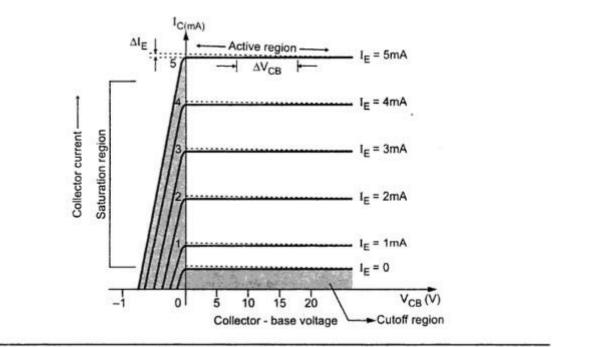

- **3.** Explain the input and output of a transistor in CB configuration. Discuss the parameters and various regions involved in it.

- > This configuration is also called as grounded base configuration.

- In this case the input is connected between the emitter and base while the output is taken across the collector and base.

- Thus the base of the transistor is common to both input and output circuits and hence the name, common base configuration. The common base circuit arrangement for NPN transistors is shown in Fig.2.5

**Current Amplification Factor (α):**

The current amplification factor is defined as the ratio of changes in Collector current ( $\Delta I_C$ ) to the change in emitter current ( $\Delta I_E$ ) when the collector to base voltage (V<sub>CB</sub>) is maintained at a constant value.

$$\alpha = (\Delta I_C) / (\Delta I_E)$$

(at constant V<sub>CB</sub>)

The value of  $\alpha$  is always less than unity. The practical value of transistors lies between 0.95 and 0.99.

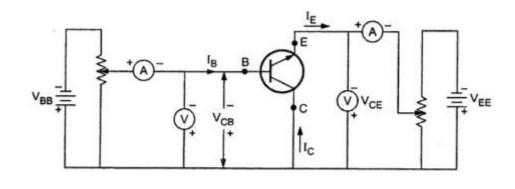

The circuit arrangement for determining the characteristics of a common base NPN transistors is shown in Fig 2.5.In this circuit, the collector to base voltage ( $V_{CB}$ ) can be varied by adjusting the potentiometer  $R_2$ . The emitter to base voltage ( $V_{EB}$ ) can be varied by adjusting the potentiometer  $R_1$ . The DC voltmeters and DC milliammeters are connected in the emitter and collector circuits to measure the voltages and currents

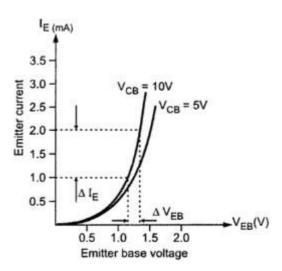

## 1. Input Characteristics:

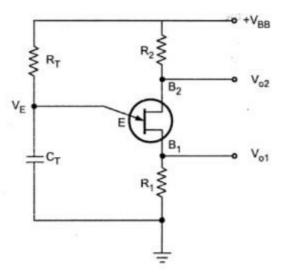

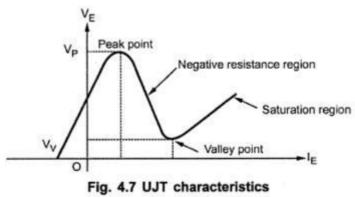

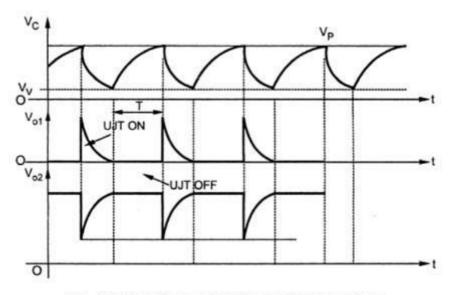

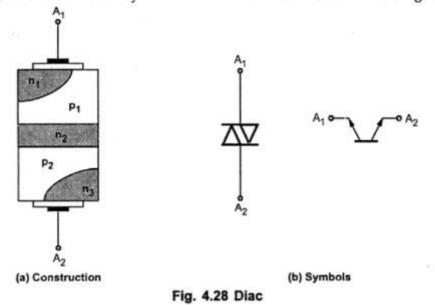

The curves plotted between the emitter current  $(I_E)$  and the emitter to base voltage  $(V_{EB})$  at constant collector to base voltage  $(V_{CB})$  are known as input characteristics of a transistor in common base configuration.