#### **BM T45 – LINEAR INTEGRATED CIRCUITS**

#### UNIT-1

#### PART - A

#### 1. List the advantage of integrated circuits over discrete component. (May 2014)

- > Practically size of an IC is thousands of times smaller than the discrete circuits.

- ➢ ICs operate at low voltages.

- > The cost of IC is very less

- > The power consumption is less

#### 2. What are the two main process of photolithography? (May 2014)

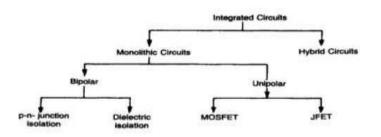

- Making of a photographic mask

- Photo etching

#### 3. a) What is the advantage of dry itching? (Nov 2014)

#### b) What are the advantage of plasma etching? (May 2017)

- Eliminates handling of dangerous acids and solvents

- Uses small amounts of chemicals

- Isotropic or anisotropic etch profiles

- No unintentional prolongation of etching

- Better process control

- Ease of automation (e.g., cassette loading)

- 4. Design an amplifier with a gain of +5 using op-amp. (Nov 2014)

$A_{\rm CL} = 1 + R_{\rm f}/R_1$   $5 = 1 + R_{\rm f}/10 \text{ k}\Omega$  $R_{\rm f} = 4 \times 10 \text{ k}\Omega = 40 \text{ k}\Omega$

# 5. Write down the various processes used to fabricate IC's using silicon planar technology.(Nov 2015)

- Silicon wafer preparation

- ➢ Epitaxial growth

- ➢ Oxidation

- Photolithography

- ➢ Diffusion

- ➢ Ion implantation

- ➢ Isolation

- ➢ Metallization

- Assembly processing and packaging

# 6. List out the ideal characteristics of an Op-amp. (Nov 2015, Nov 2016, May 2018, May 2019, Sep 2020)

- > Infinite open-loop gain  $G = v_{out} / v_{in}$

- Zero input offset voltage

- Infinite output voltage range

- Zero output impedance Rout

- Zero noise

- Infinite common-mode rejection ratio(CMRR)

- > Infinite power supply rejection ratio.

#### 7. List the advantage of ion implantation. (Nov 2016)

- > The impurity concentration is highly uniform typically within 1%, over the wafer

- > The degree of uniformity is maintained same form wafer to wafer

- > The layer can be formed anywhere within substrate

- > The lateral spread is very small

#### 8. Explain why inductors are difficult to fabricate in IC's. (May 2017)

- The property of inductor or inductance is that it would create flux lines or magnetic field around the line of conductor.

- The fabricated components in the integrated circuitry are very much susceptible to those flux lines and vulnerable to malfunctioning. This leads to gross failure of the IC.

#### 9. Bring out the classification of IC's. (Nov2017)

### 10. Design an amplifier with a gain of -10 and input resistance equal to 10 kilo ohm. (Nov2017)

$$R_1 = 10 \text{ k}\Omega$$

$$R_f = -A_{\text{CL}} R_1$$

$$= -(-10) \times 10 \ k\Omega = 100 \ k\Omega$$

#### 11. Give the difference between monolithic and hybrid IC's. (May 2018)

| Monolithic ICs                           | Hybrid ICs                                          |

|------------------------------------------|-----------------------------------------------------|

| Monolithic integrated circuits are       | Hybrid integrated circuits are fabricated by inter- |

| fabricated entirely on a single chips.   | connecting a number of individual chips.            |

| Small in size as compared to hybrid ICs  | Large in size as compared to monolithic ICs         |

| Monolithic ICs are expensive.            | Hybrid ICs are less expensive.                      |

| Speed is high as compared to hybrid ICs. | Speed is low as compared to monolithic ICs.         |

#### 12. What is meant by parasitic capacitance? (Nov 2018)

Parasitic capacitance, or stray capacitance is an unavoidable and usually unwanted capacitance that exists between the parts of an electronic component or circuit simply because of their proximity to each other.

#### 13. Name the different types of IC packages. (May 2019)

- Metal can package

- Dual-in-line package

- Ceramic flat package

#### 14. State the limitations of IC technology. (Sep 2020)

- Some components like transformers and inductors cannot be integrated into an IC.

- ➤ High grade P-N-P assembly is not possible.

- > It is difficult to achieve low temperature coefficient.

- > It is difficult to fabricate an IC with low noise.

- > There is a large value of saturation resistance of transistors.

#### PART – B

#### 1. Explain in detail the AC characteristics of an Op-amp. (May 2014, Nov 2015)

Ac characteristics:

For small signal sinusoidal applications the a.c. characteristics are

1. Frequency response 2. Slew rate

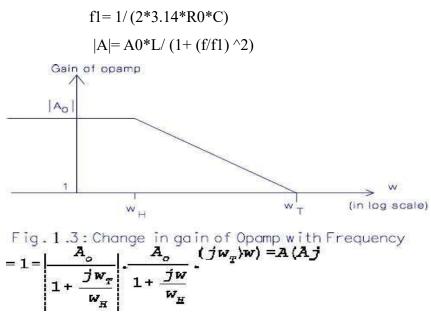

#### **<u>1. Frequency response:</u>**

- An ideal op-amp has infinite band width that is open loop gain is 90dB with d.c. signal and this gain should remain the same through audio and radio frequency.

- But practically op-amp gain decreases at high frequency. This is due to a capacitive component in the equivalent circuit of op-amp.

- Due to R0C, the gain decreases by 20 dB per decay and the frequency is said to be brake or corner frequency and is given by

#### 2. Slew rate:

The rate of change of output voltage due to the step input voltage and is usually specified as V/micro sec.

For example: 1V/micro sec. slew rate denotes the output rises or falls by 1 volts in 1 micro seconds.

The rate at which the voltage across the capacitor dVc/dt is given by

$$dVc/dt = I/C$$

Slew rate SR dVc/dt|max = Imax/C

#### For IC741

Imax= 15 micro amps, C= 30 Pico farad

Slew rate = 0.5V/micro sec.

2.a) Explain the operation of differential amplifier. (May 2014)

b) Explain the modes of operation of operational amplifier. (Nov 2014)

c) Compare the different modes of operational amplifier. (May 2017)

d) Draw the circuit diagram of an Op-amp differential mode and derive an expression for tile output in terms of the input. (May 2018)

e) Draw the circuits for inverting, non-inverting and difference amplifier using Opamp. Derive an expression for gain for these three configurations. (May 2019, Sep 2020)

f) With neat circuit diagram, explain the working of inverting amplifier and obtain an expression for its gain. (Nov 2018)

g) Sketch the equivalent circuit diagram of an ideal operational amplifier and state its characteristics.

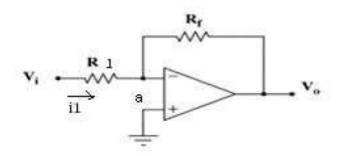

#### Inverting Amplifier:

- In Fig output voltage  $v_0$  is fed back to the inverting input terminal through the  $R_f$ - $R_1$  network where  $R_f$  is the feedback resistor.

- Input signal v<sub>i</sub> is applied to the inverting input terminal through R<sub>1</sub> and non-inverting input terminal of op-amp is grounded.

Fig. Inverting Amplifier Circuit

$$\frac{Va - Vi}{Ri} + \frac{Va - Vo}{Rt} = 0$$

$$\frac{Ri}{Ri} + \frac{O - Vo}{Rt} = 0$$

$$\frac{O - Vi}{Ri} + \frac{O - Vo}{Rt} = 0$$

$$\frac{Vi}{Ri} + \frac{Vo}{Rt} = 0$$

$$\frac{Vo}{Rt} = \frac{-Vi}{Rt}$$

$$\frac{Vo}{Rt} = \frac{-Vi}{Ri}$$

$$\frac{Vo = -\frac{Rt}{Ri}}{Ri}$$

$$\frac{Vo = -\frac{Rt}{Ri}}{Ri}$$

$$\frac{Vo = -\frac{Rt}{Ri}}{Ri}$$

$$\frac{Vo = -\frac{Rt}{Ri}}{Ri}$$

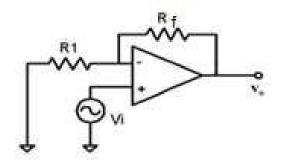

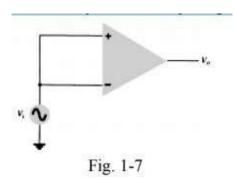

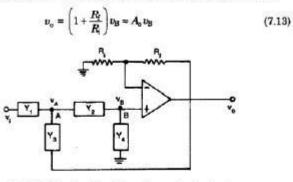

#### Non inverting amplifier:

- If a signal is applied to the non-inverting input terminal and feed back is given as shown in Fig the circuit amplifies without inverting the input signal. Such a circuit is called non-inverting amplifier.

- It may also be noted that it is also a negative feed-back system as output is being fed back to the inverting input terminal

Fig. Non-Inverting Amplifier Circuit

$$V_{i} = \frac{V_{0}}{R_{i} + R_{b}} R_{i}$$

$$\frac{V_{0}}{V_{i}} = \frac{R_{i} + R_{b}}{R_{i}} = \frac{R_{i}}{R_{i}} + \frac{R_{b}}{R_{i}}$$

$$\frac{V_{0}}{V_{i}} = 1 + \frac{R_{b}}{R_{i}}$$

$$\frac{V_{0}}{V_{i}} = 1 + \frac{R_{b}}{R_{i}}$$

$$\frac{V_{0}}{R_{i}} = 1 + \frac{R_{b}}{R_{i}}$$

$$\frac{V_{0}}{R_{i}} = 1 + \frac{R_{b}}{R_{i}}$$

• As the differential voltage vd at the input terminal of op-amp is zero, the voltage at node 'a' is v<sub>i</sub>, same as the input voltage applied to non-inverting input terminal.

#### <u>Voltage follower</u>

$$R_{f} = 0$$

$R_{i} = \infty$

$V_{0} = V_{i}$

#### <u>Differential amplifier</u>

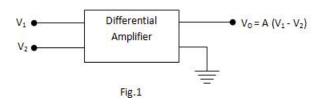

A differential amplifier is a circuit that can accept two input signals and amplify the difference between these two input signals.

Fig.shows the block diagram of a differential amplifier .

There are two input voltages  $v_1$  and  $v_2$ .

The nodal equation of a' a

$$\frac{Va - V_3}{R_1} + \frac{Va - Ve}{R_2} = 0$$

$$\frac{Va}{R_1} - \frac{Vs}{R_1} + \frac{Va}{R_2} - \frac{Vo}{R_2} = 0$$

$$Va \left(\frac{Ve_1 + Ve_3}{R_1} - \frac{Ve_3}{R_1} - \frac{Vo}{R_2} = 0$$

$$\int a \left(\frac{Ve_1 + Ve_3}{R_1} - \frac{Ve_3}{R_2} - \frac{Ve_3}{R_1} - \frac{Ve_3}{R_2} - \frac{Ve_3}{R_2} - \frac{Ve_3}{R_1} - \frac{$$

$$V_0 = A_1 V_1 + A_2 V_2$$

Since

$$V_{CM} = \frac{(V_1 + V_2)}{2} - 0$$

$$V_d = V_1 - V_2 - 0$$

$$(0) \implies V_1 + V_2 = 2V_{CM}$$

$$(0) \implies V_1 + V_2 = 2V_{CM} + V_d$$

$$\boxed{V_1 = V_{CM} + V_d}$$

$$\boxed{V_1 = V_{CM} + \frac{V_d}{2}}$$

Sub, V, Value in equ (2)

$$V_d = V_{CM} + \frac{V_d}{2} - V_2$$

$$\boxed{V_2 = V_{CM} - \frac{V_d}{2}}$$

Sub the value of V\_1 + V\_2 in Va

$$V_0 = B_1 V_1 + B_2 V_2$$

$$= B_1 \left(V_{CM} + \frac{V_d}{2}\right) + B_2 \left(V_{CM} - \frac{V_d}{2}\right)$$

$$= V_{CM} \left(B_1 + B_2\right) + \frac{V_d}{2} \left(B_1 - B_2\right)$$

$$\boxed{V_0 = V_{CM} + V_d + V_d + D_M}$$

where  $B_{CM} = B_1 + B_2$

This amplifier amplifies the difference between the two input voltages.

Therefore the output voltage is,

$$v_o = A(v_1 - v_2)$$

Where A is the voltage gain of the amplifier.

Operation of Differential Amplifier

For simplicity, we shall discuss the operation of single-ended input and double-ended outputDA.

Case – 1:

Suppose the signal is applied to input 1 (i.e. base of transistor  $Q_1$ ) and input 2(i.e.base of transistor  $Q_2$ ) is grounded as shown in fig

The transistor  $Q_1$  will act in two ways: as a common emitter amplifier and as a common collector amplifier.

As a common emitter amplifier, the input signal to  $Q_1$  will appear at output 1 (i.e. collector of  $Q_1$ ) as amplified inverted signal.

As a common collector amplifier, the signal appears on the emitter of  $Q_1$  in phase with the input and only slightly smaller.

Since the emitters of Q1 and Q2 are common, the emitter signal becomes input to Q2. Therefore,

$Q_2$  functions as a common base amplifier.

As a result, the signal on the emitter  $Q_2$  will be amplified and appears on output 2 (i.e. collector of  $Q_2$ ) in phase with the emitter signal and hence in phase with the input signal (signal at input 1).

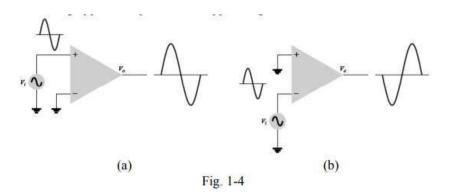

The differential amplifier exhibits three modes of operation based on the type of input (and/or output) signals. These modes are **single-ended**, **double-ended or differential**, **and common**. Since the differential amplifier is the input stage of the op-amp, the op-amp exhibits the same modes

**Single-Ended Input:** Single-ended input operation results when the input signal is connected to one input with the other input connected to ground. Fig. 1-4 shows the signals connected for this operation. In Fig. 1-4(a), the input is applied to the plus input (with minus input at ground), which results in an output having the same polarity as the applied input signal. Fig. 1-4(b) shows an input signal applied to the minus input, the output then being opposite in phase to the applied signal.

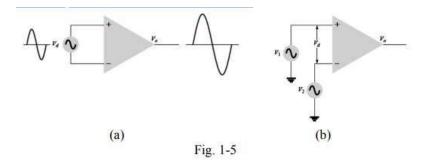

**Double-Ended (Differential) Input:** In addition to using only one input, it is possible to apply signals at each input-this being a double-ended operation. Fig. 1-5(a) shows an input, Vd, applied between the two input terminals (recall that neither input is at ground), with the resulting amplified output in phase with that applied between the plus and minus inputs. Fig. 1.5(b) shows the same action resulting when two separate signals are applied to the inputs, the difference signal being Vi1 – Vi2.

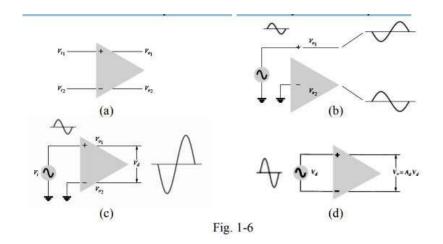

**Double-Ended Output:** While the operation discussed so far had a single output, the op-amp can also be operated with opposite outputs, as shown in Fig. 1-6(a). An input applied to either input will result in outputs from both output terminals, these outputs always being opposite in polarity. Fig. 1-6(b) shows a single-ended input with a doubleended output. As shown, the signal applied to the plus input results in two amplified outputs of opposite polarity. Fig. 1-6(c) shows the same operation with a single output measured between output terminals (not with

respect to ground). This difference output signal is Vo1 - Vo2. The difference output is also referred to as a floating signal since neither output terminal is the ground (reference) terminal. Notice that the difference output is twice as large as either Vo1 or Vo2 since they are of opposite polarity and subtracting them results in twice their amplitude. Fig. 1-6(d) shows a differential input, differential output operation. The input is applied between the two input terminals and the output taken from between the two output terminals. This is fully differential operation.

**Common-Mode Operation:** When the same input signals are applied to both inputs, commonmode operation results, as shown in Fig. 1-7. Ideally, the two inputs are equally amplified, and since they result in opposite polarity signals at the output, these signals cancel, resulting in 0-V output. Practically, a small output signal will result.

**Common-Mode Rejection:** A significant feature of a differential connection is that the signals which are opposite at the inputs are highly amplified, while those which are common to the two inputs are only slightly amplified-the overall operation being to amplify the difference signal while rejecting the common signal at the two inputs. Since noise (any unwanted input signal) is generally common to both inputs, the differential connection tends to provide

attenuation of this unwanted input while providing an amplified output of the difference signal applied to the inputs. This operating feature, referred to as common-mode rejection.

#### 2. a) Explain the fabrication of a typical circuit with neat sketch. (Nov 2014, Nov 2017)

b) Explain the basic process used in silicon planar technology with neat diagram. (Nov 2015, May 2018, Nov2018)

#### c) Describe the epitaxial growth process employed in IC fabrication. (Nov 2016)

The basic processes used to fabricate ICs using silicon planar technology can be categorised as follows:

- 1. Silicon wafer (substrate) preparation

- 2. Epitaxial growth

- 3. Oxidation

- 4. Photolithography

- 5. Diffusion

- 6. Ion implantation

- 7. Isolation technique

- 8. Metallization

- 9. Assembly processing and packaging

We shall now describe these processes in detail

#### 1. Silicon wafer Preparation

The following steps are used in the preparation of Si-wafers

- 1. Crystal growth and doping

- 2. Ingot trimming and grinding

- 3. Ingot slicing

- 4. Wafer polishing and etching

- 5. Wafer cleaning

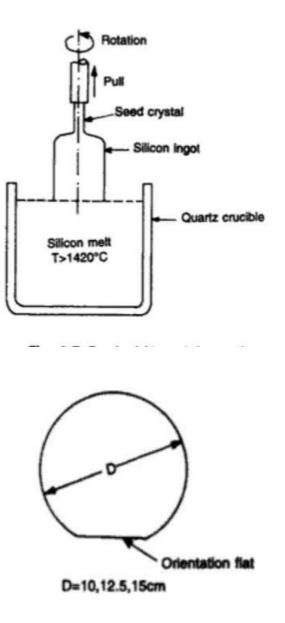

The starting material for crystal growth is highly purified (99.99999) polycrystalline silicon. The Czochralski crystal growth process is the most often used for producing single crystal silicon ingots. The polycrystalline silicon together with an appropriate amount of dopant is put in a quartz crucible and is then placed in a furnace. The material is then heated to a temperature in excess of the silicon melting point of 1420°C. A small single crystal rod of silicon called a seed crystal is then dipped into the silicon-melt and slowly pulled out as shown in Fig. 1.5. As the seed crystal is pulled out of the melt, it brings with it a solidified mass of silicon with the same crystalline structure as that of seed crystal. During the crystal pulling process, the seed crystal and the crucible are rotated in opposite directions in order to produce ingots of circular cross-section. The diameter of the ingot is controlled by the pulling rate and the melt temperature. Ingot diameter of about 10 to 15 cm is common and ingot length is generally of the order of 100 cm.

Fig. 1.6 Silicon wafer, D = 10, 12.5, 15 cm showing flat orientation

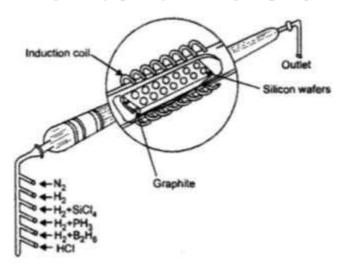

#### 2. Epitaxial growth

The word epitaxy is derived from Greek word *epi* meaning 'upon' and the past tense of the word *teinon* meaning 'arranged'. So, one could describe epitaxy as, arranging atoms in single crystal fashion upon a single crystal substrate, so that the resulting layer is an extension of the substrate crystal structure.

The basic chemical reaction used for the epitaxial growth of pure silicon is the hydrogen reduction of silicon tetrachloride.

$$SiC_4 + 2H_2 \xrightarrow{1200^{\circ}C} Si + 4HCl$$

Mostly, epitaxial films with specific impurity concentration are required. This is accomplished by introducing phosphine (PH<sub>3</sub>) for the *n*-type and bi-borane ( $B_2H_6$ ) for *p*-type doping into the silicontetrachloride hydrogen gas stream.

3. Oxidation

- SiO<sub>2</sub> is an extremely hard protective coating and is unaffected by almost all reagents except hydrofluoric acid. Thus it stands against any contamination.

- 2. By selective etching of  $SiO_2$ , diffusion of impurities through carefully defined windows in the  $SiO_2$  can be accomplished to fabricate various components.

- 4. Photolithography

However, with the advent of latest technology using X-ray or electron beam lithographic techniques, it has become possible to produce device dimension down to submicron range (< 1  $\mu$ m).

Photolithography involves two processes, namely: Making of a photographic mask Photo etching

#### 5. Diffusion

Another important process in the fabrication of monolithic ICs is the diffusion of impurities in the Silicon chip. This uses a high temperature furnace having a flat temperature profile over a useful length (about 20" length). A quartz boat containing about 20 cleaned wafers is pushed into the hot zone with temperature maintained at about a 1000°C.

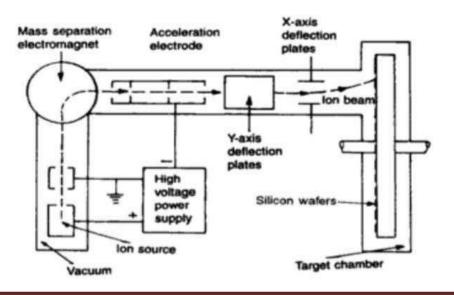

#### 6. Ion implantation

- 1. It is performed at low temperatures. Therefore, previously diffused regions have a lesser tendency for lateral spreading.

- In diffusion process, temperature has to be controlled over a large area inside the oven, whereas in ion implantation technique, accelerating potential and the beam current are electrically controlled from outside.

#### 7. Isolation Techniques

Since a number of components are fabricated on the same IC chip, it becomes necessary to provide electrical isolation between different components and interconnections. Various types of isolation techniques have been developed. However, we shall discuss here only two commonly used techniques namely:

pn junction isolation Dielectric isolation

8. Metallization

The purpose of this process is to produce a thin metal film layer that will serve to make interconnections of the various components on the chip. Aluminium is usually used for the metallization of most ICs as it offers several advantages.

- 1. It is relatively a good conductor.

- 2. It is easy to deposit aluminium films using vacuum deposition.

- 3. Aluminium makes good mechanical bonds with silicon.

- Aluminium forms low resistance, non-rectifying (i.e. ohmic) contact with p-type silicon and the heavily doped n-type silicon.

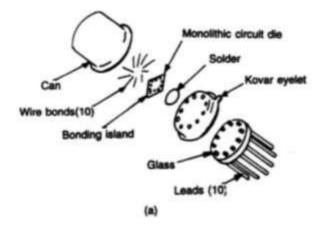

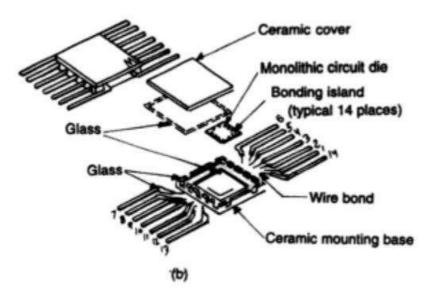

9. Assembly processing and packaging

There are three different package configurations available.

- 1. TO-5 glass metal package

- 2. Ceramic flat package

- 3. Dual-in-line (ceramic or plastic type)

TO-5 packages are available in 8, 10 or 12 leads, whereas the flat or dual-in-line package is commonly available in 8, 14 or 16 leads, but

- 3. a.List the DC characteristics of an Op-amp.

- b. Write short notes on the following non-ideal DC characteristics with necessary circuit diagrams and expressions. (Nov 2017)

- a) Input offset current

- b) Input offset voltage

#### **DC Characteristics:**

- An ideal op-amp draws no current from source and its response is independent of temperature.

- Practical op-amp has some dc voltage at the output even with both the inputs are grounded.

- The non-ideal dc characteristics that add error components to the dc output voltage are

- a. Input bias current

- b. Input offset voltage

- c. Input offset current

- d. Thermal drift

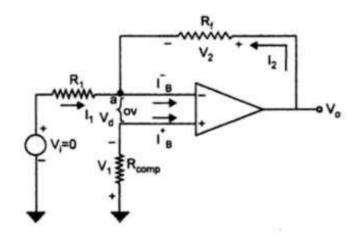

#### Input bias current:

- Ideal op-amp draws no current from the input terminal.

- A practical op-amp conducts a small value of dc current to bias the input transistors.

- In fig 1.1,the base current entering into the inverting and non-inverting terminals are I  $_{\bar{B}}$  and  $I_{B^+}$  respectively.  $I_{B^-}$  and  $I_{B^+}$  are not exactly equal due to internal imbalance between the two inputs.

Fig 1.1 Input bias current and Bias current compensation

• Input bias current  $I_B$  is defined as the average value of the base currents entering into the terminals of an op-amp during the input bias current.

IB=IB++IB-2(1.1)

It is compensated by Rcomp=  $R1 \parallel R2$  between non inverting terminal and ground

R1RFR1+RF=RCOMP (1.2)

#### Input offset current:

- Bias current compensation will work efficiently if both the bias currents  $I_B$  <sup>+</sup> and  $I_B$  <sup>-</sup> are equal.

- The input transistors cannot be made identical hence there will be some difference between I<sub>B</sub><sup>+</sup> and I<sub>B</sub><sup>-</sup>. This difference is called offset current I<sub>OS</sub>.

IOS = IB + - IB + (1.3)

• The absolute value indicates that there is no way to predict which of the current is large

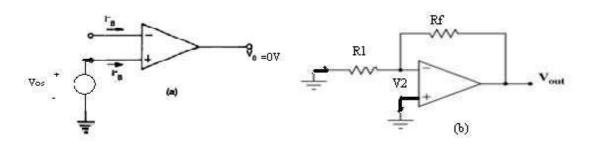

#### Input offset voltage

- It is defined as the differential DC voltage required between the inputs of an amplifier, especially an operational amplifier (op-amp), to make the output zero

- This occurs due to unavoidable imbalances inside the op-amp .

Fig 1.2 a) Op-amp showing input and output offset voltage b) Equivalent circuit for Vi=0

By voltage divider rule V2 is given by,

| Vo=(R1.+Rf) V2(R1.) | (1.5) |

|---------------------|-------|

|---------------------|-------|

Vo=1+Rf.R1.V2. (1.6)

Vos=V1-V2 (1.7)

We know that,  $V_1=0$

Vos=0 - V2

$Vos=V2 \tag{1.8}$

Therefore to make input offset voltage to be zero  $Vos=V_2$

#### Thermal drift:

- Thermal drift is defined as the average rate of change of input offset voltage or offset current or bias current per unit change in temperature

- Bias current, offset current and offset voltage change with temperature. .

- Offset current drift is expressed in  $nA/^{0}C$  and offset voltage drift in  $mV/^{0}C$ .

- For the 741c, the input resistance is 2Mohms.

#### Output Voltage Swing

The output voltage swing between -13V to +13V

#### 4. a) Explain how a diode, a resistor and a capacitor are fabricated in IC.(Nov 2016)

#### b) Explain how a monolithic capacitor can be fabricated.( Nov 2019)

#### c) Explain the fabrication of a typical circuit with neat sketch. (Nov 2014, Nov 2017)

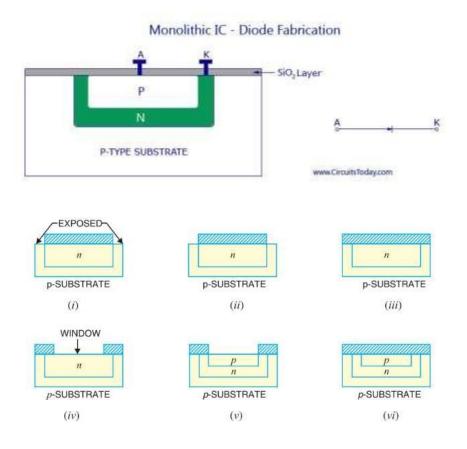

#### Diodes

They are also fabricated by the same diffusion process as transistors are. The only difference is that only two of the regions are used to form one P-N junction. In figure, collector-base junction of the transistor is used as a diode. Anode of the diode is formed during the base diffusion of the transistor and the collector region of the transistor becomes the cathode of the diode. For high speed switching emitter base junction is used as a diode.

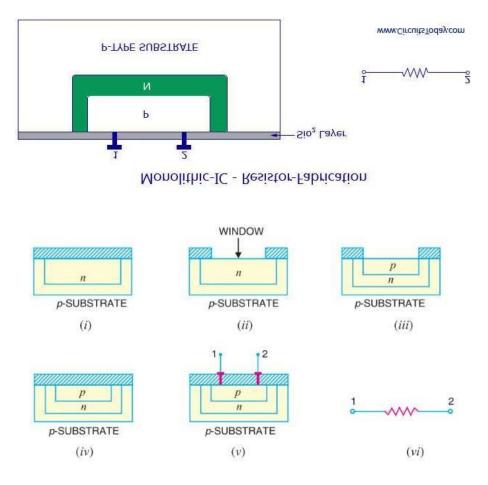

#### Resistors

The resistors used in IC's are given their respective ohmic value by varying the concentration of doping impurity and depth of diffusion. The range of resistor values that may be produced by the diffusion process varies from ohms to hundreds of kilohms. The typical tolerance, however, may be no better than  $\pm$  5%, and may even be as high as  $\pm$  20%. On the other hand, if all the resistors are diffused at the same time, then the tolerance ratio may be good. Most resistors are formed during the base diffusion of the integrated transistor, as shown in figure below. This is because it is the highest resistivity region. For low resistance values, emitter region is used as it has much lower resistivity.

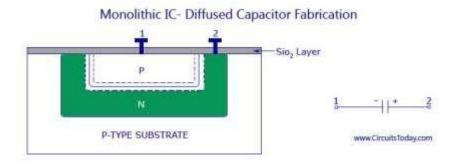

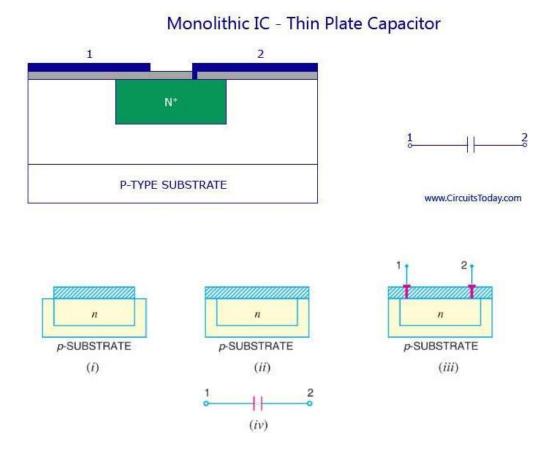

#### Capacitors

The figure below shows the P and N-regions forming the capacitor plates. The dielectric of the capacitor is the depletion region between them.

All P-N junctions have capacitance so capacitors may be produced by fabricating junctions. The amount of change in the reverse bias varies the value of junction capacitance and also the depletion width. The value may be as less as 100 picoFarads.

Using the silicon dioxide as a dielectric may also be a way to fabricate capacitors. One plate of the capacitors is formed by diffusing a heavily doped N-region. The other plate of the capacitor is formed by depositing a film of aluminium on the silicon dioxide dielectric on the wafer surface. For such a capacitor, a voltage of any polarity can be used, and when comparing a diffused capacitor with such a capacitor the diffused capacitor may have very small values of breakdown voltage.

#### 5. Describe briefly about the fabrication methods for transistors and diodes. (May 2017)

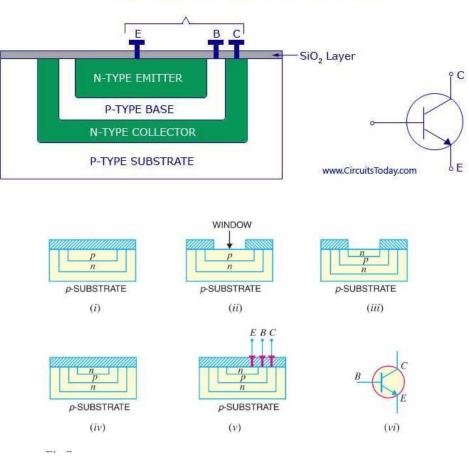

#### Transistors

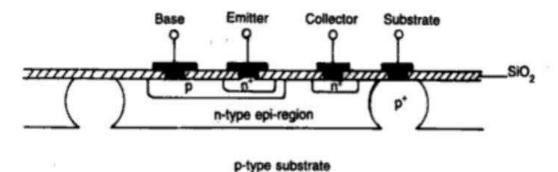

The fabrication process of a transistor is shown in the figure below. A P-type substrate is first grown and then the collector, emitter, and base regions are diffused on top of it as shown in the figure. The surface terminals for these regions are also provided for connection.

Monoilithic IC - Transistor Fabrication

Both transistors and diodes are fabricated by using the epitaxial planar diffusion process that is explained earlier. In case of discrete transistors, the P-type substrate is considered as the collector. 'But this is not possible in monolithic IC's, as all the transistors connected on one P-type substrate would have their collectors connected together. This is why separate collector regions are diffused into the substrate.

Even though separate collector regions are formed, they are not completely isolated from the substrate. For proper functioning of the circuit it is necessary that the P-type substrate is always kept negative with respect to the transistor collector. This is achieved by connecting the

substrate to the most negative terminal of the circuit supply. The unwanted or parasitic junctions, even when reverse-biased, can still affect the circuit performance adversely. The junction reverse leakage current can cause a serious problem in circuits operating at very low current levels. The capacitance of the reverse-biased junction may affect the circuit high-frequency performance, and the junction break down voltage imposes limits on the usable level of supply voltage. All these adverse effects can be reduced to the minimum if highly resistive material is employed for the substrate. If the substrate is very lightly doped, it will behave almost as an insulator.

### 6. a) Explain the various steps utilized in converting a typical circuit into a monolithic IC. (Nov 2017)

#### b) Explain the fabrication of a typical circuit with neat sketch. (Nov 2014, Nov 2017)

#### **Monolithic IC Manufacturing Process**

For the manufacture and production of the monolithic IC, all circuit components and their interconnections are to be formed in a single thin wafer. The different processes carried out for achieving this are explained below.

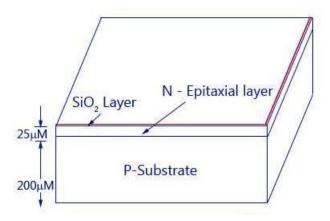

#### 1. P-layer Substrate Manufacture

Being the base layer of the IC, the P-type is silicon is first built for the IC. A silicon crystal of Ptype is grown in dimensions of 250mm length and 25mm diameter. The silicon is then cut into thin slices with high precision using a diamond saw. Each wafer will precisely have a thickness of 200 micrometer and a diameter of 25 mm. These thin slices are termed wafers. These wafers may be circular or rectangular in shape with respect to the shape of the IC. After cutting hundreds of them each wafer is polished and cleaned to form a P-type substrate layer.

#### 2. N-type Epitaxial Growth

The epitaxial groth process of a low resistive N-type over a high resistive P-type is to be carried out. This is done by placing the n-type layer on top of the P-type and heating then inside a diffusion furnace at very high temperature (nearly 1200C). After heating, a gas mixture f Silicon atoms and pentavalent atoms are also passed over the layer. This forms the epitaxial layer on the substrate. All the components required for the circuit are built on top of this layer. The layer is then cooled down, polished and cleaned.

#### 3. The Silicon Dioxide Insulation Layer

As explained above, this layer is required contamination of the N-layer epitaxy. This layer is only 1 micrometer thin and is grown by exposing the epitaxial layer to oxygen atmosphere at 1000C. A detailed image showing the P-type, N-type epitaxial layer and SiO2 layer is given below.

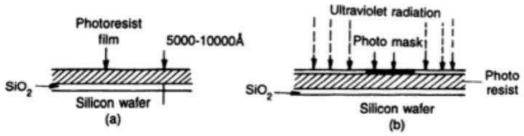

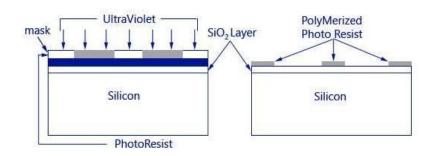

#### 4. Photolithographic Process for SiO2

To diffuse the impurities with the N-type epitaxial region, the silicon dioxide layer has to be Thus openings must etched in selected areas. be brought at these areas through photolithographic process. In this process, the SiO2 layer is coated with a thin layer of a photosensitive material called photoresist. A large black and white pattern is made in the desired patter, where the black pattern represents the area of opening and white represents the area that is left idle. This pattern is reduced in size and fit to the layer, above the photoresist. The whole layer is then exposed to ultraviolet light. Due to the exposure, the photoresist right below the white pattern becomes polymerized. The pattern is then removed and the wafer is developed using a chemical like trichloroethylene. The chemical dissolves the unpolymerized portion of the photoresist film and leaves the surface. The oxide not covered by polymerised photoresist is then removed by immersing the chip in an etching solution of HCl. Those portions of the Si02 which are protected by the photoresist remain unaffected by the acid. After the etching and diffusion process, with the help of chemical solvents like sulphuric acid, the resist mask is then removed by mechanical abrasion. The appropriate impurities are then diffused through oxide free windows.

Monolithic IC - Photolithographic Process

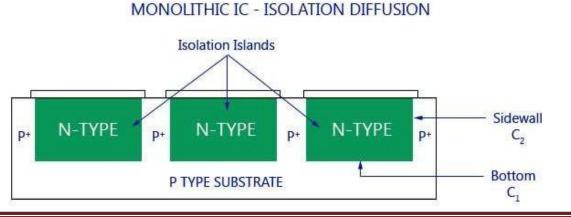

#### 5. Isolation Diffusion

After photolithographic process the remaining SiO2 layer serves as a mask for the diffusion of acceptor impurities. To get a proper time period for allowing a P-type impurity to penetrate into the N-type epitaxial layer, isolation diffusion is to be carried out. By this process, the P-type impurity will travel through the openings in SiO2 layer, and the N-type layer and thus reach the P-type substrate, Isolation junctions are used to isolate between various components of the IC. The temperature and time period of isolation diffusion should be carefully monitored and controlled. As a result of isolation diffusion, the formation of N-type region called Isolation Island occurs. Each isolated island is then chosen to grow each electrical component. From the figure below you can see that the isolation between the different components inside the IC. Each electrical element is later on formed in a separate isolation island. The bottom of the N-type isolation island ultimately forms the collector of an N-P-N transistor. The P-type substrate is always kept negative with respect to the isolation islands and provided with reverse bias at P-N junctions. The isolation will disappear if the P-N junctions are forward biased.

An effect of capacitance is produced in the region where the two adjoining isolation islands are connected to the P-type substrate. This is basically a parasitic capacitance that will affect the performance of the IC. This kind of capacitance is divided into two. As shown in the figure C1 is one kind of capacitance that forms from the bottom of the N-type region to the substrate and capacitance C2 from the sidewalls of the isolation islands to the P-region. The bottom component C1 is essentially due to step junction formed by epitaxial growth and, therefore, varies as the square root of the voltage V between the isolation region and substrate. The sidewall capacitance C2 is associated with a diffused graded junction and so varies as (-1/2) exponential of V. The total capacitance is of the order of a few picoFarads.

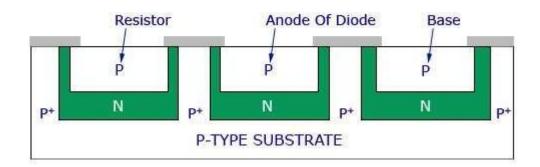

#### 6. Base Diffusion

The working of base diffusion process is shown in the figure below. This process is done to create a new layer of SiO2 over the wafer. P-regions are formed under regulated environments by diffusing P-type impurities like boron. This forms the base region of an N-P-N transistor or as well as resistors, the anode of diode, and junction capacitor. In this case, the diffusion time is so controlled that the P-type impurities do not reach the substrate. The resistivity of the base layer is usually much higher than that of the isolation regions.

### Monolithic IC - Base Diffusion

The isolation regions will have a lot lesser resistivity than that of the base layer.

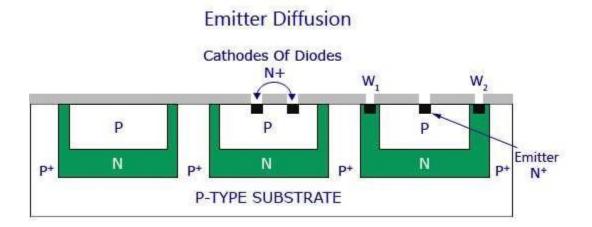

#### 7. Emitter Diffusion

Masking and etching process is again carried out to form a layer of silicon dioxide over the entire surface and opening of the P-type region. The transistor emitters, the cathode regions for diodes, and junction capacitors are grown by diffusion using N-type impurities like phosphorus through the windows created through the process under controlled environmental process. As

shown in the figure below there are two additional windows: W1 and W2. These windows are made in the N-region to carry an aluminium metallization process.

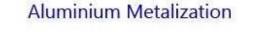

#### 8. Aluminium Metallization

The windows made in the N-region after creating a silicon dioxide layer are then deposited with aluminium on the top surface. The same photoresist technique that was used in photolithographic process is also used here to etch away the unwanted aluminium areas. The structure then provides the connected strips to which the leads are attached. The process can be better understood by going through the figure below.

#### 9. Scribing and Mounting

This is the final stage of the IC manufacturing process. After the metallization process, the silicon wafer is then scribed with a diamond tipped tool and separated into individual chips. Each chip is then mounted on a ceramic wafer and is attached to a suitable header. Next the

package leads are connected to the IC chip by bonding of aluminium or gold wire from the terminal pad on the IC chip to the package lead. Thus the manufacturing process is complete. Thu, hundreds of IC's is manufactured simultaneously on a single silicon wafer.

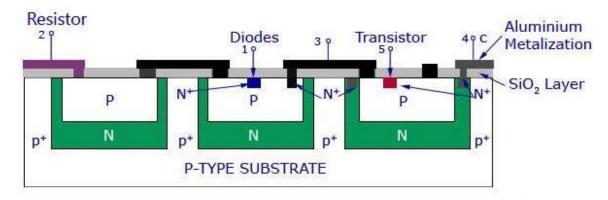

7. What is thick and thin Technology? Explain various methods used for deposition of thin film technology. (Sep 2020)

Conventional film circuits, both thick and thin, are made by depositing film capacitors and resistors on a passive substrate such as glass or ceramic and subsequently adding pre-fabricated active components to the film structure. Care has to be taken that the film elements and their interconnections are compatible with the rest of the integrated circuit.

Combining films and semiconductor technology, a circuit designer has greater degree of freedom, a wider range of component values and better electrical performance than either technology can provide separately.

#### Thin flim and thick flim technology

Various methods in use for deposition of thin film are:

- 1. Vacuum Evaporation

- 2. Sputtering

- 3. Gas plating

- 4. Electroplating

- 5. Electroless plating

- 6. Silk screening

The methods listed above have been used with varying degree of success. In this text however, we limit ourselves to discuss cathode sputtering and plating techniques only.

#### **BM T45 – LINEAR INTEGRATED CIRCUITS**

#### UNIT-2

#### PART-A

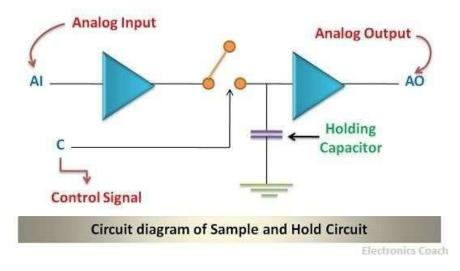

#### 1. Define the functions/operations of sample and hold circuit. (May 2014, May 2018)

- The function of the Sample & Hold Circuit is to sample an analog input signal and hold this value over a certain length of time for subsequent processing.

- > The sampling period may be from 1 to  $10 \mu$ S.

- > The holding period may be from a few milliseconds to several seconds.

#### 2. What are the applications of integrator and differentiator? (May 2014)

- Differentiators are used as wave shaping circuits, to detect high frequency components in the input signal.

- The integrator circuit is mostly used in analog computers, analog-to-digital converters and wave-shaping circuits.

#### 3. What is summing amplifier? (Nov 2014)

- > The summing Amplifier is one variation of inverting amplifier.

- Summing amplifier is basically an op amp circuit that can combine numbers of input signal to a single output that is the weighted sum of the applied inputs.

#### 4. What is slew rate? (Nov 2014)

- The slew rate is defined as the maximum rate of change of output Voltage caused by a step input voltage.

- An ideal slew rate is infinite which means that op-amp's output voltage should change instantaneously in response to input step voltage.

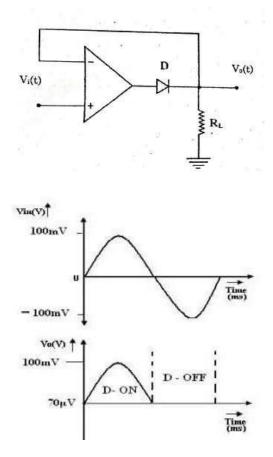

#### 5. How does the precision rectifier differs from the conventional rectifier? (Nov 2015)

- Precision rectifiers use op amp based circuits whereas conventional rectifiers use simple diodes.

- Precision rectifier is a close approximation of an ideal diode because of absence of forward voltage drop.

## 6. State the important features of an instrumentation amplifier. (Nov 2015, Nov 2016, Nov 2017)

High common mode rejection ratio (CMRR)

- ➢ High open loop gain

- ➢ Low DC offset

- ➢ Low drift

- Low input impedance

- ➢ Low noise.

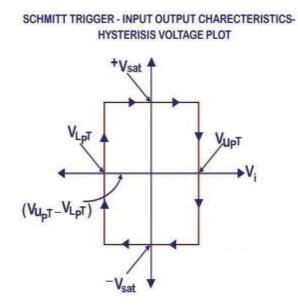

#### 7. Define Hysteresis and Hysteresis voltage of Schmitt trigger. (Nov 2016)

- Hysteresis can be defined as when the input is higher than a certain chosen threshold, the output is low.

- When the input is below a threshold, the output is high; when the input is between the two, the output retains its current value.

- > This dual threshold action is called hysteresis.

## 8. What is the value of open loop gain and output impedance of an ideal Op-amp. (May 2017)

- > The output gain will be infinite.

- > The output impedance of an ideal op amp is 0.

#### 9. Define CMRR. (May 2017)

- > It is defined as the ratio of the differential voltage gain to common mode voltage gain.

- > It is expressed in decibels.

- $CMRR = A_d / A_c$

# 10. Draw the practical sample and hold circuit configuration. (Nov 2017, Nov 2018, May 2019)

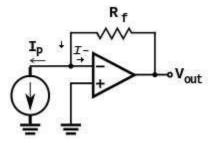

11. Draw the circuit of I to V converter using Op- amp. (May 2018)

12. Sketch the output waveform  $V_0$  (t) for the following circuit, if the input voltage is  $V_i(t)=2\sin(2000 \Pi t)$ . (Nov 2018)

#### 13. How do a Schmitt trigger acts as a regenerative comparator? (May 2019, Sep 2020)

- > A Schmitt trigger circuit is also called a regenerative comparator circuit.

- > It is basically an inverting comparator circuit with a positive feedback.

- The purpose of the Schmitt trigger is to convert any regular or irregular shaped input waveform into a square wave output voltage or pulse.

#### 14. Name four applications of comparator. (Sep 2020)

Zero crossing detector

- ➢ Window detector

- ➢ Time marker generator

- Phase detector

#### PART-B

### 1. What is an instrumentation amplifier? Draw a system whose gain is controlled by an adjustable resistance (May 2014, Nov 2015, May 2018, Nov 2018, Sep 2020)

#### Instrumentation amplifier

In a number of individual and consumers Application, one is required to measure and control physical quantities. Some typical example are Measurement and control of temperature, humidity, light intensity, water flow etc. These physical quantities are usually measure with the help of transducers. The output of the transducers has to be amplified so that it can derive the indicator or display system. This function is performed by an instrumentation amplifier. It is also called data amplifiers.

#### Characteristics

- ➢ High gain accuracy

- ➢ High CMRR

- ➢ Low dc offset

- Low output impedance

- ▶ High gain stability with low temperature coefficient.

#### Applications

- > Temperature indicator

- > Temperature controller

- ➢ Light intensity meter

- > Water flow meter

- Thermal conductivity

$$\begin{array}{c} V_{1} & z & V_{1}^{\prime \prime} & F_{1}^{\prime} & F_{2}^{\prime} & F_{2}^{\prime} \\ V_{1}^{\prime} & z & V_{1}^{\prime \prime} & F_{1}^{\prime} & F_{2}^{\prime} \\ V_{2}^{\prime} & z & V_{2}^{\prime \prime} & F_{1}^{\prime} & F_{2}^{\prime} \\ V_{2}^{\prime} & V_{2}^{\prime \prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ V_{2}^{\prime} & V_{2}^{\prime \prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ V_{2}^{\prime} & V_{2}^{\prime \prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ V_{2}^{\prime} & V_{2}^{\prime \prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ V_{1}^{\prime} & -V_{2}^{\prime \prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ F_{2}^{\prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ \hline & V_{2}^{\prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ F_{2}^{\prime} & V_{2}^{\prime} & V_{2}^{\prime} \\ V_{1}^{\prime} & -V_{2}^{\prime} & V_{2}^{\prime} \\ F_{2}^{\prime} & F_{2}^{\prime} & V_{2}^{\prime} \\ \hline & V_{1}^{\prime} & -V_{2}^{\prime} \\ \hline & V_{1}^{\prime} & -V_{2}^{\prime} \\ F_{2}^{\prime} & F_{2}^{\prime} & F_{2}^{\prime} \\ \hline & V_{1}^{\prime} & -V_{2}^{\prime} \\ \hline & V_{1}^{\prime} & V_{2}^{\prime} \\ \hline & V_{1}^{\prime} & V_{1}^{\prime} \\ \hline & V_{1}^{\prime} & V_{1}$$

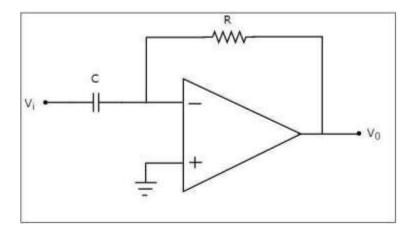

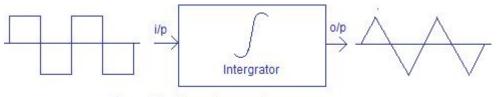

2. a) Explain the operation of differentiator. (May 2014, Nov 2016, Nov 2018)

The input signal to the differentiator is applied to the capacitor. The capacitor blocks any DC content so there is no current flow to the amplifier summing point, X resulting in zero output voltage. The capacitor only allows AC type input voltage changes to pass through and whose frequency is dependent on the rate of change of the input signal.

At low frequencies the reactance of the capacitor is "High" resulting in a low gain ( $R_f/Xc$ ) and low output voltage from the op-amp. At higher frequencies the reactance of the capacitor is much lower resulting in a higher gain and higher output voltage from the differentiator amplifier.

However, at high frequencies an op-amp differentiator circuit becomes unstable and will start to oscillate. This is due mainly to the first-order effect, which determines the frequency response of the op-amp circuit causing a second-order response which, at high frequencies gives an output voltage far higher than what would be expected. To avoid this the high frequency gain of the circuit needs to be reduced by adding an additional small value capacitor across the feedback resistor  $R_f$ .

Since the node voltage of the operational amplifier at its inverting input terminal is zero, the current, i flowing through the capacitor will be given as:

$$I_{IN} = I_F$$

and  $I_F = -\frac{V_{OUT}}{R_F}$

The charge on the capacitor equals Capacitance times Voltage across the capacitor

$$Q = C \times V_{IN}$$

Thus the rate of change of this charge is:

$$\frac{\mathrm{dQ}}{\mathrm{dt}} = \mathrm{C} \, \frac{\mathrm{dV}_{\mathrm{IN}}}{\mathrm{dt}}$$

but dQ/dt is the capacitor current, *i*

$$I_{IN} = C \frac{dV_{IN}}{dt} = I_F$$

$$\therefore -\frac{V_{OUT}}{R_F} = C \frac{dV_{IN}}{dt}$$

from which we have an ideal voltage output for the op-amp differentiator is given as:

$$V_{OUT} = -R_F C \frac{dV_{IN}}{dt}$$

Therefore, the output voltage  $V_{out}$  is a constant  $-Rf^*C$  times the derivative of the input voltage  $V_{in}$  with respect to time. The minus sign (–) indicates a 180° phase shift because the input signal is connected to the inverting input terminal of the operational amplifier.

The Op-amp Differentiator circuit in its basic form has two main disadvantages compared to the previous operational amplifier integrator circuit. One is that it suffers from instability at high frequencies as mentioned above, and the other is that the capacitive input makes it very susceptible to random noise signals and any noise or harmonics present in the source circuit will be amplified more than the input signal itself. This is because the output is proportional to the slope of the input voltage so some means of limiting the bandwidth in order to achieve closed-loop stability is required.

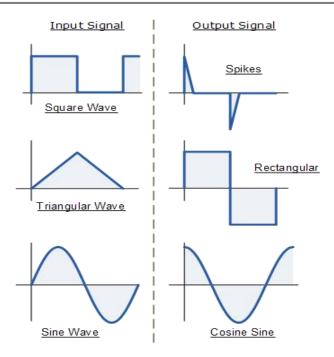

#### **Op-amp Differentiator Waveforms**

If we apply a constantly changing signal such as a Square-wave, Triangular or Sine-wave type signal to the input of a differentiator amplifier circuit the resultant output signal will be changed and whose final shape is dependent upon the RC time constant of the Resistor/Capacitor combination.

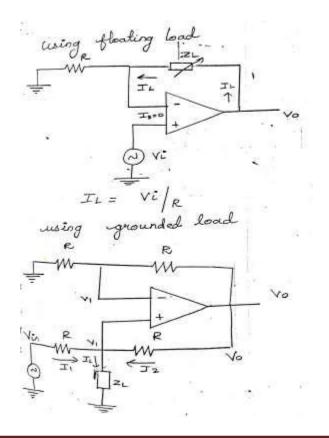

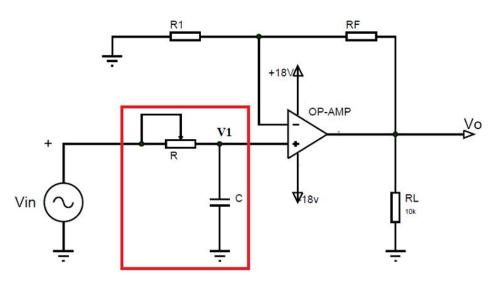

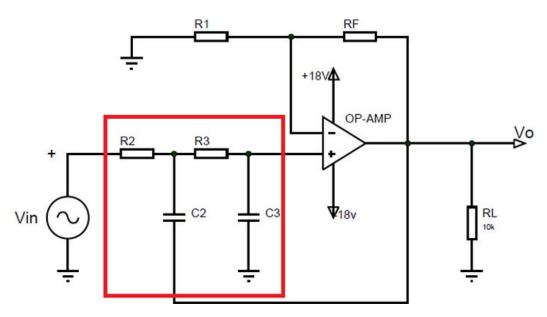

#### 2. Brief about V-I converter. (Nov 2014, Nov 2016, May 2017, May 2019)

#### V to I converter

The voltage to current converter presented as a special case of the inverting amplifier in which an input voltage is converted into a proportional output current. It is also called transconductance amplifier.

Applying kcl,

$$T_{l} + T_{2} = T_{L}$$

$$\frac{V_{ll} - V_{l}}{R} + \frac{V_{0} - V_{l}}{R} = T_{L}$$

$$\frac{V_{ll} + V_{0} - 2V_{l}}{R} = T_{L}R$$

$$V_{ll} + V_{0} - 2V_{l} = T_{L}R - V_{0} - V_{0}$$

$$V_{l} = V_{ll} + V_{0} - T_{L}R$$

$$\frac{V_{l} - V_{0}}{R} + \frac{V_{l} - 0}{R} = 0$$

$$\frac{2V_{l} - V_{0}}{R} = V_{0}$$

$$\frac{V_{l} - V_{0}}{R} = V_{0} + V_{0} - T_{L}R$$

$$\frac{V_{l} - V_{0}}{R} = V_{l} - T_{L}R$$

## 12 C RL Vo dia usi 3 TS -Is = Ic m I€ = Is <u>I</u>c Ts +1 $V_{E} = -V_{o}$ Ic 12 2 Ri re output voltage RiIs = function of logari Va 303 log ( Vi/verel

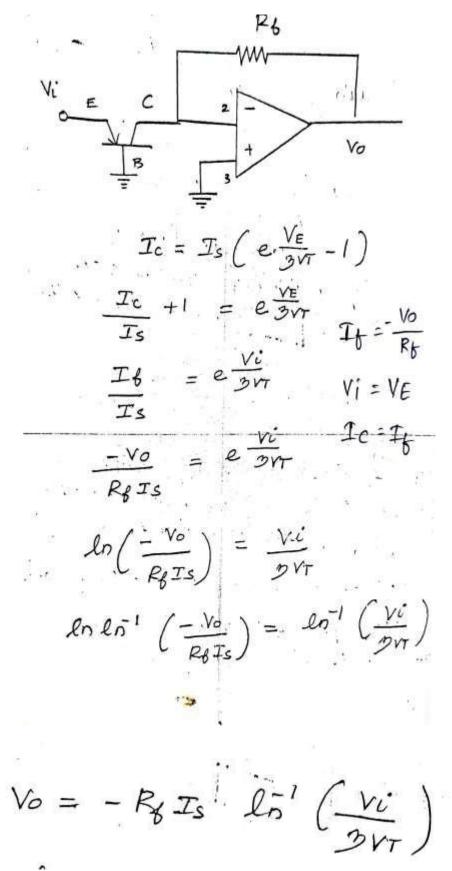

#### 4. Brief about Log amplifier. (Nov 2014, Nov 2017, Sep 2020, Nov 2018)

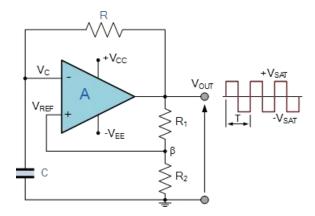

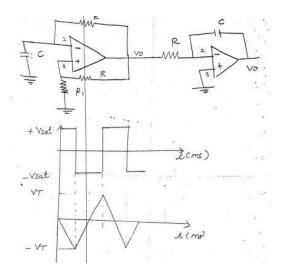

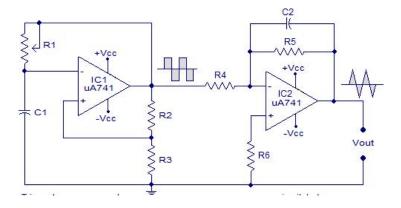

# 5. Explain the working of multivibrator using operational amplifiers in detail. (Nov 2014, May 2019)

## **Op-amp** Multivibrator

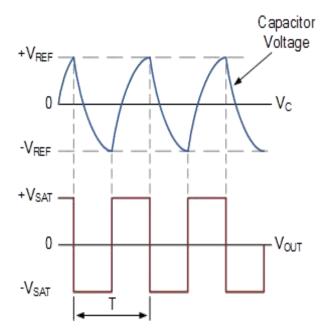

The idea of converting a periodic waveform into a rectangular output one step further by replacing the sinusoidal input with an RC timing circuit connected across the op-amps output. This time, instead of a sinusoidal waveform being used to trigger the op-amp, we can use the capacitors charging voltage, Vc to change the output state of the op-amp as shown.

## **Op-amp Multivibrator Circuit**

Lets assume that the capacitor is fully discharged and the output of the op-amp is saturated at the positive supply rail. The capacitor, C starts to charge up from the output voltage, Vout through resistor, R at a rate determined by their RC time constant.

We know from our tutorials about RC circuits that the capacitor wants to charge up fully to the value of Vout (which is +V(sat)) within five time constants. However, as soon as the capacitors charging voltage at the op-amps inverting (-) terminal is equal to or greater than the voltage at the non-inverting terminal (the op-amps output voltage fraction divided between resistors R1 and R2), the output will change state and be driven to the oppos ing negative supply rail.

But the capacitor, which has been happily charging towards the positive supply rail (+V(sat)), now sees a negative voltage, -V(sat) across its plates. This sudden reversal of the output voltage causes the capacitor to discharge toward the new value of Vout at a rate dictated again by their RC time constant.

## **Op-amp Multivibrator Voltages**

Once the op-amps inverting terminal reaches the new negative reference voltage, -Vref at the non-inverting terminal, the op-amp once again changes state and the output is driven to the opposing supply rail voltage, +V(sat). The capacitor now see's a positive voltage across its

plates and the charging cycle begins again. Thus, the capacitor is constantly charging and discharging creating an astable op-amp multivibrator output.

The period of the output waveform is determined by the RC time constant of the two timing components and the feedback ratio established by the R1, R2 voltage divider network which sets the reference voltage level. If the positive and negative values of the amplifiers saturation voltage have the same magnitude, then t1 = t2 and the expression to give the period of oscillation becomes:

$$\beta = \frac{R_2}{R_1 + R_2}$$

$$T = 2RC \times \ln\left(\frac{1+\beta}{1-\beta}\right) \quad \therefore f = \frac{1}{T}$$

Where: R is Resistance, C is Capacitance, ln() is the Natural Logarithm of the feedback fraction, T is periodic time in seconds, and f is oscillation Frequency in Hz.

Then we can see from the above equation that the frequency of oscillation for an **Op-amp Multivibrator** circuit not only depends upon the RC time constant but also upon the feedback fraction. However, if we used resistor values that gave a feedback fraction of **0.462**, ( $\beta = 0.462$ ), then the frequency of oscillation of the circuit would be equal to just 1/2RC as shown because the linear log term becomes equal to one.

## 6. Write short notes on Antilog amplifier. (Nov 2015, Nov 2016, May 2017, Sep 2020)

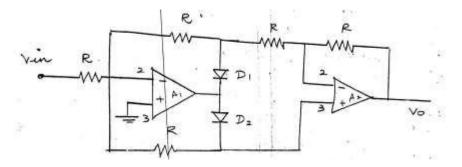

## 7. Write short notes on Precision rectifier. (Nov 2015)

(12 During negative half cycle; and Da is on Vi LO, Diode D, is off m 2 (Virtual grad) R 3 point x' O-V RR +0-10 R  $\frac{V\hat{v}}{R} + \frac{V}{R} + \frac{V}{2R} = 0$  $\frac{Vi}{R} + \frac{3V}{2R} = 0 \left( \frac{Vi}{2R} \right)$ ¥:+=v=0 1= -2/3 Vi  $V_0 = \left( \frac{1+R}{2R} \right)$  $Vo = \left(\frac{2R+R}{RR}\right)$ Vo = (3R) Vo = 3/2 V ∋ Vo:  $V_{0} = 3/2 \left( \frac{-2}{3} \right) V_{1}^{2}$  $V_0 = \frac{3}{2} \times C$

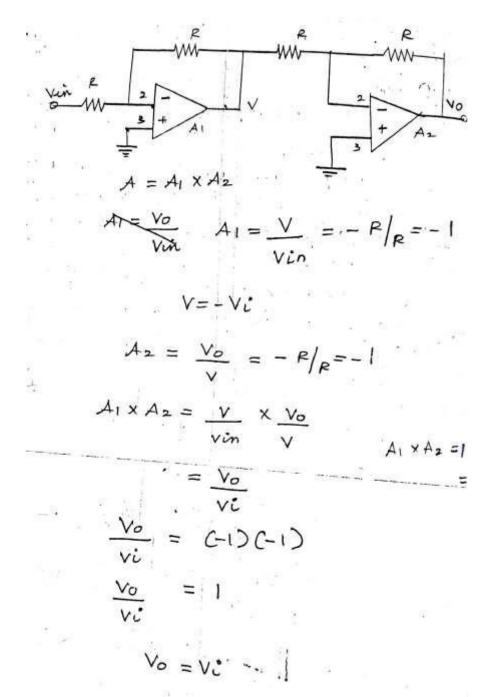

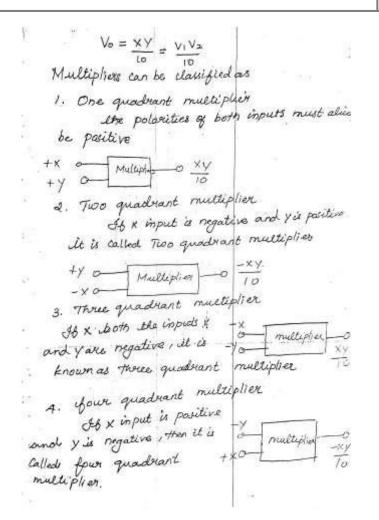

## 8. Draw the circuit and explain about an OP-AMP used as a Multiplier (Nov 2016) Multiplier

Log and anti log amplifiers are used in this circuits. The output voltage is proportional to the product of the two input voltages. It is called analog voltage multipliers.

R Voc (4,) log Antila Ampli Vob R log 1 Applying Superposition theorem, Vac & Unv with mplifier Vob loa x C ln V, y ln V2 tilog Voc VOC IS ol. a lo' (lnviv2) Vo VO & VIV2 3 k= /vere output is proportional nalog puts of 200 Multiplier IC V GINP

#### Applications

- Voltage divider

- Squaring circuit

- Square rooting circuit

- Frequency double

- Phase angle detection

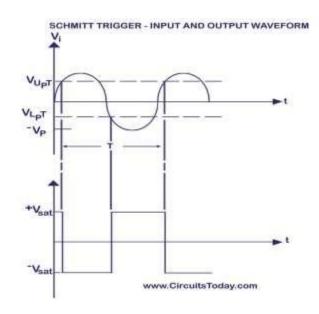

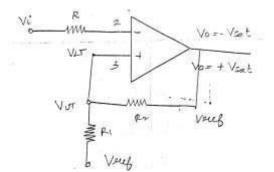

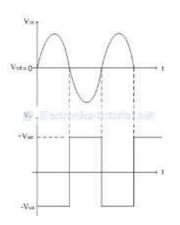

## 9. Explain the working of Schmitt trigger using op amp in detail (May 2017, May 2018, Nov 2018)

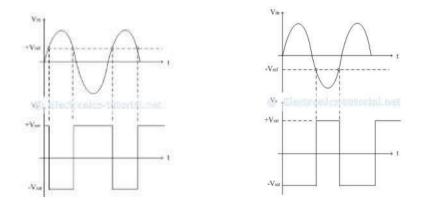

#### Schmitt trigger 741

It converts sinusoidal input to square wave output. The output of Schmitt trigger swings between upper threshold voltage and lower threshold voltage and the reference voltage of the input waveform.

The difference in voltage between Vut and Vlt is called hysteresis voltage. The curve looking like hysteria curve of magnetic materials.

VH = Vut - Vlt

During positive cycle

$$\frac{Vur - Vret}{R_1} + \frac{V_{uT} - V_{sat}}{R_2} = 0$$

$$\frac{Vur}{R_1} + \frac{Vur}{R_2} + \left(-\frac{Vret}{R_2} - \frac{Vsat}{R_2}\right) = 0$$

$$\frac{1}{R_1} + \frac{1}{R_2} \left(Vur\right) = \frac{Vret}{R_1} + \frac{Vsat}{R_2}$$

$$\frac{Vur}{R_1} = \frac{R_2 Vret}{R_1} + VsatR_1 + \frac{Vzrt}{R_2}$$

$$V_{0T} = \frac{R_1 R_2}{R_1 + R_2} \qquad R_1 + R_2$$

$$V_{0T} = \frac{R_2 V_{T} + V_{Sal} R_1}{R_1 + R_2}$$

During negative cycle

$$\frac{V_{1T} - V_{7}e_{F}}{R_{1}} + \frac{V_{1T} + V_{5}a_{F}}{R_{2}} = \frac{7}{20} + \frac{V_{1T} + V_{5}a_{F}}{R_{1}} - \frac{V_{5}a_{F}}{R_{2}} + \frac{V_{1T} + V_{5}a_{F}}{R_{1}} - \frac{V_{5}a_{F}}{R_{2}} + \frac{V_{1T} + V_{5}a_{F}}{R_{1}R_{2}} + \frac{V_{1T} + V_{5}a_{F}}{R_{1}R_{2}} + \frac{V_{1T} + V_{5}a_{F}}{R_{1}R_{2}} + \frac{R_{2}V_{7}e_{F} - R_{1}V_{5}a_{F}}{R_{1}R_{2}} + \frac{R_{1}R_{2}}{R_{1}R_{2}} + \frac{V_{1T} = \frac{R_{2}V_{7}e_{F} - R_{1}V_{5}a_{F}}{R_{1}R_{2}} \times \frac{R_{1}R_{2}}{R_{1}+R_{2}} + \frac{V_{1T} = \frac{R_{2}V_{7}e_{F} - V_{5}a_{F}R_{1}}{R_{1}+R_{2}} + \frac{V_{1T} = \frac{R_{2}V_{7}e_{F} - V_{5}a_{F}R_{1}}{R_{1}+R_{2}} + \frac{V_{1T} = \frac{R_{2}V_{7}e_{F} - V_{5}a_{F}R_{1}}{R_{1}+R_{2}} + \frac{R_{1}R_{2}}{R_{1}+R_{2}} + \frac{V_{1T} - V_{1T}}{R_{1}+R_{2}} + \frac{V_{1T} -$$

$$V_{H} = \bigvee_{i \neq j} V_{i \neq j} + \bigvee_{i \neq j} V_{i \neq j} - \bigvee_{i \neq j} V_{i \neq j} - \bigvee_{i \neq k} V_{i \neq k}$$

$$= \underbrace{R_{2} \bigvee_{i \neq k} + \bigvee_{i \neq k}}_{R_{1} + R_{2}} R_{1} - \underbrace{R_{2} \bigvee_{i \neq k} + \bigvee_{i \neq k}}_{R_{1} + R_{2}}$$

$$= \underbrace{R_{2} \bigvee_{i \neq k} + \bigvee_{i \neq k}}_{R_{1} + R_{2}}$$

$$R_{1} + R_{2}$$

$$V_{H} = \underbrace{\mathcal{Z} \bigvee_{i \neq k} R_{i}}_{R_{1} + R_{2}}$$

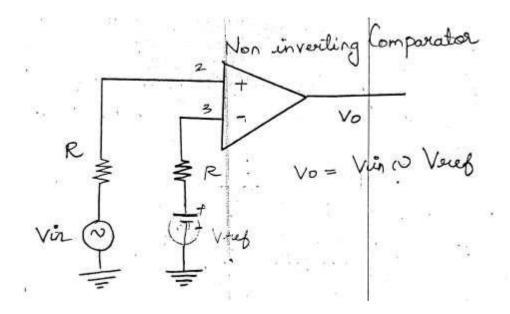

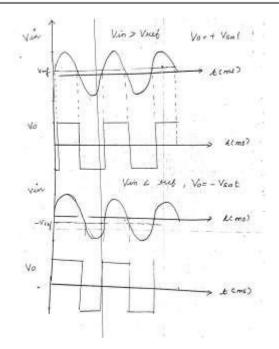

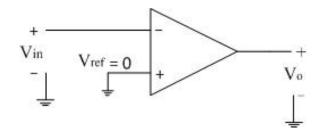

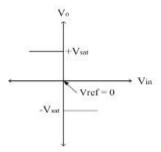

## 10. Explain about comparator (Inverting and Non inverting comparator). (May 2017, Nov 2017)

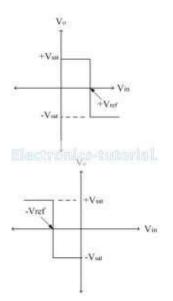

#### Comparator

A comparator is a circuit which compares a signal voltage applied at input of an opamp with a known reference voltage at the other input. The comparator is a type of analog to digital converter. Vin is greater or less than Vref. The comparator is sometimes called a voltage level detector.

#### **Comparator characteristics**

- ➢ Response time

- > Accuracy

- ➢ Logic threshold

#### Types

- Inverting comparator

- Non Inverting comparator

#### **Inverting Comparator**

The following figure shows the inverting configuration of comparator. The input signal is applied at inverting terminal of op-amp. The reference voltage Vref = 0V.

Due to open loop configuration of op-amp, the output goes into saturation. The operation of the comparator is explained with the following two equations 1. If Vin> Vref then Vo=-Vsat

Thus for the positive half cycle of the input signal the above condition is true. So for the positive half cycle of input signal, the output goes into negative saturation i.e. –Vsat. The input and output waveforms are shown below.

### 2. If Vin<Vref then Vo=+V\_sat

Thus for the negative half cycle of the input signal the above condition is true. So for the negative half cycle of input signal, the output goes into positive saturation i.e. +Vsat. The transfer characteristics are shown in figure below.

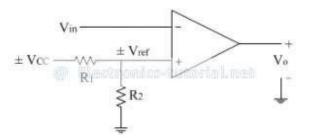

The reference voltage is zero here and hence the circuit is also called as inverting zero crossing detector. The reference voltage can be changed externally with the help of potential divider arrangement. This reference voltage can be either positive or negative as shown in circuit diagram below.

If the supply voltage is positive, the reference voltage is also positive. If the supply voltage is negative, the reference voltage is also negative.

$$\pm V_{ref} = \frac{R_2}{(R_1 + R_2)} (\pm V_{CC})$$

The following figure shows the input and output waveforms for positive reference and negative reference.

The transfer characteristics of both positive as well as negative reference are shown below.

The transfer characteristics are basically a graph of output voltage versus input voltage. From the above characteristics, it is observed that the reference voltage (or reference point) is the point at which the state change occurs i.e. the transition from one state to other state. In other words, the circuit is triggered at the reference point hence it is also called as triggering point. The reference voltage can be changed externally and also can be either positive or negative as discussed above. Thus the reference point can have a trip on input axis anywhere, and hence it is also referred as trip point or trip voltage. Also at the reference point the state change occurs at the output when input signal crosses the reference voltage. Thus reference voltage is also called as threshold voltage at which the comparator is changing its output state.

## Application

- Zero crossing detector

- Window detector

- Time marker generator

- Phase meter

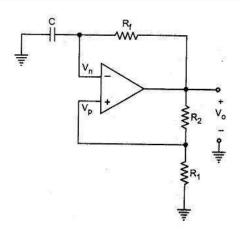

## 11. Write short notes on Square wave generator (May 2018)

#### Square Wave Generator Using Op amp:

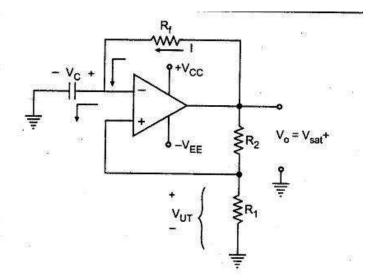

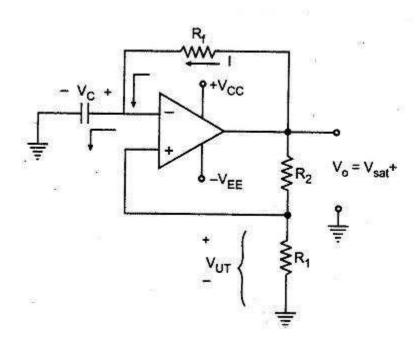

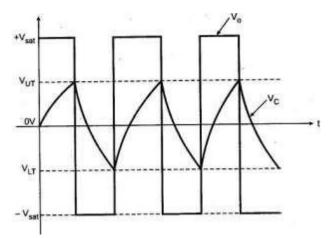

The Square Wave Generator Using Op amp means the astable multivibrator circuit using opamp, which generates the square wave of required frequency. The Fig shows the square wave generator using op amp.

It looks like a comparator with hysteresis (schmitt trigger), except that the input voltage is replaced by a capacitor. The circuit has a time dependent elements such as resistance and capacitor to set the frequency of oscillation.

As shown in the Fig the comparator and positive feedback resistors  $R_1$  and  $R_2$  form an inverting schmitt trigger.

When  $V_{\text{o}}$  is at  $+V_{\text{sat}},$  the feedback voltage is called the upper threshold voltage  $V_{\text{UT}}$  and is given as

$$V_{UT} = \frac{R_1 + V_{sat}}{R_1 + R_2} ... (1)$$

When  $V_o$  is at  $-V_{sat}$ , the feedback voltage is called the lower-threshold voltage  $V_{LT}$  and is given as

$$V_{LT} = \frac{R_1 \cdot -V_{sat}}{R_1 + R_2}$$

... (2)

When power is turn ON,  $V_o$  automatically swings either to  $+V_{sat}$  or to  $-V_{sat}$  since these are the only stable states allowed by the schmitt trigger. Assume it swings to  $+V_{sat}$ . With  $V_o = +V_{sat}$  we have  $-V_p = V_{UT}$  and capacitor starts charging towards  $+V_{sat}$  through the feedback path provided by the resistor  $R_f$  to the inverting (-) input. As long as the capacitor voltage  $V_C$  is less than  $V_{UT}$ , the output voltage remains at  $+V_{sat}$ .

As soon as  $V_C$  charges to a value slightly greater than  $V_{\text{UT}}$ , the (-) input goes positive with respect to the (+) input. This switches the output voltage from  $+V_{\text{sat}}$  to  $-V_{\text{sat}}$  and we have  $V_p = V_{\text{LT}}$ , which is negative with respect to ground. As  $V_o$  switches to  $-V_{\text{sat}}$ , capacitor starts discharging via  $R_f$ , as shown in the Fig.

The current I – discharges capacitor to 0 V and recharges capacitor to  $V_{LT}$ . When  $V_C$  becomes slightly more negative than the feedback voltage  $V_{LT}$ , output voltage  $V_o$  switches back to  $+V_{sat}$ . As a result, the condition in Fig. 2.84(a) is reestablished except that capacitor now has a initial charge equal to  $V_{LT}$ . The capacitor will discharge from  $V_{LT}$  to 0V and then recharge to  $V_{UT}$ , and the process is repeating. Once the, initial cycle is completed, the waveform become periodic, as shown in the Fig. 2.84(c).

## **Frequency of Oscillation:**

The frequency of oscillation of Square Wave Generator Using Op amp is determined by the time it takes the <u>capacitor</u> to charge from V  $_{UT}$  to V<sub>LT</sub> and vice versa. The voltage across the capacitor as a function of time is given as

$$V_{C}(t) = V_{max} + (V_{initial} - V_{max})e^{(-t/T)}$$

... (3)

where

$V_{C}(t)$  is the instantaneous voltage across the capacitor.

V<sub>initial</sub> is the initial voltage

$V_{max}$  is the voltage toward which the capacitor is charging.

Let us consider the charging of capacitor from  $V_{LT}$  to  $V_{UT}$ , where  $V_{LT}$  is the initial voltage,  $V_{UT}$  is the instantaneous voltage and  $+V_{sat}$  is the maximum voltage. At  $t = T_1$ , voltage across capacitor reaches  $V_{UT}$  and therefore equation (3) becomes

$$V_{UT} = +V_{sat} + (V_{LT} - +V_{sat})e^{(-Tt/R_{f}C)} \qquad \dots (4)$$

$$\therefore - (V_{LT} - +V_{sat})e^{(-Tt/R_{f}C)} = +V_{sat} - V_{UT}$$

$$\therefore e^{(-Tt/R_{f}C)} = \frac{(+V_{sat} - V_{UT})}{(+V_{sat} - V_{LT})}$$

$$\frac{-T_{I}}{R_{f}C} = ln\left(\frac{+V_{sat} - V_{UT}}{+V_{sat} - V_{LT}}\right)$$

$$T_{I} = -R_{f}C ln\left(\frac{+V_{sat} - V_{UT}}{+V_{sat} - V_{LT}}\right)$$

$$= R_{f}C ln\left(\frac{+V_{sat} - V_{LT}}{+V_{sat} - V_{UT}}\right) \qquad \dots (5)$$

The time taken by capacitor to charge from  $V_{UT}$  to  $V_{LT}$  is same as time required for charging capacitor from  $V_{LT}$  to  $V_{UT}$ . Therefore, total time required for one oscillation is given as

$$T = 2T_{1} ... (6)$$

=  $2R_{f} C ln \left( \frac{+V_{sat} - V_{LT}}{+V_{sat} - V_{UT}} \right) ... (7)$

The frequency of oscillation can be determined as  $f_o = 1/T$ , where T represents the time required for one oscillation.

Substituting the value of T we get,

$$f_{o} = \frac{1}{2 R_{f} C ln \left(\frac{+V_{sat} - V_{LT}}{+V_{sat} - V_{UT}}\right)}.$$

(8)

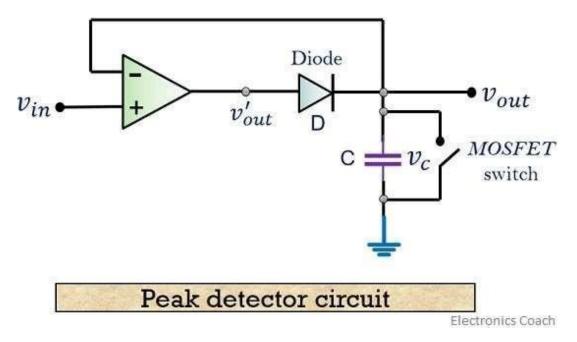

#### 12. Write short notes about Peak detector. (May 2019)

Peak detector circuits are used to determine the peak (maximum) value of an input signal. It stores the peak value of input voltages for infinite time duration until it comes to reset condition. The peak detector circuit utilizes its property of following the highest value of an input signal and storing it.

Rectifier circuits usually provide an output in proportion to the average value of the input. However, some application requires measurement of the peak value of the signal. Thus, peak detectors are used.

Usually, the peak of non-sinusoidal waveforms is measured using a peak detector. As traditional ac voltmeter cannot measure the peak of such signals.

#### **Circuit Working of Peak detector**

The figure below shows the circuit of a basic positive peak detector-

It consists of a diode and capacitor along with an op-amp as shown above. The circuit does not require any complex component in order to determine the peak of the input waveform.

## **Working Principle**

The working principle of the circuit is such that, the peak of the input waveform is followed and stored in terms of voltage in the capacitor.

By the time on moving further, if the circuit detects a higher peak, the new peak value is stored in the capacitor until it is discharged.

The capacitor employed in the circuit is charged through the diode by the applied input signal. The small voltage drop across the diode is ignored and the capacitor is charged up to the highest peak of the applied input signal.

Let us consider initially the capacitor is charged to voltage  $V_c$ . The diode employed in the circuit gets forward biased when the applied input voltage  $V_{in}$  exceeds the capacitor voltage  $V_c$ . Thereby allowing the circuit to behave as a voltage follower. The output voltage follows the applied input voltage until  $V_{in}$  is more than  $V_c$ .

As the input voltage  $V_{in}$  reduces below the value of capacitive voltage  $V_c$ , it causes the diode to get reverse biased. In such condition, the capacitor retains the value until the input again exceeds the value stored in the capacitor.

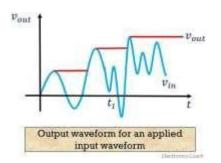

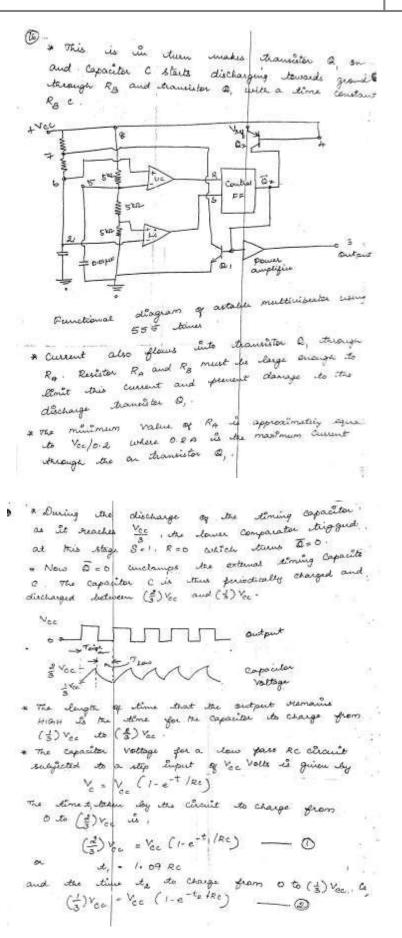

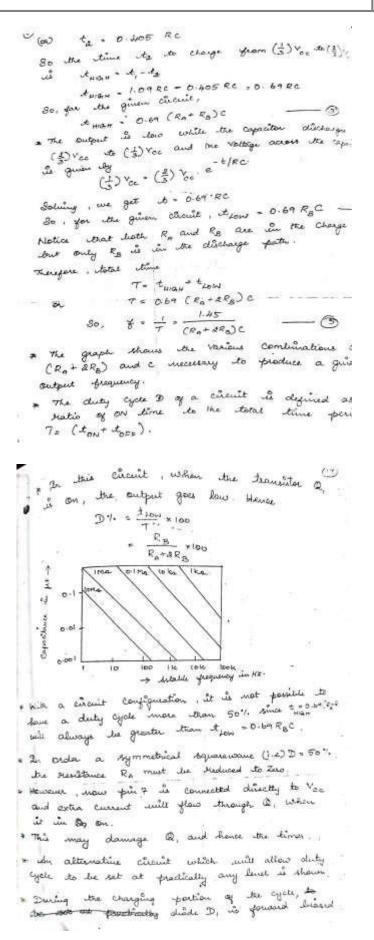

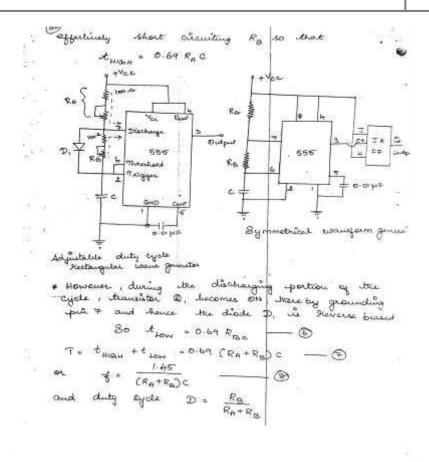

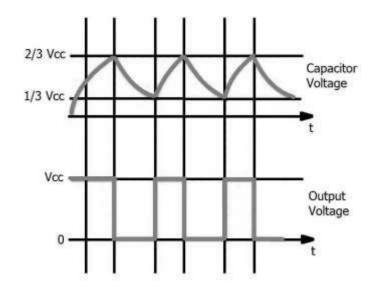

The figure below shows the output voltage waveform for an applied input signal.

As we can see in the waveform shown above, at time  $t_1$ , the circuit misses the peak of the input signal as it is less than the previous peak of the input signal. Thereby allowing the capacitor to hold the value of the previously occurred peak.

As it is a positive peak detector, one can also construct a negative peak detector circuit, that will hold the lowest or most negative signal voltage. This is basically done by reversing the polarities of the diode in the circuit.

Improvement in peak detector circuit

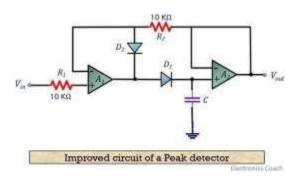

The figure below shows the circuit of an improved peak detector. It is used to buffer the source of the signal from that of the capacitor.

As we can see the circuit is comprised of 2 Op-amps. However, the basic circuit of the peak detector contains only one Op-amp. A high impedance load is offered by the op-amp  $A_1$  to the source. While op-amp  $A_2$  performs buffering action in between the load and capacitor.

The same basic principle is applied in this circuit also. The voltage at the output side is the similar as the peak of the input signal stored in the capacitor.

Its working is such that, as the input voltage becomes higher than the charge stored on the capacitor, it charges itself with the new higher value of input signal.

However, for a smaller value of the input, the capacitor sticks to the previous higher value. The diode  $D_2$  employed here restricts the output of op-amp  $A_1$  from reaching negative saturation.

This basically provides an improvement in the recovery time of op-amp  $A_1$  at the condition of attaining a higher peak than the previous. The two resistances serve as the path for the bias current of input to  $A_1$ .

To prevent the effect of the offset voltage, the value of the two resistances  $R_1$  and  $R_2$  are kept equal.

The necessary frequency compensation must be given to op-amp  $A_1$  in order to have stability against oscillations.

#### **Applications of Peak detector**

- 1. It is used in the analysis of spectral and mass spectrometer.

- 2. Peak detector finds its application in destructive testing.

- 3. It is used for instrumentation measurement, mostly in amplitude modulated wave communication.

- 4. It widely finds applications in sound measuring instruments.

## **BM T45 – LINEAR INTEGRATED CIRCUITS**

## UNIT-3

## PART-A

#### 1. (a) What are the limitations of three terminal regulator? (May 2014)

#### (b) Enumerate the limitations of three terminal voltage regulators. (Nov 2018)

- Limited power dissipation in available packages

- Limited current ranges

- Fixed voltage versions

- Dropout voltage

#### 2. Discuss the advantages and disadvantages of SMPS. (May 2014)

#### Advantages

- > The switch mode power supply has a smaller in size.

- > The SMPS has light weight. SMPS has wide output range.

- ➢ Low heat generation in SMPS.

- SMPS has wide output range.

- ➢ Low heat generation in SMPS.

#### Disadvantages

- ➢ It can be used only as a step down regulator.

- ➢ It has only one output voltage.

- > It has high frequency electrical noise.

- > SMPS also cause harmonic distortion.

## 3. Give some applications of comparators. (Nov 2014)

- Zero crossing detector

- Window detector

- Time marker generator

- Phase detector

#### 4. What is the function of voltage regulators? (Nov 2014, May 2017, Nov 2017)

A voltage regulator is an electronic circuit that provides a stable dc voltage independent of the load current, temperature, and ac line voltage variations.

#### 5. State the important features of an instrumentation amplifier. Nov 2015)

- ➢ High common mode rejection ratio (CMRR)

- ➢ High open loop gain

- ➢ Low DC offset

- ➢ Low drift

- Low input impedance

➢ Low noise.

## 6. Define voltage to frequency conversion factor of VCO. (Nov 2015)

> Voltage to Frequency conversion factor is defined as,

Kv = fo / Vc = 8fo / Vcc

➢ Vc is the modulation voltage, fo-frequency shift

#### 7. Define pass band of a filter. (Nov 2016)

- A band pass filter is an electronic circuit or device which allows only signals between specific frequencies to pass through and attenuates/rejects frequencies outside the range.

- > Band pass filters are largely used in wireless receivers and transmitters.

#### 8. State the two conditions of oscillations. (Nov 2016)

- The total phase shift around the loop must be zero at the desired frequency of oscillation.

- > The magnitude of the loop gain  $|A\beta|$  should be equal to unity.

#### 9. What is the principle of switch mode power supplies? (May 2017)

- > SMPS circuit is operated by switching and hence the voltages vary continuously.

- > The switching device is operated in saturation or cut off mode.

- > The output voltage is controlled by the switching time of the feedback circuitry.

- > Switching time is adjusted by adjusting the duty cycle.

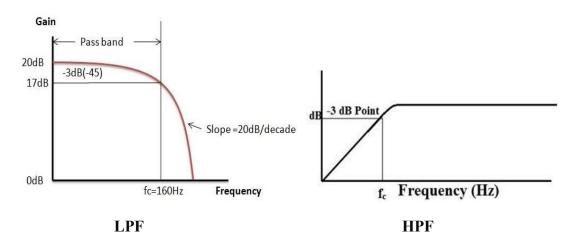

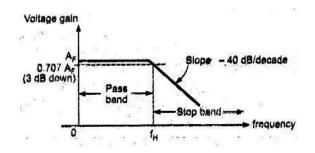

## 10. Give the graphical representation of frequency response of LPF and HPF. (Nov 2017)

## 11. What are the applications of oscillator? (May 2018)

- Used in various audio systems and video systems

- > Used in various radio, TV, and other communication devices

- Used in alarms and buzzes

- > Used in metal detectors, stun guns, inverters, and ultrasonic

## 12. In what way VCO is different from other oscillators? (May 2018)

- A VCO is a Voltage Controlled Oscillators i.e. it is an electronic oscillator whose oscillating/output frequency can be controlled by a DC voltage.

- The oscillating/output frequency of the VCO can be modified by changing the DC voltage applied to it.

## 13. How do we get a notch filter from a band pass filter? (May 2019)

- > A notch filter is a narrow band stop filter.

- ➢ If the stop band of Band stop filter is very narrow and highly attenuated over a few hertz, then that special type of band stop filter is known as Notch Filter.

## 14. Why VCO is called voltage to frequency converter? (May 2019, Sep 2020)

- > The VCO provides the linear relationship between the applied voltage & the output frequency.

- So it is known as voltage to frequency converter.

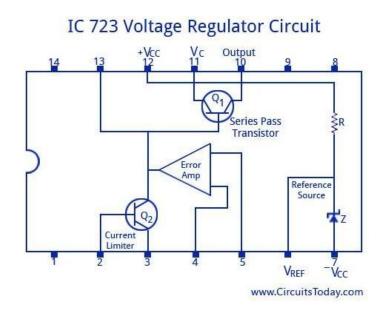

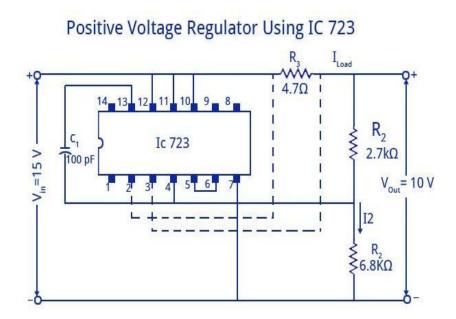

### 15. How current boosting is achieved in a 723 regulator? (Sep 2020)

- > The 723 voltage regulator is commonly used for series voltage regulator applications.

- > It can be used as both positive and negative voltage regulator.

- It has an ability to provide up to 150 mA of current to the load, but this can be increased more than 10A by using power transistors.

## PART-B

#### 1. a) Explain the operation of SMPS in detail. (May 2014, Nov 2015)

- b) With neat circuit diagrams and waveforms, explain the operation of SMPS. (Nov 2017, May 2018)

- c) Explain about switching regulator. (Nov 2016)

- d) Explain the working principle of switched mode power supply. Discuss its advantage and disadvantages. (Sep 2020)

#### Switched Mode Power Supply (SMPS)

The disadvantages of LPS such as lower efficiency, the need for large value of capacitors to

reduce ripples and heavy and costly transformers etc. are overcome by the implementation of Switched Mode Power Supplies.

The working of SMPS is simply understood by knowing that the transistor used in LPS is used to control the voltage drop while the transistor in SMPS is used as a controlled switch.

## Working

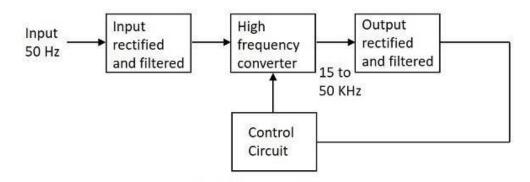

The working of SMPS can be understood by the following figure.

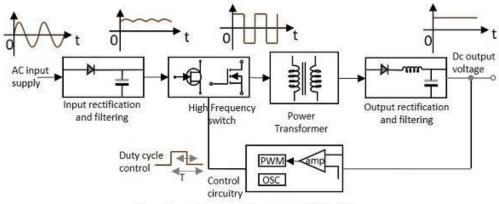

## Input Stage

The AC input supply signal 50 Hz is given directly to the rectifier and filter circuit combination without using any transformer. This output will have many variations and the capacitance value of the capacitor should be higher to handle the input fluctuations. This unregulated dc is given to the central switching section of SMPS.

## **Switching Section**

A fast switching device such as a Power transistor or a MOSFET is employed in this section, which switches ON and OFF according to the variations and this output is given to the primary of the transformer present in this section. The transformer used here are much smaller and lighter ones unlike the ones used for 60 Hz supply. These are much efficient and hence the power conversion ratio is higher.

## **Output Stage**

The output signal from the switching section is again rectified and filtered, to get the required DC voltage. This is a regulated output voltage which is then given to the control circuit, which is a feedback circuit. The final output is obtained after considering the feedback signal.

## **Control Unit**

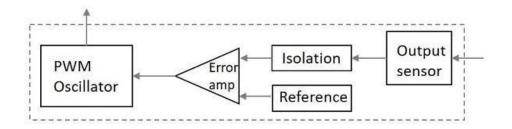

This unit is the feedback circuit which has many sections. Let us have a clear understanding about this from the following figure.

The above figure explains the inner parts of a control unit. The output sensor senses the signal and joins it to the control unit. The signal is isolated from the other section so that any sudden spikes should not affect the circuitry. A reference voltage is given as one input along with the signal to the error amplifier which is a comparator that compares the signal with the required signal level.

By controlling the chopping frequency the final voltage level is maintained. This is controlled by comparing the inputs given to the error amplifier, whose output helps to decide whether to increase or decrease the chopping frequency. The PWM oscillator produces a standard PWM wave fixed frequency.

Functional block diagram of SMPS

The SMPS is mostly used where switching of voltages is not at all a problem and where efficiency of the system really matters.

- SMPS circuit is operated by switching and hence the voltages vary continuously.

- The switching device is operated in saturation or cut off mode.

- The output voltage is controlled by the switching time of the feedback circuitry.

- Switching time is adjusted by adjusting the duty cycle.

- The efficiency of SMPS is high because, instead of dissipating excess power as heat, it continuously switches its input to control the output.

## Disadvantages

• The noise is present due to high frequency switching.

- The circuit is complex.

- It produces electromagnetic interference.

#### Advantages

- The efficiency is as high as 80 to 90%

- Less heat generation; less power wastage.

- Reduced harmonic feedback into the supply mains.

- The device is compact and small in size.

- The manufacturing cost is reduced.

- Provision for providing the required number of voltages.

#### Applications

They are used in the motherboard of computers, mobile phone chargers, HVDC measurements, battery chargers, central power distribution, motor vehicles, consumer electronics, laptops, security systems, space stations, etc.

#### **Types of SMPS**

SMPS is the Switched Mode Power Supply circuit which is designed for obtaining the regulated DC output voltage from an unregulated DC or AC voltage. There are four main types of SMPS such as

- DC to DC Converter

- AC to DC Converter

- Fly back Converter

- Forward Converter

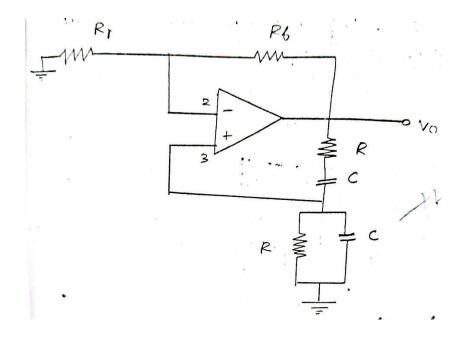

## 2. a) Explain in detail phase shift oscillator. (May 2014, May 2019)

b) Briefly explain the Barkhausen criterion for oscillation. With neat circuit diagram explain the construction and operation of RC phase shift oscillator using op-amp. Also derive the expression for frequency of oscillation. (Nov 2018)

$$V_{0} \stackrel{(1)}{\longrightarrow} \stackrel{(1)}{\longrightarrow$$

$$\frac{V_{6}}{V_{0}} = \frac{P^{5}}{6R^{2}x + R^{3} + 5P^{5}x^{5} + x^{5}}$$

$$\frac{V_{6}}{V_{0}} = \frac{1}{1 + \frac{b}{R^{2}} + \frac{5x^{5}}{R^{2}} + \frac{x^{3}}{R^{5}}}$$

$$\frac{V_{6}}{V_{0}} = \frac{1}{1 + \frac{b}{1}WCR} - \frac{5}{w^{2}C^{2}R^{2}} + \frac{1}{j(w^{2}c^{5}R^{3})}$$

$$\frac{w}{w} = \frac{1}{w^{R}C}$$

$$\frac{1}{j} = -j, \quad \frac{1}{j^{2}} = -1, \quad \frac{1}{j^{5}} = j$$

$$\frac{V_{6}}{V_{0}} = \frac{1}{1 + j^{6}x - 5x^{2} + jx^{5}}$$

$$= \frac{1}{(1 - 5x^{2}) - j^{6}x^{5} - 6x}$$

$$h_{\beta} = \frac{h}{a+jb} \qquad a = 1 - 5x^{2}$$

$$= \frac{h}{a+jb} \times \frac{a-jb}{a+jb}$$

$$= \frac{ha}{a^{2}+b^{2}} - \frac{j^{R}h}{a^{2}+b^{2}}$$

Condition for ascillation

$$h_{\beta} = j$$

$$h_{\beta} = 1+jp$$

$$\frac{\mu_{\alpha}}{\alpha^{2} + b^{2}} = i - \frac{\gamma_{b}}{\alpha^{2} + b^{2}} = 0$$

$$R = -\frac{P_{b}}{p_{1}}$$

$$-\frac{\int P_{b}}{\alpha^{2} + b^{2}} = 0$$

$$b = 0 - \alpha^{2} - b\alpha = 0$$

$$\alpha^{3} = b \propto$$

$$\alpha^{4} = b \approx$$

$$\alpha^{4} = b \approx$$

$$\alpha^{4} = b \approx$$

$$\frac{\sqrt{b}}{\sqrt{b}} = \frac{1}{\sqrt{b}} \frac{1}{$$

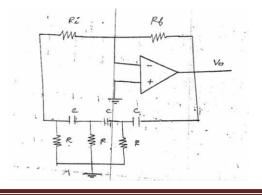

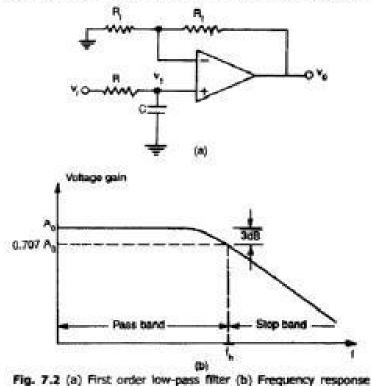

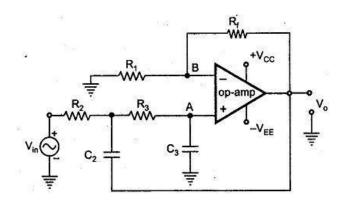

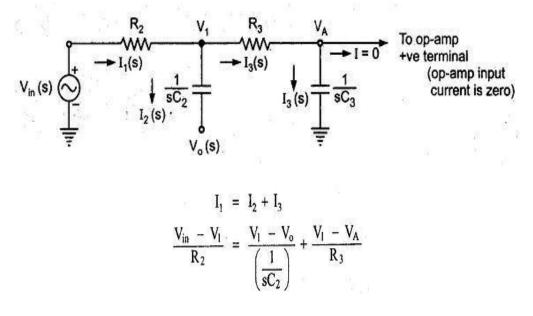

#### 3. Derive the voltage gain and transfer function of second order active filter. (Nov 2014)

#### 7.2.2 Second Order Active Filter

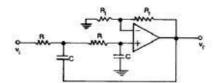

An improved filter response can be obtained by using a second order active filter. A second order filter consists of two RC pairs and has a roll-off rate of -40 dB/decade. A general second order filter (Sallen-Key filter) is shown in Fig. 7.3. The results derived here can be used for analysing low pass and high pass filters.

The op-amp is connected as non-inverting amplifier and hence,

Fig. 7.3 Salien-Key filter (General second order filter)

where

$$A_0 = 1 + \frac{R_c}{R_i}$$

(7.14)

and  $v_B$  is the voltage at node *B*. Kirchhoff's current law (KCL) at node A gives

$$v_i Y_1 = v_A (Y_1 + Y_2 + Y_3) - v_o Y_3 - v_B Y_2$$

$$= v_{\rm A} \left( Y_1 + Y_2 + Y_3 \right) - v_0 Y_3 - \frac{v_0 Y_2}{A_0}$$

(7.15)

where  $v_A$  is the voltage at node A.

-

KCL at node B gives,

H

$$v_{A}Y_{2} = v_{B}(Y_{2} + Y_{4}) = \frac{v_{b}(Y_{2} + Y_{4})}{A_{b}}$$

$$v_{A} = \frac{v_{b}(Y_{2} + Y_{4})}{A_{b}Y_{2}}$$

Substituting Eq. (7.16) in Eq. (7.15) and after simplification, we get the voltage gain as

$$\frac{a_{0}}{a_{1}} = \frac{A_{0}Y_{1}Y_{2}}{Y_{1}Y_{2} + Y_{4}(X_{1} + Y_{2} + Y_{5}) + Y_{2}Y_{3}(1 - A_{0})}$$

(7.17)

(7.16)

To make a low pass filter, choose,  $Y_1 = Y_2 = 1/R$  and  $Y_3 = Y_4 = sC$  as shown in Fig. 7.4. For simplicity, equal components have been used.

Fig. 7.4 Second order low-pass filter

From Eq. (7.17), we get the transfer function H(s) of a low pass filter as,

$$(s) = \frac{A_0}{s^2 C^2 R^2 + sCR (3 - A_0) + 1}$$

(7.18)

This is to note that from Eq. (7.18),  $H(0) = A_{o}$  for s = 0 and  $H(\infty) = 0$  for  $s = \infty$  and obviously the configuration is for low pass active filter. It may be noted that for minimum dc offset  $R_{i}R_{i}/(R_{i} + R_{i}) = R + R = 2R$  should be satisfied.

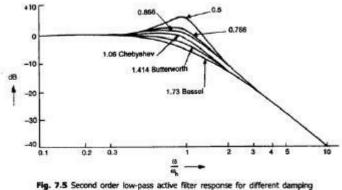

Second order physical systems have been studied extensively since long back and their step response, damping coefficient and its cause and effect relationship are known. We shall exploit those ideas in case of second order RC active filter. The transfer function of low pass second order system (electrical, mechanical, hydraulic or chemical) can be written as.

$$H(s) = \frac{A_s \omega_b^2}{s^2 + \alpha \omega_b s + \omega_b^2}$$