## **DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING**

## Subject Name: PULSE AND DIGITAL CIRCUITS

Subject Code: EE T45

## **UNIT – I LINEAR WAVE SHAPPING CIRCUITS**

Linear wave shaping circuits: RC, RL and RLC circuits – Pulse transformer – Steady state switching characteristics of devices– Clipping and clamping circuits–Switching circuits.

## DISCUSS ABOUT WORKING OF CLIPPER CIRCUIT IN DETAIL. [ NOV-2016]

1

### Definition:

- 1. The circuit with which the waveform is shaped by removing (or clipping) a portion of the input signal without distorting the remaining part of the alternating waveform is called a *clipper*.

- 2. Clipping circuits are also referred to as voltage (or current) limiters, amplitude selector or slicers.

- 3. The four general categories of clippers are

- 1. Positive clipper

- 1. Series Positive clipper

- 2. Shunt Positive clipper

- 2. Negative clipper

- 1. Series negative clipper

- 2. Shunt negative clipper

- 3. Biased clipper

- 4. Combinational clipper

#### Positive clipper:

#### Series Positive clipper:

- 4. In the series positive clipper when the input voltage is positive the diode does not conduct and acts as an open circuit and hence the positive half cycle does not appear at the output. i.e the positive half cycle is clipped off.

- 5. When the input signal is negative, the diode conducts and acts as a closed switch (short circuit), the negative half appears at the output as shown in figure below

#### Shunt Positive clipper:

- 6. When the input voltage is positive the diode conducts and acts as a short circuit and hence there is zero signal at the output i.e the positive half cycle is clipped off.

- 7. When the input signal is negative the diode does not conduct and acts as on open switch, the negative half cycle appears at the output as shown below

#### Negative clipper:

8. In the negative clipping circuit, the diode is connected in a direction opposite to that of a positive clipper.

Series negative clipper

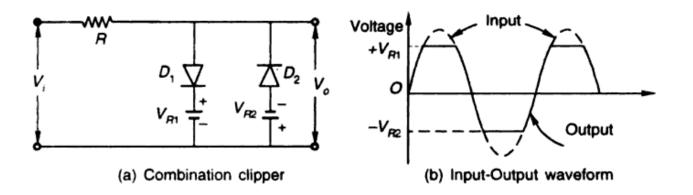

- 9. In the series negative clipper, during the positive half cycle of the input signal, the diode conducts and acts as a short circuit and hence the positive half cycle of the input signal will appear at the output as shown in figure.

- 10. During the negative half cycle of the input signal the diode does not conduct and acts as on open circuit.

- 11. The negative half cycle will not appear at the output i.e the negative half cycle is clipped off.

#### Shunt negative clipper

- 12. When the input signal is positive the diode does not conduct and acts as on open switch, the positive half cycle appears at the output as shown below

- 13. When the input voltage is negative the diode conducts and acts as a short circuit and hence there is zero signal at the output i.e the positive half cycle is clipped off.

#### **Biased clipper:**

#### Biased positive series clipper

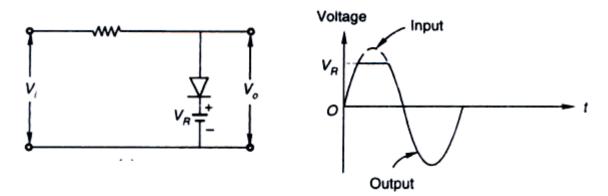

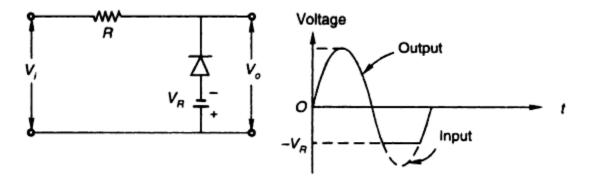

14. Figure shows the circuits of shunt and series type positive clipping along with input and output waveforms.

- 15. In the biased series positive clipper the diode does not conduct as long as the input voltage is greater than  $+V_R$  and hence the output remains at  $+V_R$ .

- 16. When the input voltage becomes less than  $+V_R$  the diode conducts and acts as a short circuit.

- 17. Hence all the input signals having less than  $+V_R$  as well as negative half cycle of the input wave will appear at the output

#### Biased positive shunt clipper

- 18. In the biased shunt positive clipper as shown in figure the diode conducts as long as the input voltage is greater than  $+V_R$  and hence the output remains at  $+V_R$ .

- 19. When the input voltage becomes less than  $+V_R$  the diode does not conducts and acts as a open circuit.

- 20. Hence all the input signals having less than  $+V_R$  as well as negative half cycle of the input wave will appear at the output

21. The clipping levels can be shifted up or down by varying the bias voltage  $+V_R$

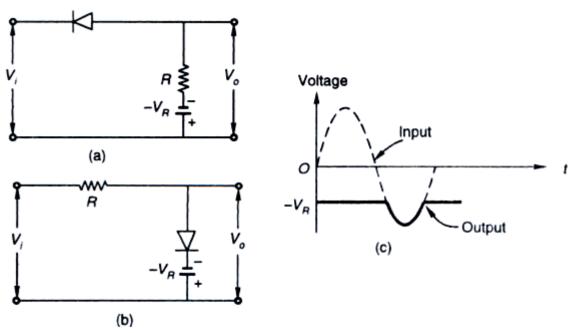

Biased positive clipper with reverse polarity of  $V_{R}$ . (a) Series, (b) Shunt, and (c) Input and output signal waveforms

- 22. Above figure shows the biased series and shunt clippers with reverse polarity of  $+V_R$  along with the input and output voltage waveforms.

- 23. Here the entire signal above  $-+V_R$  is clipped off

#### **Biased clipper:**

#### Biased negative series clipper

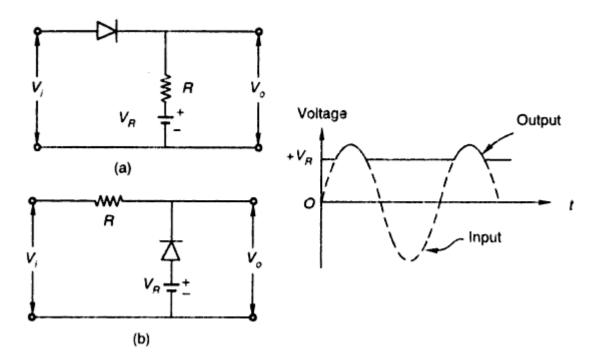

24. In the biased series negative clipper when the input voltage  $V_i \leq V_R$  the diode does not conduct and clipping takes place.

Biased negative shunt clipper

25. In the biased shunt negative clipper when the input voltage  $V_i \leq V_R$  the diode conducts and clipping takes place.

26. The clipping level can be shifted up and down by varying the bias voltage  $(-V_R)$

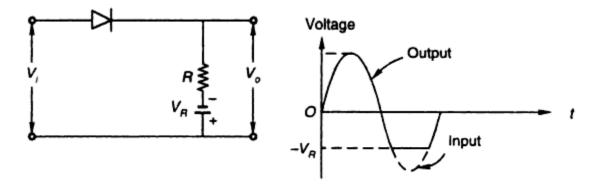

### Biased negative clipper with reverse polarity of the battery $V_{\text{R}}$

- 27. Above figure shows the biased series and shunt clippers with reverse polarity of  $+V_R$  along with the input and output voltage waveforms.

- 28. Here the entire signal above  $-+V_R$  is clipped off

#### Biased negative shunt clipper

- 29. This is the combination of a biased positive clipper and a biased negative clipper.

- 30. When the input signal voltage  $V_i \ge V_{R1}$  diode D1conducts and acts as a closed switch, while diode D2 is reverse biased and D2 acts as open switch.

- 31. Hence the output voltage cannot exceed the voltage level of  $+V_{R1}$  during the positive half cycle.

- 32. Similarly when the input signal voltage  $V_i \leq V_{R2}$  the diode D2 conducts and acts as closed switch while diode D1 is reverse biased and diode D1 acts as an open switch.

- 33. Hence the output voltage VO cannot go below the voltage level of  $-V_{R2}$  during the negative half cycle.

- 34. It is evident that the clipping levels may be changed by varying the values of  $V_{R1}$  and  $V_{R2}$ .

- 35. If  $V_{R1} = V_{R2}$  the circuit will clip both the positive and negative half cycles at the same viltage level and hence such a combination clipper is called *symmetric clipper*.

#### Applications of clippers:

- 1. Radars

- 2. Digital computers

- 3. Radio and television receivers etc

## DISCUSS ABOUT WORKING OF CLAMPERS CIRCUIT IN DETAIL.

#### Definition:

- 5. Clamping network shifts (clamps) a signal to a different DC level i.e it introduces a DC level to an AC signal.

- 6. Hence the clamping network is also known as *DC restorer*.

- 7. It is of two types

- 1. Negative voltage clamper

- 2. Positive voltage clamper

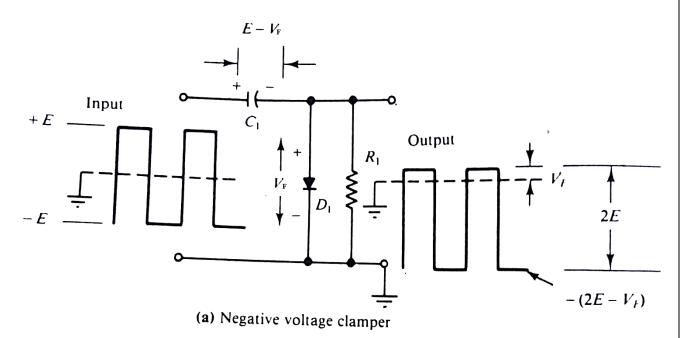

#### Negative voltage clamper

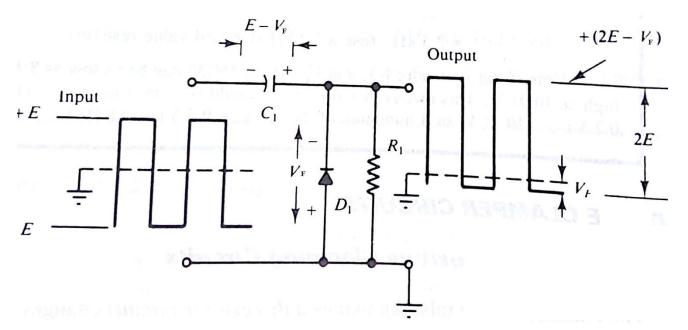

8. When the input is positive diode D1 is forward biased and capacitor C1 charges with the polarity as shown in figure below.

- 9. During the positive input peak the output cannot exceed the diode forward bias voltage  $V_{\rm F}$ .

- 10. At this time therefore the voltage on the right side of the capacitor is  $V_F$ , while on the left side of the capacitor the voltage is +E.

- 11. Thus the capacitor is charge to  $E-V_F$ , positive on the left and negative on the right as shown in above figure.

- 12. When the input switches to negative the diode is reverse biased and it has no further effect on the capacitor voltage.

- 13.  $R_1$  has a high resistance value and cannot discharge the capacitor significantly during the negative portion of the input waveform.

- 14. While the input is negative the output voltage is the sum of the input voltage and capacitor voltage.

- 15. Since the polarity of the capacitor voltage is the same as the (negative) input, the result is a negative output larger than the input voltage. Thus

Negative output =  $-E-(E-V_F) = -(2E - V_F)$

16. The peak to peak output is the difference between the negative and positive peak voltages

peak to peak output = (positive peak) - (negative peak)

$$= V_F - (2E - V_F)$$

$$= 2E$$

- 17. It is seen that the amplitude of the output waveform from the negative voltage clamper is exactly the same as that of the input.

- 18. The function of  $R_1$  is to discharge C1 over several cycles of the input waveform.

#### Negative voltage clamper

- 19. It functions exactly the same way as the negative voltage clamper. The diode connected as shown clamps the negative output peak at  $-V_F$ .

- 20. Capacitor C1 charges to E-V<sub>F</sub> positive on the right and negative on the left.

- 21. The positive output then becomes  $2E V_F$

#### Applications:

22. These circuits find application in television receivers to restore the DC reference signal to the video signal.

## EXPLAIN IN DETAIL ABOUT STEADY STATE SWITCHING CHARACTERISITCS OF PN DIODE.

1. Diodes are often used in a switching mode.

23.

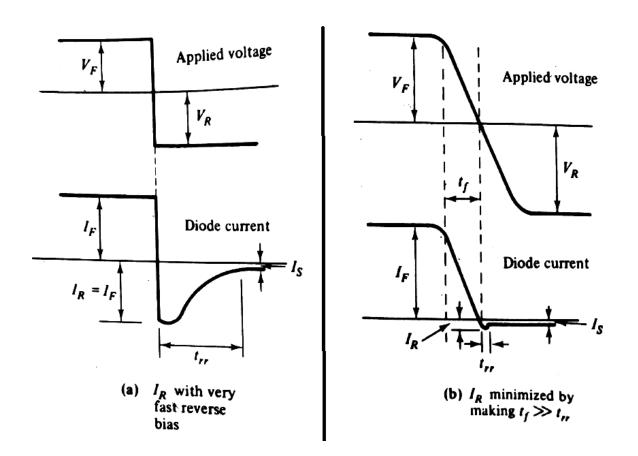

- 2. When the applied bias voltage to the PN diode is suddenly reversed in the opposite direction, the diode response reaches a steady state after an interval of time called *recovery time*.

- 3. The *forward recovery time* ( $T_{fr}$ ) is defined as the time required for forward voltage or current to reach a value after switching diode from its reverse to forward biased state.

- 4. The *reverse recovery time*  $(T_{rr})$  is defined as the time required for reverse voltage or current to reach a value after switching diode from its forward to reverse biased state.

- 5. Most diodes switch very quickly into the forward biased condition; however there is a longer turnoff time owing to the junction diffusion in reverse biased condition.

- 6. When the PN junction diode is forward biased, the minority electron concentration in the P region is approximately linear.

- 7. If the junction is suddenly reverse biased at  $t_1$ , then because of stored electronic charge, the reverse current  $I_R$  is initially of the same magnitude as the forward current  $I_F$ .

- 8. When the pulse switches from positive to negative, the diode conducts in reverse instead of switching off sharply.

- 9. The reverse current  $I_R$  initially equals the forward current  $I_F$ , then it gradually decreases towards zero.

- 10. The high level of reverse of reverse current occurs because at the instant of reverse bias there are charge carriers crossing the junction depletion region, and these must be removed.

- 11. The typical values of reverse recovery time  $T_{rr}$  for switching diode ranges from 4ns to 50ns.

- 12. After the instant  $t = t_2$  the diode gradually recovers and ultimately reaches the steady state.

- 13. During the interval from  $t_1$  to  $t_2$ , the injected minority carrier have remained stored & hence this time interval is called *storage time t<sub>s</sub>*

- 14. The time interval between  $t_2 \& t_3$  when the diode has recovered nominally is called *transition time t<sub>t</sub>*.

Figure: Switching characteristics of PN junction diode

# EXPLAIN IN DETAIL ABOUT STEADY STATE SWITCHING CHARACTERISITCS OF TRANSISTOR.

15.

1.

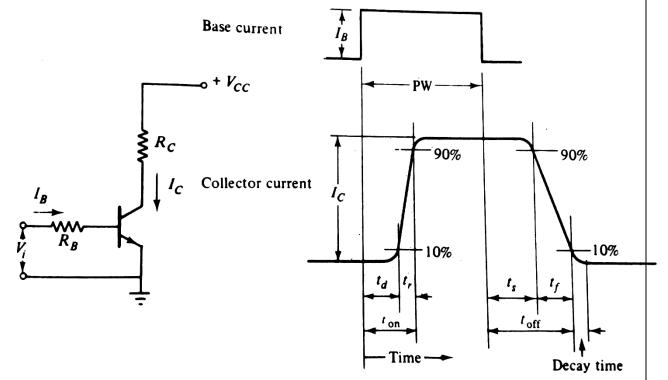

- 1. Transistor can be used as a witch. One important characteristics of a switching transistor is the speed with which it can be switched ON and OFF.

- 2. Consider the figure shown below where the time relationship between collector current and base current is shown.

*Time relationship between base current and collector current in a transistor switch* When the input current  $I_B$  is applied, the transistor does not switch ON immediately.

- 2. The time between application of base current and commencement of collector current is termed *delay time*  $t_d$

- 3. The *delay time*  $t_d$  is defined as the time required for I<sub>C</sub> to reach 10% of its final level after I<sub>B</sub> has commenced.

- 4. Even when the transistor begins to switch on a finite time elapses before  $I_C$  reaches its maximum level.

- 5. The *rise time t<sub>r</sub>* is defined as time it takes for  $I_C$  to go from 10% to 90% of its maximum level.

- 6. The *turn on time t<sub>on</sub>* for the transistor is the sum of  $t_d$  and  $t_r$ .

- 7. Similarly a transistor cannot be switched off instantaneously.

- 8. The *turn off time*  $t_{off}$  is composed of a *storage time*  $t_s$  and a *fall time*  $t_f$ . The storage time results from the fact that the collector base junction is forward biased when the transistor is in saturation.

- 9. Charge carriers crossing a forward junction are trapped in the depletion region when the junction is reversed.

- 10. These charge carrier must be withdrawn or made to recombine with charge carriers of an opposite type before the collector current begins to fall.

- 11. The *storage time t<sub>s</sub>* is defined as the time between  $I_B$  switch off and  $I_C$  falling to 90% of its maximum level.

- 12. The fall time tf is the time required for  $I_C$  to fall from 90% to 10% of its maximum.

- 13. Decay time is included in turn off time and it is the time required for  $I_C$  to go from its 10% level to  $I_{CO}$ .

- 14. From data sheet for general purpose transistor 2N3904 the turn on and turn off times are

Turn on time  $t_{on} = t_d + t_r = 35ns + 35ns = 70ns$

Turn off time toff =  $t_s + t_f = 200ns + 50 ns = 250ns$

## 15. DRAW AND EXPLAIN THE RESPONSE OF LOW PASS RC CIRCUIT FOR THE FOLLOWING INPUT

- 1. SINUSOIDAL INPUT

- 2. STEP VOLTAGE INPUT

- 3. PULSE INPUT

- 4. SQUARE WAVE INPUT

- 5. RAMP INPUT

- 6. EXPONENTIAL INPUT

#### LOW PASS RC CIRCUIT

- 1. A low pass RC circuit is a circuit which transmits only low frequency signals and stops high frequency signals.

- 2. At  $f = 0 \rightarrow XC = \infty$  i.e open circuit

- 3. Thus the entire input appears at the output so the output is same as the input and the gain is unity.

$$A = \frac{v_0}{v_i} = 1$$

1. As frequency increases,  $X_C$  decreases so the circuit acts as short circuit and output falls to zero (i.e f increases then  $X_C$  decreases, so that circuit behaves like a short circuit.)

#### 1. LOW PASS RC CIRCUIT FOR A SINUSOIDAL INPUT

- 2. The gain versus frequency curve is excited by a sinusoidal input. The curve is obtained by keeping input signal constant and varying the frequency.

- 3. At low frequency the output is equal to the input hence the gain is unity. |A| = 1

- 4. As the frequency increases the output decreases and gain decreases.

- 5. The frequency at which gain is  $\frac{1}{\sqrt{2}} = 0.707$  of its maximum value is called the cut off frequency.

- 6. For low pass filter there is no lower cut off frequencies.

- 7. The upper cutoff frequency is the frequency at which the gain is  $\frac{1}{\sqrt{2}} = 0.707$  i.e 70% of its maximum value.

- 8. The bandwidth of the low pass circuit is equal to the upper cut off frequency  $f_2$  itself.

Apply KVL

$Vi(t) = i(t) R + \frac{1}{c} \int i(t) dt$  -----(1)

$$V_0(t) = \frac{1}{c} \int i(t) dt$$

-----(2)

Taking laplace transform for (1) & (2)

$$RI(S) + \frac{1}{c} \frac{I(S)}{S} = V_i(S)$$

$$\frac{1}{c} \frac{I(S)}{S} = V_0(S)$$

For the network shown the magnitude of the steady state gain A is given by

$$A = \frac{V_0(S)}{V_i(S)}$$

$$A = \frac{\frac{1}{C}\frac{I(S)}{S}}{RI(S) + \frac{1}{C}\frac{I(S)}{S}} = \frac{\frac{1}{C}\frac{I(S)}{S}}{I(S)\left(R + \frac{1}{SC}\right)}$$

$$A = \frac{\frac{1}{SC}}{(R + \frac{1}{SC})} = \frac{\frac{1}{SC}}{(\frac{SRC + 1}{SC})}$$

$$A = \frac{1}{(SRC + 1)}$$

Put S= j\omega = j2\pi f

$$A = \frac{1}{(1 + j2\pi fRC)}$$

$$|A| = \frac{1}{\sqrt{1 + (j2\pi fRC)^2}}$$

At upper cut off frequency  $f_2$

$$|A| = \frac{1}{\sqrt{2}}$$

$$|A| = \frac{1}{\sqrt{1 + (j2\pi fRC)^2}}$$

Squaring both sides and equating the denominators

$$2 = 1 + (j2\pi fRC)^2$$

The upper cut off frequency  $f2 = \frac{1}{2\pi RC}$

Substitute f2 in equation (3)

$$|A| = \frac{1}{\sqrt{1 + \left(\frac{f}{f_2}\right)^2}}$$

The angle  $\Theta$  by which the output leads the input is given by  $\Theta = \tan^{-1} \left( \frac{f}{f_2} \right)$

► (3)

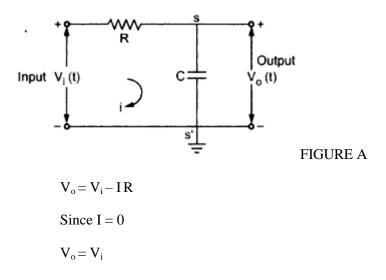

#### 9. LOW PASS RC CIRCUIT FOR A STEP VOLTAGE INPUT

- 10. A step signal is the one which maintains the value zero for all times t < 0, and maintains the value V for all times t > 0.

- 11. The transition between the two voltage levels takes place at t = 0

- 12. In the low pass RC circuit as shown in figure A, if the capacitor is initially uncharged, when a step input is applied, since the voltage across the capacitor cannot change simultaneously the output will be zero at t=0.

- 13. As the capacitor charges the output voltage rises exponentially towards the steady state value V with a time constant RC as shown in above figure.

Let  $\boldsymbol{V}^l$  be the initial voltage across the capacitor

Apply KVL

$$V_i(t) = i(t) R + \frac{1}{c} \int i(t) dt$$

-----(1)

Differentiating the above equation

$$\frac{dV_{i}(t)}{dt} = \frac{di(t)}{dt}R + \frac{1}{c}i(t)$$

$$V_i(t) = V$$

$\frac{dV_i(t)}{dt} = 0$

$$0 = \frac{di(t)}{dt} R + \frac{1}{c} i(t)$$

Taking laplace transform on both sides

$$0 = [SI(S) - I(0)]R + \frac{I(S)}{c}$$

$$RI(0) = [RSI(S) + \frac{I(S)}{c}]$$

$$RI(0) = I(S)[RS + \frac{1}{c}]$$

$$I(0) = I(S) \left[S + \frac{1}{RC}\right]$$

The initial current I(0) is given by  $I(0) = \frac{v - v^{l}}{R}$

Substituting we get

$$\frac{v - v^{l}}{R} = I(S) \left[S + \frac{1}{RC}\right]$$

$$I(S) = \frac{v - v^{l}}{R[S + \frac{1}{RC}]}$$

$$V_{o}(S) = V_{i}(S) - I(S)R$$

$$V_{o}(S) = \frac{v}{S} - \frac{v - v^{l}}{R[S + \frac{1}{RC}]}R = \frac{v}{S} - \frac{v - v^{l}}{[S + \frac{1}{RC}]}$$

Taking inverse laplace transform on both sides

$$\mathbf{V}_{\mathrm{o}}(t) = V - [V - \mathbf{V}^{\mathrm{l}}] \mathrm{e}^{-\mathrm{t}/\mathrm{RC}}$$

If the capacitor is initially uncharged then  $V_o(t) = V [1 - e^{-t/RC}]$

The rise time  $t_r = 2.2RC$

This indicates that the rise time t<sub>r</sub> is proportional to the time constant RC of the circuit

#### 14. LOW PASS RC CIRCUIT FOR A PULSE INPUT

15. LOW PASS RC CIRCUIT FOR A SQUARE WAVE INPUT

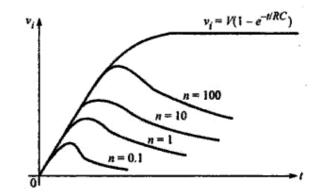

16. LOW PASS RC CIRCUIT FOR A RAMP INPUT

17. LOW PASS RC CIRCUIT FOR A EXPONENTIAL WAVE INPUT

18.

Taking the inverse Laplace transform on both sides and letting  $RC/\tau = n$ ,

$$v_o(t) = V \left[ 1 - \frac{e^{-t/\tau}}{1 - n} + \frac{e^{-t/RC}}{\frac{1}{n} - 1} \right]$$

If  $t/\tau = x$ , then  $v_o(t) = V \left[ 1 - \frac{e^{-x}}{1 - n} + \frac{n}{1 - n} e^{-x/n} \right]$ , if  $n \neq 1$

if  $v_o(t) = 1 - (1 + x)e^{-x}$ , if  $n = 1$

and

These are the expressions for the voltage across the capacitor of a low-pass RC circuit excited by an exponential input of rise time  $t_{r1} = 2.2\tau$ .

If an exponential of rise time  $t_{r1}$  is passed through a low-pass circuit with rise time  $t_{r2}$ , the rise time of the output waveform  $t_r$  will be given by an empirical relation,  $t_r = 1.05\sqrt{t_{r1}^2 + t_{r2}^2}$ . This is same as the rise time obtained when a step is applied to a cascade of two circuits of rise times  $t_{r1}$  and  $t_{r2}$  assuming that the second circuit does not load the first.

## DRAW AND EXPLAIN THE RESPONSE OF HIGH PASS RC CIRCUIT FOR THE FOLLOWING INPUT

- 1. SINUSOIDAL INPUT

- 2. STEP VOLTAGE INPUT

- 3. PULSE INPUT

- 4. SQUARE WAVE INPUT

- 5. RAMP INPUT

- 6. EXPONENTIAL INPUT

#### HIGH PASS RC CIRCUIT

19.

Figure 1.30 shows a high-pass RC circuit. At zero frequency the reactance of the capacitor is infinity and so it blocks the input and hence the output is zero. Hence, this capacitor is called the *blocking capacitor* and this circuit, also called the *capacitive coupling circuit*, is used to provide dc isolation between the input and the output. As the frequency increases, the reactance of the capacitor decreases and hence the output and gain increase. At very high frequencies, the capacitive reactance is very small so a very small voltage appears across C and, so the output is almost equal to the input and the gain is equal to 1. Since this circuit attenuates low-frequency signals and allows transmission of high-frequency signals with little or no attenuation, it is called a high-pass circuit.

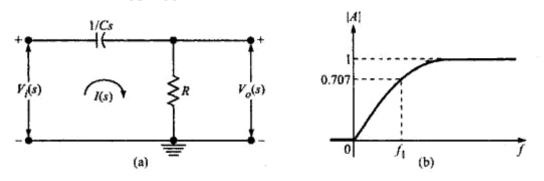

#### 1. HIGH PASS RC CIRCUIT FOR A SINUSOIDAL INPUT

Figure 1.31(a) shows the Laplace transformed high-pass RC circuit. The gain versus frequency curve of a high-pass circuit excited by a sinusoidal input is shown in Figure 1.31(b). For a sinusoidal input  $v_i$ , the output signal  $v_o$  increases in amplitude with increasing frequency. The frequency at which the gain is  $1/\sqrt{2}$  of its maximum value is called the lower cut-off or lower 3-dB frequency. For a high-pass circuit, there is no upper cut-off frequency because all high frequency signals are transmitted with zero attenuation. Therefore,  $f_2 = \infty$ . Hence bandwidth =  $f_2 - f_1 = \infty$ .

Figure 1.31 (a) Laplace transformed high-pass circuit and (b) gain versus frequency plot.

#### Expression for the lower cut-off frequency

For the high-pass RC circuit shown in Figure 1.31(a), the magnitude of the steady-state gain A, and the angle  $\theta$  by which the output leads the input are given by

$$A = \frac{V_o(s)}{V_i(s)} = \frac{R}{R + \frac{1}{Cs}} = \frac{1}{1 + \frac{1}{RCs}}$$

Putting

$$s = j\omega, \ A = \frac{1}{1 - j\frac{1}{\omega RC}} = \frac{1}{1 - j\frac{1}{2\pi fRC}}$$

$$\therefore \qquad |A| = \frac{1}{\sqrt{1 + \left(\frac{1}{2\pi fRC}\right)^2}} \quad \text{and} \quad \theta = -\tan^{-1}\frac{1}{2\pi fRC}$$

÷

*.* .

At the lower cut-off frequency

$$f_i$$

,  $|A| = 1/\sqrt{2}$

$$\frac{1}{\sqrt{1 + \left(\frac{1}{2\pi f_1 RC}\right)^2}} = \frac{1}{\sqrt{2}}$$

Squaring and equating the denominators,

$$\frac{1}{2\pi f_1 RC} = 1$$

i.e.  $f_1 = \frac{1}{2\pi RC}$

This is the expression for the lower cut-off frequency of a high-pass circuit.

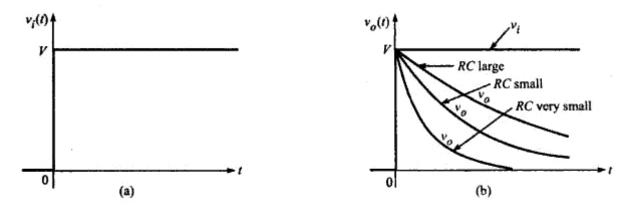

#### 2. HIGH PASS RC CIRCUIT FOR A STEP INPUT

When a step signal of amplitude V volts shown in Figure 1.32(a) is applied to the high-pass RC circuit of Figure 1.30, since the voltage across the capacitor cannot change instantaneously the output will be just equal to the input at t = 0 (for t < 0,  $v_i = 0$  and  $v_o = 0$ ). Later when the capacitor charges exponentially, the output reduces exponentially with the same time constant RC. The expression for the output voltage for t > 0 is given by

$$V_o(t) = V_f - (V_f - V_{in})e^{-t/RC} = 0 - (0 - V)e^{-t/RC} = Ve^{-t/RC}$$

Figure 1.32(b) shows the response of the circuit for large, small, and very small time constants.

For  $t > 5\tau$ , the output will reach more than 99% of its final value. Hence although the steady state is approached asymptotically, for most applications we may assume that the final value has been reached after  $5\tau$ . If the initial slope of the exponential is maintained, the output falls to zero in a time  $t = \tau$ .

The voltage across a capacitor can change instantaneously only when an infinite current passes through it, because for any finite current i(t) through the capacitor, the instantaneous

change in voltage across the capacitor is given by  $\frac{1}{C}\int_0^0 i(t) dt = 0$ .

Figure 1.32 (a) Step input and (b) step response for different time constants.

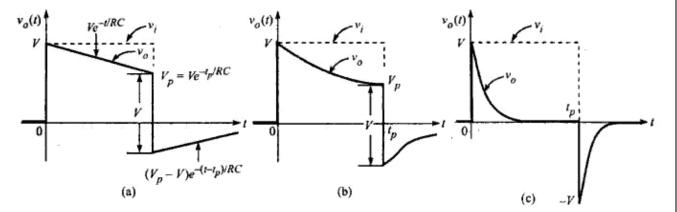

3. HIGH PASS RC CIRCUIT FOR A PULSE INPUT

A pulse of amplitude V and duration  $t_p$  shown in Figure 1.4(a) is nothing but the sum of a positive step of amplitude V starting at t = 0 and a negative step of amplitude V starting at  $t_p$  as shown in Figure 1.4(b). So, the response of the circuit for  $0 < t < t_p$  for the pulse input is the same as that for a step input and is given by  $v_o(t) = Ve^{-t/RC}$ . At  $t = t_p$ ,  $v_o(t) = V_p = Ve^{-t_p/RC}$ . At  $t = t_p$ , since the input falls by V volts suddenly and since the voltage across the capacitor cannot change instantaneously, the output also falls suddenly by V volts to  $V_p - V$ . Hence at  $t = t_{p^+}$ ,  $v_o(t) = Ve^{-t_p/RC} - V$ . Since  $V_p < V$ ,  $V_p - V$  is negative. So there is an undershoot at  $t = t_p$  and hence for  $t > t_p$ , the output is negative. For  $t > t_p$ , the output rises exponentially towards zero with a time constant RC according to the expression  $(Ve^{-t_p/RC} - V)e^{-(t-t_p)/RC}$ .

The output waveforms for  $RC >> t_p$ , RC comparable to  $t_p$  and  $RC << t_p$  are shown in Figures 1.33(a), (b), and (c) respectively. There is distortion in the outputs and the distortion is the least when the time constant is very large. Observe that there is positive area and negative area in the output waveforms. The negative area will always be equal to the positive area. So if the time constant is very large the tilt (the almost linear decrease in the output voltage) will be small and hence the undershoot will be very small, and for  $t > t_p$ , the output rises towards the zero level very very slowly. If the time constant is very small compared to the pulse width (i.e.  $RC/t_p \ll 1$ ), the output consists of a positive spike or pip of amplitude V volts at the beginning of the pulse and a negative spike of the same amplitude at the end of the pulse. Hence a high-pass circuit with a very small time constant is called a *peaking circuit* and this process of converting pulses into pips by means of a circuit of short time constant is called peaking.

Figure 1.33 Pulse response for (a)  $RC >> t_p$ , (b) RC comparable to  $t_p$  and (c)  $RC \ll t_p$ .

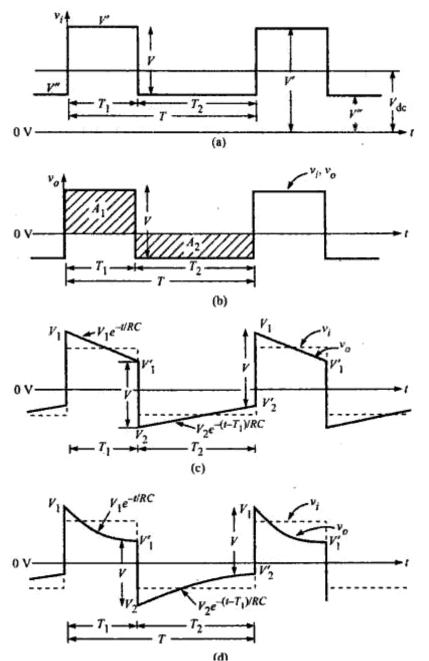

#### 4. HIGH PASS RC CIRCUIT FOR A SQUARE WAVE INPUT

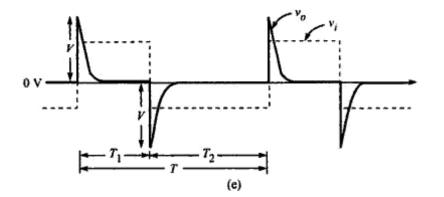

A square wave shown in Figure 1.34(a) is a periodic waveform, which maintains itself at one constant level V' with respect to ground for a time  $T_1$  and then changes abruptly to another level V'' and remains constant at that level for a time  $T_2$ , and then repeats itself at regular intervals of  $T = T_1 + T_2$ . A square wave may be treated as a series of positive and negative steps. The shape of the output depends on the time constant of the circuit. Figures 1.34(b), 1.34(c), 1.34(d), and 1.34(e) show the output waveforms of the high-pass RC circuit under steady-state conditions for the cases (a) RC >> T, (b) RC > T, (c) RC = T, and (d) RC << T respectively.

When the time constant is arbitrarily large (i.e.  $RC/T_1$  and  $RC/T_2$  are very very large in comparison to unity) the output is same as the input but with zero dc level. When RC > T, the output is in the form of a tilt. When RC is comparable to T, the output rises and falls exponentially. When RC << T (i.e.  $RC/T_1$  and  $RC/T_2$  are very very small in comparison to unity), the output consists of alternate positive and negative spikes. In this case the peak-to-peak amplitude of the output is twice the peak-to-peak value of the input.

Figure 1.34 (a) A square wave input, (b) output when RC is arbitrarily large, (c) output when RC > T, (d) output when RC is comparable to T, and (e) output when RC << T.

In fact, for any periodic input waveform under steady-state conditions, the average level of the output waveform from the high-pass circuit of Figure 1.30 is always zero independently of the dc level of the input. The proof is as follows:

Writing KVL around the loop of Figure 1.30,

$$v_i(t) = \frac{1}{C} \int i(t) dt + v_o(t)$$

$$= \frac{1}{RC} \int v_o(t) dt + v_o(t) \qquad \left( \because i(t) = \frac{v_o(t)}{R} \right)$$

Differentiating,

i.e.

$$\frac{dv_i(t)}{dt} = \frac{v_o(t)}{RC} + \frac{dv_o(t)}{dt}$$

Multiplying by dt and integrating this equation over one period T,

$$\int_{t=0}^{t=T} dv_i(t) = \int_{t=0}^{t=T} \frac{v_o(t) dt}{RC} + \int_{t=0}^{t=T} dv_o(t)$$

$$v_i(T) - v_i(0) = \frac{1}{RC} \int_0^T v_o(t) dt + v_o(T) - v_o(0)$$

Under steady-state conditions, the output waveform (as well as the input signal) is repetitive with a period T so that  $v_o(T) = v_o(0)$  and  $v_i(T) = v_i(0)$ .

Hence  $\int_0^T v_o(t) dt = 0$ . Since this integral represents the area under the output waveform

over one cycle, we can say that the average level of the steady-state output signal is always zero.

This can also be proved based on frequency domain analysis as follows.

The periodic input signal may be resolved into a Fourier series consisting of a constant term and an infinite number of sinusoidal components whose frequencies are multiples of f = 1/T. Since the blocking capacitor presents infinite impedance to the dc input voltage, none of these dc components reach the output under steady-state conditions. Hence the output signal is a sum of sinusoids whose frequencies are multiples of f. This waveform is therefore periodic with a fundamental period T but without a dc component.

With respect to the high-pass circuit of Figure 1.30, we can say that:

- The average level of the output signal is always zero, independently of the average level of the input. The output must consequently extend in both negative and positive directions with respect to the zero voltage axis and the area of the part of the waveform above the zero axis must equal the area which is below the zero axis.

- 2. When the input changes abruptly by an amount V, the output also changes abruptly by an equal amount and in the same direction.

- During any finite time interval when the input maintains a constant level, the output decays exponentially towards zero voltage.

Under steady-state conditions, the capacitor charges and discharges to the same voltage levels in each cycle. So the shape of the output waveform is fixed.

For  $0 < t < T_1$ , the output is given by  $v_{o1} = V_1 e^{-t/RC}$ At  $t = T_1$ ,  $v_{o1} = V_1' = V_1 e^{-T_1/RC}$

For  $T_1 < t < T_1 + T_2$ , the output is  $v_{o2} = V_2 e^{-(t-T_1)/RC}$

At

$$t = T_1 + T_2$$

,  $v_{o2} = V_2' = V_2 e^{-T_2/RC}$

Also  $V_1' - V_2 = V$  and  $V_1 - V_2' = V$

From these relations  $V_1$ ,  $V'_1$ ,  $V_2$  and  $V'_2$  can be computed.

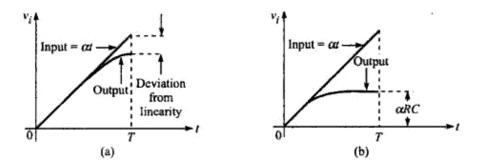

#### 5. HIGH PASS RC CIRCUIT FOR A RAMP INPUT

A waveform which is zero for t < 0 and which increases linearly with time for t > 0 is called a ramp or sweep voltage.

When the high-pass RC circuit of Figure 1.30 is excited by a ramp input  $v_i(t) = \alpha t$ , where  $\alpha$  is the slope of the ramp, then

$$V_i(s) = \frac{\alpha}{s^2}$$

From the Laplace transformed circuit of Figure 1.31(a),

$$V_o(s) = V_i(s) \frac{R}{R + \frac{1}{Cs}} = \frac{\alpha}{s^2} \frac{RCs}{1 + RCs}$$

$$= \frac{\alpha}{s\left(s + \frac{1}{RC}\right)} = \alpha RC \left(\frac{1}{s} - \frac{1}{s + \frac{1}{RC}}\right)$$

Taking the inverse Laplace transform on both sides,  $v_o(t) = \alpha RC(1 - e^{-t/RC})$

For times t which are very small in comparison with RC, we have

$$v_o(t) = \alpha RC \left[ 1 - \left\{ 1 + \left(\frac{-t}{RC}\right) + \left(\frac{-t}{RC}\right)^2 \frac{1}{2!} + \left(\frac{-t}{RC}\right)^3 \frac{1}{3!} + \dots \right\} \right]$$

$$= \alpha RC \left[ \frac{t}{RC} - \frac{t^2}{2(RC)^2} + \dots \right]$$

$$= \alpha t - \frac{\alpha t^2}{2RC} = \alpha t \left( 1 - \frac{t}{2RC} \right)$$

Figure 1.36 shows the response of the high-pass circuit for a ramp input when (a) RC >> T, and (b) RC << T, where T is the duration of the ramp. For small values of T, the output signal falls away slightly from the input as shown in the Figure 1.36(a).

Figure 1.36 Response of the high-pass circuit for a ramp input when (a) RC >> T and (b) RC << T.

When a ramp signal is transmitted through a linear network, the output departs from the input. A measure of the departure from linearity expressed as the transmission error  $e_t$  is defined as the difference between the input and the output divided by the input. The transmission error at a time t = T is then

$$e_{t} = \frac{v_{i} - v_{o}}{v_{i}} \bigg|_{t=T} \approx \frac{\alpha t - \alpha t \left(1 - \frac{t}{2RC}\right)}{\alpha t} \bigg|_{t=T} \approx \frac{T}{2RC} = \pi f_{1}T$$

where  $f_1 = \frac{1}{2\pi RC}$  is the lower 3-dB frequency of the high-pass circuit.

For large values of t in comparison with RC, the output approaches the constant value  $\alpha RC$  as indicated in Figure 1.36(b).

#### 6. HIGH PASS RC CIRCUIT FOR A EXPONENTIAL INPUT

When the high-pass RC circuit of Figure 1.30 is excited by an exponential input  $v_i(t) = V(1 - e^{-t/\tau})$  shown in Figure 1.8, where  $\tau$  is the time constant of the input, the output taken across the resistor is given by

$$v_R(t) = v_i(t) - v_C(t)$$

For an exponential input  $v_i(t) = V(1 - e^{-t/\tau})$ , the expression for the voltage across the capacitor (derived earlier while dealing with *RC* low-pass circuit) is

$$v_{o}(t) = V\left(1 - \frac{e^{-x}}{1 - n} + \frac{n}{1 - n}e^{-x/n}\right)$$

$$v_{R}(t) = V(1 - e^{-t/\tau}) - V\left(1 - \frac{e^{-x}}{1 - n} + \frac{n}{1 - n}e^{-x/n}\right)$$

$$= V(1 - e^{-x}) - V\left(1 - \frac{e^{-x}}{1 - n} + \frac{n}{1 - n}e^{-x/n}\right)$$

$$= V\left(\frac{e^{-x}}{1 - n} - e^{-x}\right) - V\left(\frac{ne^{-x/n}}{1 - n}\right)$$

$$= V\left[e^{-x}\left(\frac{1}{1 - n} - 1\right) - \frac{n}{1 - n}e^{-x/n}\right]$$

$$= V\frac{n}{n - 1}[e^{-x/n} - e^{-x}], \text{ if } n \neq 1$$

$$v_{R}(t) = Vxe^{-x}, \text{ if } n = 1$$

and

۰.

If the time constant of the circuit is very high, n is high and the second term of the equation for  $n \neq 1$  is negligible compared to the first term except for small values of time.

$$\therefore \qquad \qquad v_o \approx V \frac{n}{n-1} e^{-x/n} \approx V e^{-t/RC}$$

This equation agrees with the way the circuit should behave for an ideal step voltage. The response of the high-pass circuit for different values of n is shown in Figure 1.37.

Figure 1.37 Response of high-pass circuit for exponential input.

Near the origin of time the output follows the input. Also, the smaller the circuit time constant, the smaller will be the output peak and the narrower will be the pulse. The larger the circuit time constant, the larger will be the peak output and also the wider will be the pulse.

The maximum output occurs when

$$\frac{dv_o}{dt} = 0$$

i.e.

$$\frac{d}{dt}\left[V\frac{n}{n-1}\left(e^{-x/n} - e^{-x}\right)\right] = 0$$

i.e.

$$V\frac{n}{n-1}\left[\left(\frac{-1}{n}\right)\left(\frac{1}{\tau}\right)e^{-x/n} - e^{-x}\left(-\frac{1}{\tau}\right)\right] = 0$$

i.e.

$$V\frac{n}{n-1}\left[\frac{e^{-x}}{\tau} - \frac{e^{-xn}}{n\tau}\right] = 0$$

$$\therefore \qquad e^{-x} = \frac{e^{-x/n}}{n}$$

i.e.

$$n = e^{x(1 - (1/n))} = e^{x((n-1)/n)}$$

i.e.

$$\ln n = \frac{x(n-1)}{n}$$

or  $x = \frac{n}{n-1} \ln n$

Since  $x = t/\tau$ , the time to rise to peak  $t_p$  is given by

Also,

$$t_{p} = \tau \frac{n}{n-1} \ln n$$

$$-x = \frac{-n}{n-1} \ln n = \ln [n^{n/(1-n)}]$$

To obtain the maximum value of output, substitute this value of -x in the expression for  $v_o(t)$

$$V_{o}(\max) = \frac{Vn}{n-1} \exp\left[\frac{1}{n} \ln(n^{n/(1-n)}) - \ln(n^{n/(1-n)})\right]$$

$$= V \frac{n}{n-1} \exp\left[\ln(n^{1/(1-n)}) - \ln(n^{n/(1-n)})\right]$$

$$= V \frac{n}{n-1} \left[n^{(1/(1-n))} - n^{(n/(1-n))}\right]$$

$$= \frac{V}{n-1} \left[n^{1+(1/(1-n))} - n^{1+(n/(1-n))}\right]$$

$$= \frac{V}{n-1} \left[n^{n/(1-n)} - n^{1/(1-n)}\right]$$

$$= \frac{V}{n-1} \left[n^{1/(1-n)}(n-1)\right]$$

$$= Vn^{1/(1-n)}, \quad \text{for } n \neq 1$$

$$\frac{V_{o}(\max)}{V} = n^{1/(1-n)}, \quad \text{for } n \neq 1$$

39

## EXPLAIN DIFFERENTIATING CIRCUIT AND DERIVE THE CONDITION FOR THE ACHIEVEMENT OF GOOD DIFFERENTIATION.[APRIL 2016]

When the time constant of the high-pass RC circuit is very very small, the capacitor charges very quickly; so almost all the input  $v_i(t)$  appears across the capacitor and the voltage across the resistor will be negligible compared to the voltage across the capacitor. Hence the current is determined entirely by the capacitance. Then the current

$$i(t) = C \frac{dv_i(t)}{dt}$$

and the output signal across R is

7

$$v_o(t) = RC \frac{dv_i(t)}{dt}$$

Thus we see that the output is proportional to the derivative of the input.

The high-pass RC circuit acts as a differentiator provided the RC time constant of the circuit is very small in comparison with the time required for the input signal to make an appreciable change.

The derivative of a step signal is an impulse of infinite amplitude at the occurrence of the discontinuity of step. The derivative of an ideal pulse is a positive impulse followed by a delayed negative impulse, each of infinite amplitude and occurring at the points of discontinuity. The derivative of a square wave is a waveform which is uniformly zero except at the points of discontinuity. At these points, precise differentiation would yield impulses of infinite amplitude, zero width and alternating polarity. For a square wave input, an RC high-pass circuit with very small time constant will produce an output, which is zero except at the points of discontinuity. At these points of discontinuity, there will be peaks of finite amplitude V. This is because the voltage across R is not negligible compared with that across C.

An RC differentiator converts a triangular wave into a square wave.

For the ramp  $v_i = \alpha t$ , the value of  $RC(dv/dt) = \alpha RC$ . This is true except near the origin. The output approaches the proper derivative value only after a lapse of time corresponding to several time constants. The error near t = 0 is again due to the fact that in this region the voltage across R is not negligible compared with that across C.

If we assume that the leading edge of a pulse can be approximated by a ramp, then we can measure the rate of rise of the pulse by using a differentiator. The peak output is measured on an oscilloscope, and from the equation  $v_o = \alpha RC$ , we see that this voltage divided by the product RC gives the slope  $\alpha$ .

A criteria for good differentiation in terms of steady-state sinusoidal analysis is, that if a sine wave is applied to the high-pass RC circuit, the output will be a sine wave shifted by a leading angle  $\theta$  such that:

$$\tan \theta = \frac{X_C}{R} = \frac{1}{\omega RC}$$

with the output being proportional to  $\sin(\omega t + \theta)$ . In order to have true differentiation, we must obtain  $\cos \omega t$ . In other words,  $\theta$  must equal 90°. This result can be obtained only if R = 0 or C = 0. However, if  $\omega RC = 0.01$ , then  $1/\omega RC = 100$  and  $\theta = 89.4^{\circ}$ , which is sufficiently close to 90° for most purposes. If  $\omega RC = 0.1$ , then  $\theta = 84.3^{\circ}$  and for some applications this may be close enough to 90°.

If the peak value of input is  $V_m$ , the output is

$$v_o = \frac{V_m R}{\sqrt{R^2 + \frac{1}{\omega^2 C^2}}} \sin(\omega t + \theta)$$

and if  $\omega RC \ll 1$ , then the output is approximately  $V_m \omega RC \cos \omega t$ . This result agrees with the expected value  $RC(dv_i/dt)$ . If  $\omega RC = 0.01$ , then the output amplitude is 0.01 times the input amplitude.

## EXPLAIN INTEGRATOR CIRCUIT AND DERIVE THE CONDITION FOR THE ACHIEVEMENT OF GOOD INTEGRATION.[APRIL 2016]

8

If the time constant of an RC low-pass circuit is very large, the capacitor charges very slowly and so almost all the input voltage appears across the resistor for small values of time. Then, the current in the circuit is  $v_i(t)/R$  and the output signal across C is

$$v_o(t) = \frac{1}{C} \int i(t) dt = \frac{1}{C} \int \frac{v_i(t)}{R} dt = \frac{1}{RC} \int v_i(t) dt$$

Hence the output is the integral of the input, i.e. if  $v_i(t) = \alpha t$ , then

$$v_o(t) = \frac{\alpha t^2}{2RC}$$

As time increases, the voltage drop across C does not remain negligible compared with that across R and the output will not remain the integral of the input. The output will change from a quadratic to a linear function of time.

If the time constant of an RC low-pass circuit is very large in comparison with the time required for the input signal to make an appreciable change, the circuit acts as an integrator. A criterion for good integration in terms of steady-state analysis is as follows: The lowpass circuit acts as an integrator provided the time constant of the circuit RC > 15T, where T is the period of the input sine wave. When RC > 15T, the input sinusoid will be shifted at least by 89.4° (instead of the ideal 90° shift required for integration) when it is transmitted through the network.

An RC integrator converts a square wave into a triangular wave.

Integrators are almost invariably preferred over differentiators in analog computer applications for the following reasons:

- 1. It is easier to stabilize an integrator than a differentiator because the gain of an integrator decreases with frequency whereas the gain of a differentiator increases with frequency.

- An integrator is less sensitive to noise voltages than a differentiator because of its limited bandwidth.

- 3. The amplifier of a differentiator may overload if the input waveform changes very rapidly.

- 4. It is more convenient to introduce initial conditions in an integrator.

### **UNIT – II MULTIVIBRATORS AND TIME BASE CIRCUITS**

. Bistable, monostable and astable multi-vibrators using BJT– Schmitt trigger circuit using BJT – Voltage and current sawtooth sweeps – Fixed amplitude sweep – Constant current sweep – UJT– Sawtooth Miller and boot strap time base–Multivibrators using negative resistance devices (UJT and Tunnel diodes).

### 11 MARKS

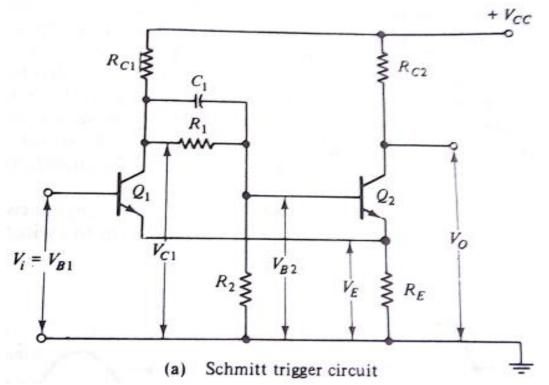

# 1. DISCUSS ABOUT WORKING OF SCHMITT TRIGGER WITH NEAT DIAGRAM. [ NOV-2016]

#### Definition:

- > It is a fast operating voltage level detector.

- > When the input voltage arrives at the upper or lower trigger levels, the output voltage rapidly changes.

- > It operates with almost any input waveform and always gives a pulse type output.

#### Circuit Description:

- > Transistor Q1 & Q2 have a common emitter resistor  $R_E$ .

- > The Q2 base voltage ( $V_{B2}$ ) is derived via potential divider (R1 & R2) from the collector of Q1.

- > Transistor Q1 & Q2 have collector resistance  $R_{C1}$  &  $R_{C2}$  respectively.

- The arrangement is such that when transistor Q1 is ON, Transistor Q2 is OFF; then transistor Q1 is OFF, Transistor Q2 is ON.

- > Speed up capacitor  $C_1$  is provided to improve the circuit switching speed.

#### **Circuit Operation :**

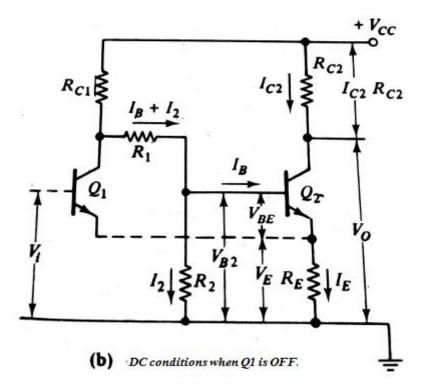

#### Consider the DC conditions when Q1 is OFF.

- When Q1 is off it can be regarded as an open circuit; therefore it can be left out of the circuit as shown below.

- > The Q2 base voltage is now derived from  $V_{CC}$  by a potential divider consisting of R1,R2 & R<sub>C1</sub>.

- > Thus Q2 is ON and a collector current IC2 flows producing a voltage drop across R<sub>C2</sub>

- > The output voltage is  $(V_{CC} I_{C2}R_{C2})$

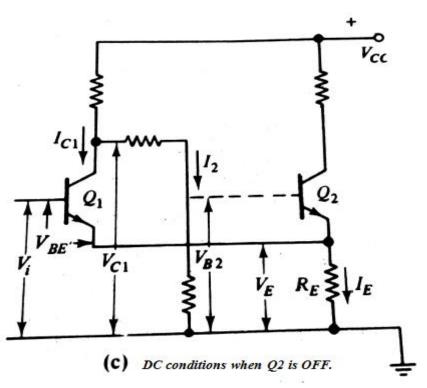

#### Consider the DC conditions when Q2 is OFF.

When Q2 is off it can be regarded as an open circuit; therefore it can be left out of the circuit as shown below.

- > Q1 is now triggered ON, the emitter voltage becomes  $V_E = V_i V_{BE}$ .

- Also the collector current I<sub>C1</sub> causes a voltage drop across R<sub>C1</sub> causing V<sub>B2</sub> to fall below the level of V<sub>E</sub>.

- > Thus when the Q1 is ON, Q2 is biased OFF and  $I_{C2}$  becomes zero.

- At this point there is no longer any significant voltage drop across R<sub>C2</sub> and the output voltage is approximately V<sub>CC</sub>.

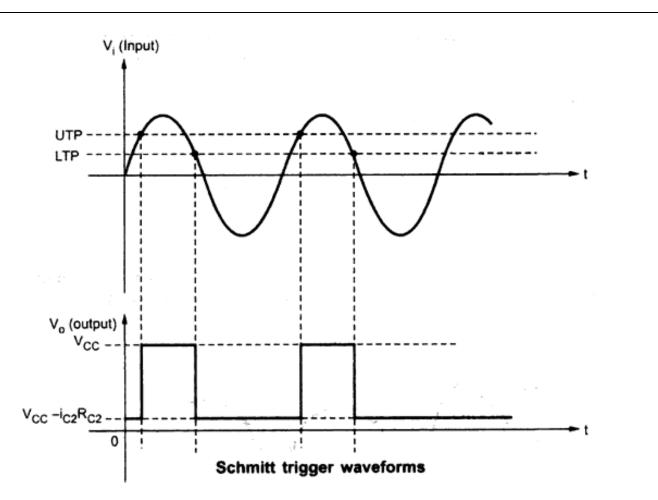

#### Upper Trigger Point (UTP)

- From fig (b) it is seen that with Q2 ON,  $V_E = V_{B2} V_{BE}$ . This is the voltage at the emitter terminal of both transistors, since they are connected together.

- > Transistor Q1 will not switch ON until its base voltage becomes greater than VE.

- > Q1 switches ON approximately at  $V_i = V_E + V_{BE}$ , which equals  $V_{B2}$ .

- > If  $V_i$  is suddenly made greater than this level Q1 would switch ON rapidly.

- > The lowest level of V<sub>i</sub> that causes Q1 to switch ON is known as the *Upper trigger point (UTP)*

#### Lower Trigger Point (LTP)

- From fig (c) with Q1 ON ,  $I_E = (V_i V_{BE})/R_E$ . Thus a reduction in Vi also reduces IE and since IC~IE, IC1 also becomes small.

- The voltage drop across RC1 is approximately IC1RC1 and the collector voltage of Q1 is VC1=(Vcc-Ic1Rc1).

- > Therefore when Vi is reduced IC1 becomes smaller causing Vc1 to rise.

- If Vi is reduced by a very small amount the resultant small increase in VB2 may leave Q2 base still below the level of its emitter voltage.

- > Q2 switches ON again only when VB2 and Vi becomes equal.

- > The input voltage at which this occurs is known as *Lower Trigger Point (LTP)*

- ➢ From the above waveforms it is seen than when the input arrives at the upper trigger point the output switches to VCC.

- $\blacktriangleright$  When he input falls to the lower trigger point the output drops to (Vcc Ic2Rc2)

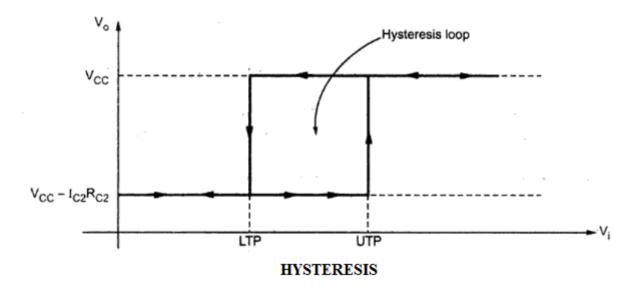

The graph of output voltage against input voltage is called transfer characteristics of the Schmitt trigger.

- It can be seen than once output changes its state, it remains there indefinitely until the input voltage crosses any of the threshold levels.

- So when output changes its state from low to high at UTP, it remains there till input crosses ltp and vice versa.

- > This characteristics of Schmitt trigger is called hysteresis.

- > It is also called dead band or dead zone as there is no change in this zone, though input changes.

- > The loop of the characteristics is called hysteresis loop.

- > The difference between UTP and LTP is called the width of hysteresis

- The amount of hysteresis can be changed by changing the values of RC1 and RC2, while the UTP can be increased by increasing the value of RE.

#### **Applications**

- 1. It is used as amplitude comparator.

- 2. It is used as squaring circuit.

- 3. It is used for wave shaping circuits.

- 4. The hysteresis in Schmitt trigger is valuable when conditioning noisy signals for using digital circuits.

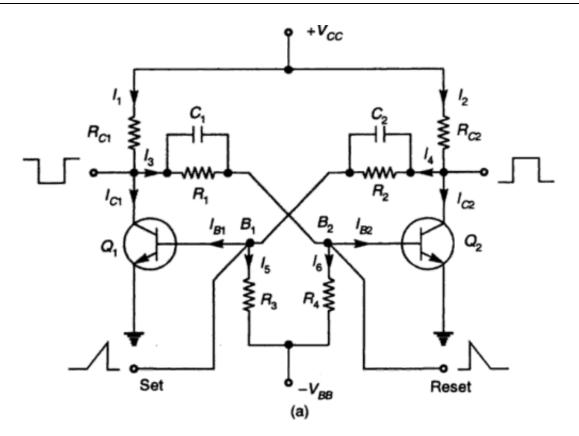

# 2. DISCUSS ABOUT WORKING OF BISTABLE MULTIVIBRATOR WITH NEAT DIAGRAM. []

#### Definition:

- > The bistable multivibrator is also referred to as a flip flop, Eccles Jordan circuit.

- It has two stable states.

- A trigger pulse is applied to the circuit will cause it to switch from one state to the other. Another trigger pulse is then required to switch the circuit back to its original state.

#### Circuit Description:

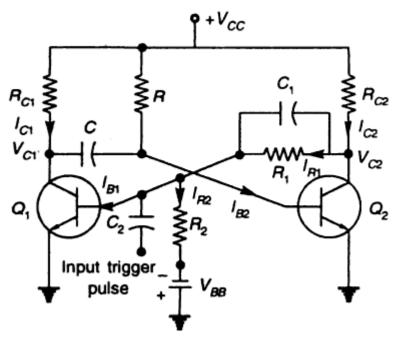

- Figure below shows the circuit of bistable multivibrator using two NPN transistors. In this circuit the output of a transistor Q2 is coupled to the base of transistor Q1 through a resistor R2.

- Similarly the output of Q1 is coupled to the base of Q2 through resistor R1.

- The main purpose of capacitors C1 and C2 is to improve the switching characteristics of the circuit by passing the high frequency components of these square wave pulses.

- > This allows fast rise and fall times so that these square waves will not be distorted.

- > C1 and C2 are thus called commutating capacitors.

#### **Circuit Operation :**

- When the circuit is first switched on one of the transistor will start conducting more than the other. This transistor is driven into saturation (i.e ON).

- > Then because of regenerative feed back action the other transistor is taken into cutoff (i.e OFF).

- Assume that Q1 is ON and Q2 is OFF.

- It is a stable state of the circuit and will remain in this state till a trigger pulse is applied from outside

- A positive triggering pulse applied to the reset input 9base of Q2 increases its forward bias, thereby turning transistor Q2 ON and an increase in collector current and a decrease in collector voltage.

- The fall in collector voltage is coupled to the base of Q1 where it reverse biases the base emitter circuit and Q1 is thus turned OFF..

- The circuit is then in its second stable state and remains so till a positive trigger pulse is applied to set input (base of Q1)

- A similar action can be achieved by applying a negative pulse at the set input for a transition from the first stable state to the second stable state and by applying a negative pulse at the reset input, reverse transition can be obtained

- Figure above shows the waveforms at the collector of transistor Q1 and Q2 of the bistable multivibrator in response to the trigger pulses applied to the set and rest input.

- $\succ$  It is evident from these waveforms that the output waveforms are the complement of each other.

#### **Applications**

- 1. It is used as memory element in shift registers, counters and so on

- 2. It is used as frequency divider.

- 3. It is used to generate square waves of symmetrical shape by sending regular triggering pulse to the input.

- 4. It is used in processing of pulse type waveforms

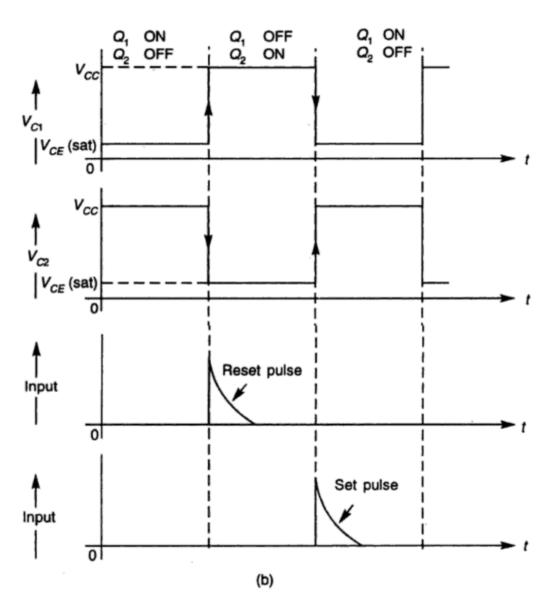

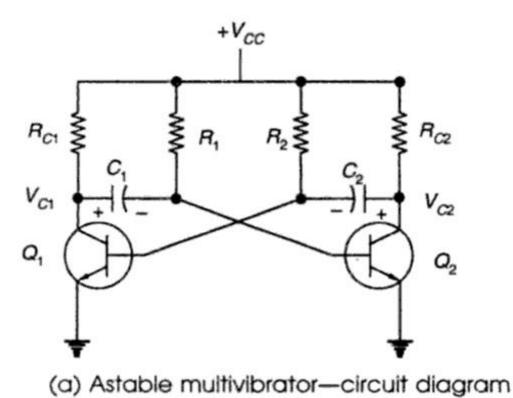

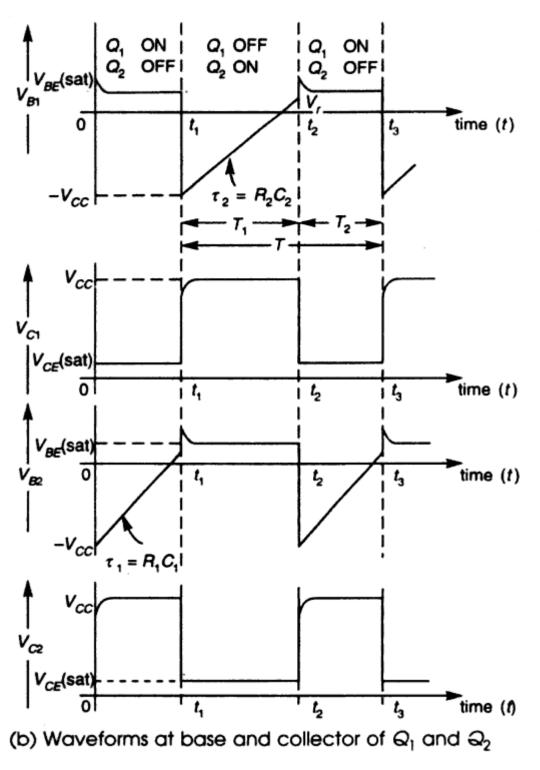

# 3. DISCUSS ABOUT WORKING OF ASTABLE MULTIVIBRATOR WITH NEAT DIAGRAM. []

#### Definition:

- It is a free running multivibrator which generates square wave without any external triggering pulse.

- > It has no stable states, i.e it has two quasi stable states.

It switches back and forth from one state to the other, remaining in each state for a time depending upon the discharging of a capacitive circuit.

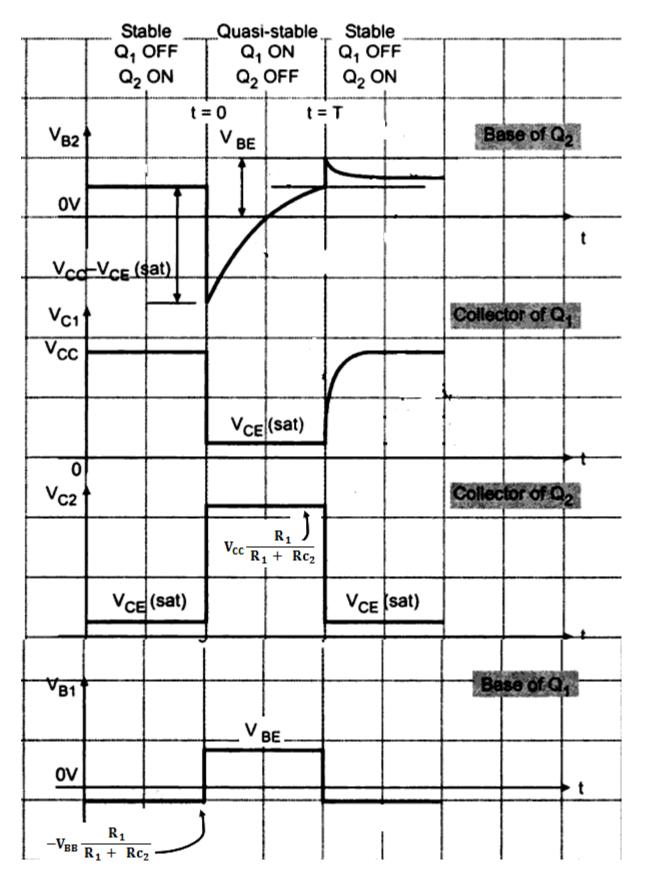

#### Circuit Description:

Figure below shows the basic symmetric transistor astable multivibrator in which the components in one half of a cycle of the circuit are identical to their counter part in the other half.

> The square wave output can be taken from collector point of Q1 or Q2.

- > The two collector resistance are equal to  $Rc.R_{C1} = R_{C2} = \frac{V_{CC} V_{CE(SAT)}}{I_{C(MAX)}}$

- The collector Q1 is coupled to the base of Q2 through capacitor C2 while the collector of Q2 is coupled to the base of Q1 through capacitor C1.

- > The capacitive coupling is used between the stages due to which neither transistor can remain permanently cut off

#### Circuit Operation :

- When the supply voltage +Vcc is applies one transistor will conduct more than the other due to circuit imbalance.

- > Initially let us assume that transistor Q1 is conducting and Q2 is cut off.

- > Then Vc1 the output of Q1 is equal to Vce(sat) i.e approximately zero volt and Vc2 =+Vcc.

- At this instant C charges exponentially with a time constant R1C1 towards the supply voltage through R1 and correspondingly VB2 also increases exponentially towards Vcc

- → When Vb2 crosses the cut in voltage Q2 starts conducting and Vc2 falls to Vce(sat).

- Also Vb1 falls due to cpacitive coupling between collector of Q2 and base of Q1 therby driving Q1 into OFF state.

- Now the rise in voltage Vc1 is coupled through C1 to the base of Q2 causing a small overshoot in voltage Vb2.Thus Q1 is OFF and Q2 is ON.

- At this instant the voltage levels are

Vb1 is negative

Vc1 = Vcc

Vb2 = Vbe(sat)

Vc2 = Vce(sat)

- When Q1 is OFF and Q2 is ON the voltage Vb1 increases exponentially with a time constant R2C2 towards Vcc.

- > Therefore Q1 is driven into saturation and Q2 is cut off.

- Now the voltage levels are

Vb2 is negative Vc2 = Vcc Vb1 = Vbe(sat) Vc1 = Vce(sat)

- It is clear that Q2 is ON, the falling voltage Vc2 permits the discharging of the capacitor C2 which drivesQ1 into cut off.

- > The rising voltage of Vc1 feeds back to the base of Q2 tending to turn it ON.

- > This process is said to be regenerative

Expression for time period T:

The capacitor  $C_2$  discharges exponentially and the voltage  $V_{B2}$  increases exponentially.

$$V_i = \text{Initial value of } V_{B2} = -V_{CC} \qquad \dots (1)$$

$$V_f$$

= Final value of  $V_{B2}$  = +  $V_{CC}$  ... (2)

For the capacitor we can write the basic equation as,

$$V_{o} = V_{f} - (V_{f} - V_{i}) e^{-t/\tau} \qquad \dots \text{ (basic equation)}$$

Here Vo means the base voltage,

*.*..

$$V_{B2} = V_{CC} - (V_{CC} - (-V_{CC})) e^{-t/R_2 C_2}$$

... (3)

$$V_{B2} = V_{CC} - 2 V_{CC} e^{-t/R_2 C_2}$$

$$V_{B2} = V_{CC} (1 - 2 e^{-t/R_2 C_2}) \dots (4)$$

We know that at switching time,

$$t = T_2 \text{ and } V_{B2} = V_{\gamma} \qquad \dots (5)$$

Substituting in equation (4),

$$V_{y} = V_{CC} (1 - 2 e^{-T_2/R_2 C_2}) \dots (6)$$

The best approximation to obtain  $T_2$  is,  $V_{\gamma} = 0$  V

*.*:.

*.*..

$0 = V_{CC} (1 - 2 e^{-T_2/R_2C_2})$ 1- 2 e^{-T\_2/R\_2C\_2} = 0

$\therefore e^{-T_2/R_2C_2} = 0.5$

$$\therefore \quad ln(e^{-T_2/R_2C_2}) = ln(0.5)$$

÷

$$\frac{-I_2}{R_2 C_2} = -0.69$$

$$T_2 = 0.69 R_2 C_2$$

*.*..

Similarly we can write the equation at  $t = T_1$  and find out the expression for  $T_1$  which same as for  $T_2$ .

$$\therefore \qquad T_1 = 0.69 R_1 C_1 \qquad \dots (8)$$

$$\therefore \qquad T = T_1 + T_2$$

$T = T_1 + T_2$  $T = 0.69 (R_1C_1 + R_2C_2) ... (9)$

...(7)

if

$$R_1 = R_2 = R \text{ and } C_1 = C_2 = C \text{ then}$$

$T = 0.69 (2 \text{ RC}) = 1.38 \text{ RC}$  ...(10)

For asymmetrical configuration

$$T=0.69(R_1C_1 + R_2C_2)$$

$$T_{on}=0.69 R_1C_1$$

$$T_{off}=0.69 R_2C_2$$

#### **Applications**

- 1. It is used as square wave generator, voltage to frequency converter and in pulse synchronization as clock for binary logic signals

- 2. It is used in construction of digital voltmeter and SMPS.

- 3. It can be used as oscillators over a wide range of audio and radio frequencies.

# 4. DISCUSS ABOUT WORKING OF MONOSTABLE MULTIVIBRATOR WITH NEAT DIAGRAM. []

#### Definition

- > Monostable multivibrator has one stable state and one quasi stable state.

- It is also known as one shot multivibrator. It remains in its stable state until an input pulse triggers it into its quasi stable state for a time duration determined by discharging an RC circuit and the circuit returns to its original stable state.

- > It remains there until the next trigger pulse is applied.

- > Thus a monostable multivibrator cannot generate square waves of its own like an astable multivibrator.

- > Only external trigger pulses will cause it to generate the rectangular waves.

#### Circuit Description :

- > It consists of two identical transistors Q1and Q2 with equal collector resistance RC1 and RC2.

- The output of Q2 is coupled to the input of base Q1 through a resistive attenuator in which C1 is a small speed ip capacitor to speed up the transition.

- ➤ The value of R2 and –Vbb are chosen so as to reverse bias Q1 and keep it in the OFF state.

- The collector supply VCC and R will forward bias Q2 and keep it in the ON state. Actually this is the stable state for the circuit.

#### **Circuit Operation :**

- When a positive trigger pulse of short duration and sufficient magnitude is applied to the base of Q1 through C2, transistor Q1 starts conducting and thereby decreasing the voltage at its collector VC1 which is coupled to the base of Q2 through capacitor C.

- > This decreases the forward bias on Q2 and its collector current decreases.

- > The increasing positive potential on the collector of Q2 is applied to the base of Q1 through R1.

- This further increases the base potential of Q1 and Q1 is quickly driven to saturation and Q2 is cutoff.

- ➤ The capacitor C is charged to approximately to +VCC through the path Vcc, R and Q1.

- As the capacitor C discharges the base of Q2 is forward biased and collector current starts to flow into Q2.

- > Thus Q2 is quickly driven to saturation and Q1 is cutoff.

- This is the stable state for the circuit and remains in this condition until another trigger pulse causes the circuit to switch over the states.

#### Derivation of pulse width:

To write equation for exponential charging of capacitor we can write,

$$t = 0^{+}, \qquad V_{i} = V_{\sigma} - I_{1} R_{C}$$

$$t = \infty, \qquad V_{f} = V_{CC}$$

$$. \qquad V_{C} = V_{f} - (V_{i} - V_{f}) e^{-t/\tau} \qquad \dots \text{ (basic equation)}$$

where

$$\tau = \text{ time constant}$$

wnere

*.*..

time constant

$$V_{B2} = V_{CC} - (V_{CC} - V_{\sigma} + I_1 R_C) e^{-t/\tau}$$

... (1)

at

$$t = T$$

,  $V_{B2} = V_{\gamma}$  ... (2)

Substituting (2) into (1) and solving for T we get,

$$T = \tau \ln \left( \frac{V_{CC} + I_1 R_C - V_{\sigma}}{V_{CC} - V_{\gamma}} \right) \qquad \dots (3)$$

Where

*:*.

$V_{\sigma} = 0.3 V$  for germanium

#### = 0.8 V for silicon

When Q1 is in saturation under quasi-stable state we can write,

$$V_{C1} = V_{CE}(sat) \qquad \dots (4)$$

$$I_1 R_C = V_{CC} - V_{CE}(sat)$$

... (5)

Substituting in (3),

$$\therefore \qquad T = \tau \ln \left( \frac{V_{CC} + V_{CC} - V_{CE}(sat) - V_{BE}(sat)}{V_{CC} - V_{\gamma}} \right) \qquad \dots (6)$$

This is because,  $V_{\sigma} = V_{BE}(sat)$

This is because,

$$V_{\sigma} = V_{BE}(sat)$$

$$\therefore \qquad T = \tau \ln \left( \frac{2 V_{CC} - V_{CE}(sat) - V_{BE}(sat)}{V_{CC} - V_{\gamma}} \right) \qquad \dots (7)$$

$$T = \tau \ln \left\{ \frac{2 \left[ V_{CC} - \left( \frac{V_{CE} (sat) + V_{BE} (sat)}{2} \right) \right]}{V_{CC} - V_{\gamma}} \right\} ....(8)$$

T = 0.69 RC

#### **Applications**

- > It is used to function as an adjustable pulse width generator.

- > It is used to generate sharp pulses from the distorted pulses.

- > It is used to generate uniform width pulses from a variable width input pulse train.

- > It is used as a time delay unit since it produces a transition at a fixed time after the trigger signal.

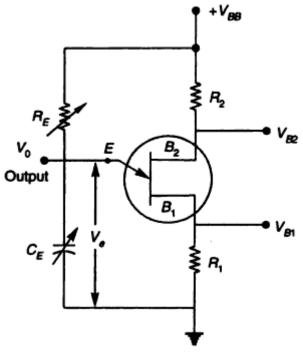

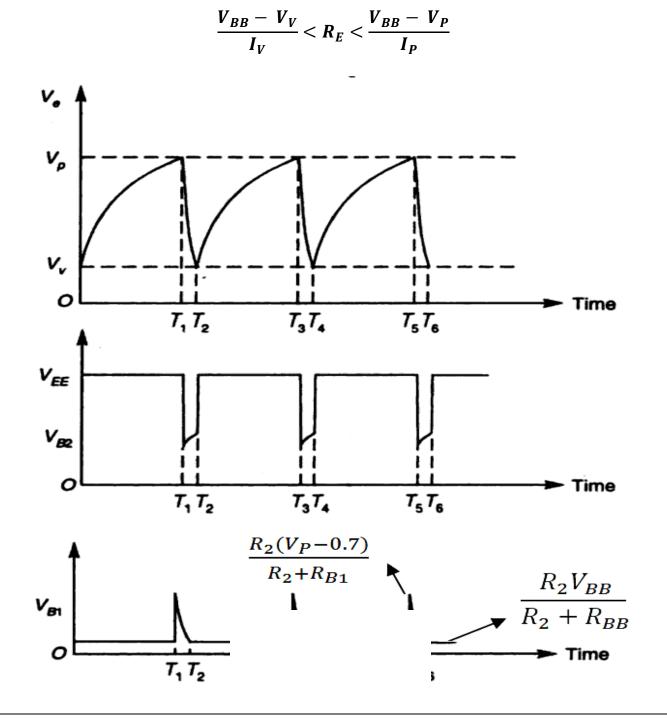

# 5. DISCUSS ABOUT WORKING OF UJT RELAXATIONA OSCILLATOR WITH NEAT DIAGRAM. []

#### Circuit Description & Operation:

- A unijunction transistor can be used in conjunction with a capacitor and a charging resistor to construct an oscillator with an approximate ramp type output.

- > Figure shows the UJT relaxation oscillator in which capacitor  $C_E$  charges through  $R_E$  as the supply voltage  $V_{BB}$  is switched ON.

- The voltage across the capacitor increases exponentially and when the capacitor voltage reaches the peak point voltage VP, the UJT starts conducting and the capacitor voltage is discharged rapidly through VB1 and R1.

- ➤ After the peak point voltage of UJT is reached, it provides negative resistance to the discharge path which is useful in the working of the relaxation oscillator.

- > As the capacitor voltage reaches zero, the devices then cuts off and capacitor  $C_E$  starts to charge again.

- $\blacktriangleright$  This cycle is repeated continuously generating a saw tooth waveform across C<sub>E</sub>.

- > The inclusion of external resistors  $R_2$  and  $R_1$  in series with  $B_2$  and  $B_1$  provides spike waveforms.

- When the UJT fires, the sudden surge of current through B1 causes drop across R1, which provides going spikes.

- Also at the time of firing, fall of V<sub>EB1</sub> causes I<sub>2</sub> to increase rapidly which generates negative going spike across R<sub>2</sub>

- In the design of UJT relaxation oscillator the charging resistor R<sub>E</sub> must be selected between certain upper and lower limits.

- Resistance  $R_E$  must not be so large that the emitter current is less than the peak point current  $I_P$  when  $V_V$  is at the firing voltage otherwise the device may not switch ON.

- > If  $R_E$  is very small then when  $V_{EB1}$  is at the emitter saturation level a current greater than the valley point current  $I_V$  might flow into emitter terminal. In this case the UJT may not switch off.

- > Thus for correct UJT operation  $R_E$  must be selected between two limits that allow the emitter current to be a minimum of  $I_P$  and a maximum of  $I_V$ .

Frequency of oscillation:

Frequency of oscillation The time period and hence the frequency of the sawtooth wave can be calculated as follows. Assuming that the capacitor is initially uncharged, the voltage  $V_c$  across the capacitor prior to breakdown is given by

$$V_c = V_{BB} \left( 1 - e^{-t/R_E C_E} \right)$$

where  $R_E C_E$  = charging time constant of resistor-capacitor circuit, and t = time from the commencement of the waveform.

The discharge of the capacitor occurs when  $V_C$  is equal to the peak-point voltage  $V_P$ , i.e.

$$V_P = \eta V_{BB} = V_{BB} (1 - e^{-t/R_E C_E})$$

$$\eta = 1 - e^{-t/R_E C_E}$$

Therefore,

$$t = R_E C_E \log_e \frac{1}{(1-\eta)}$$

$$= 2.303 R_E C_E \log_{10} \frac{1}{(1-\eta)}$$

If the discharge time of the capacitor is neglected, then t = T, the period of the wave.

Therefore, frequency of oscillation of sawtooth wave,

$e^{-t/R_E C_E} = (1 - \eta)$

$$f = \frac{1}{T} = \frac{1}{2.3 R_E C_E \log_{10} \frac{1}{(1-\eta)}}$$

**Applications**

1. It is used for triggering the device for SCR and TRIAC.

2. It is also used in timing circuits, saw tooth generator, simple oscillators and phase control.

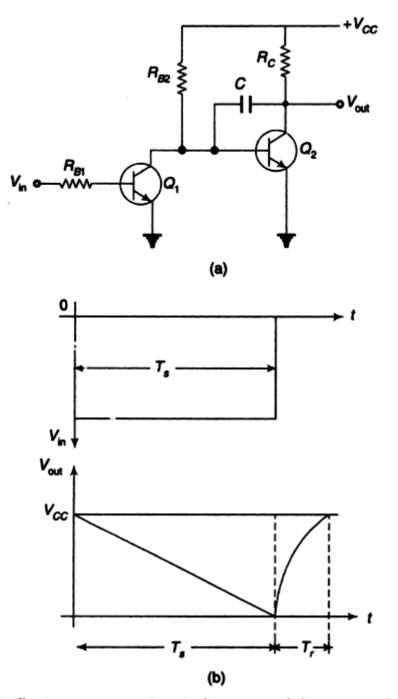

### 6. DISCUSS ABOUT WORKING OF MILLER INTEGRATOR CIRCUIT []

#### Introduction

In the miller circuit, an operational integrator is used to convert a step into ramp waveform.

**Miller integrator** Figure 17.25(a) shows the circuit of a Miller integrator or a sweep circuit. Transistor  $Q_1$  acts as a switch and transistor  $Q_2$  is a common-emitter amplifier, i.e. a high gain amplifier. Consider the case when  $Q_1$  is ON and  $Q_2$  is OFF. At this condition, the voltage across the capacitor C and the output voltage  $V_o$  is equal to  $V_{CC}$ .

Fig. 17.25 Miller integrator: (a) Circuit diagram, and (b) Input and output waveforms

When a negative pulse is applied to the base of  $Q_1$ , the emitter-base junction of  $Q_1$  is reverse biased and hence  $Q_1$  is turned OFF. Thus, the collector voltage  $(V_{C1})$  of  $Q_1$  increases which increases the bias to  $Q_2$  and as a result  $Q_2$  is turned ON. Since  $Q_2$  conducts,  $V_{out}$  begins to decrease. Because the capacitor is coupled to the base of transistor  $Q_2$ , the rate of decrease of output voltage is controlled by rate of discharge of capacitor. The time constant of the discharge is given by  $\tau_d = R_{B2}C$ .

As the value of time constant is very large, the discharge current practically remains constant. Hence, the run down of the collector voltage is linear. When the input pulse is removed,  $Q_1$  turns ON and  $Q_2$  turns OFF. The capacitor charges quickly to +  $V_{CC}$  through  $R_c$  with the time constant  $\tau_c = R_c C$ . The waveforms are shown in Fig. 17.25(b).

#### 7. DISCUSS ABOUT WORKING OF BOOTSTRAP SWEEP CIRCUIT []

**Bootstrap sweep circuit** The bootstrap circuit illustrated in Fig. 17.26(a) is a commonly used method for achieving a constant charging current. Here, transistor  $Q_1$  acts as a switch and  $Q_2$  as an emitter follower which is connected across capacitor C. Therefore, the output voltage  $V_0$  will be approximately equal to the voltage across C. The transistor, therefore, provides a low resistance output terminal for the sawtooth generator.

Initially,  $Q_1$  is ON and  $Q_2$  is OFF. Hence,  $C_1$  is charged to the supply voltage  $V_{CC}$  through diode D and the output voltage  $V_o$  is zero. When a negative pulse, as shown in Fig. 17.26(b), is applied to the base of  $Q_1$  and  $Q_1$  is turned OFF. Now, capacitor  $C_1$  discharges and starts charging capacitor C through resistor R. As a result, the base voltage of  $Q_2$  and  $V_o$  start increasing from zero volts. Therefore, diode D becomes reverse biased. The value of capacitor  $C_1$  is much larger than that of capacitor C. The voltage across R remains substantially constant throughout the charging process and thus the charging current  $(i_R)$  is maintained constant. So, capacitor C is charged with a constant current which causes the voltage across C, i.e. the output voltage  $V_o$  to increase linearly with time with the relation.

$$V_o = \frac{V_{CC}t}{RC}$$

When the negative pulse at the input is removed, C discharges through  $Q_1$  and  $V_o$  reduces to zero. Then capacitor  $C_1$  again charges to the supply voltage  $V_{CC}$  through diode D.

The bootstrap sweep circuit is called so because the circuit itself pulls up by its own bootstrap.

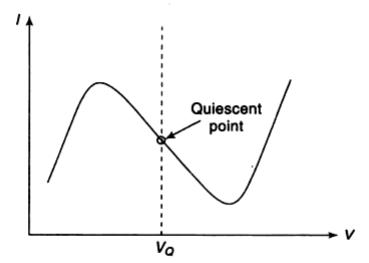

# 8. EXPLAIN IN DETAIL ABOUT NEGATIVE RESISTANCE OSCILLATORS IN DETAIL.

All oscillators do not require positive feedback for their operation. If the positive resistance of the LC tank circuit is cancelled by introducing the right amount of negative resistance across the tank circuit, then the steady oscillation can be maintained. There are several devices such as dynatron, transitron, UJT and tunnel diode that exhibit a region of negative resistance within the V-I characteristics as shown in Fig. 15.22. Such devices operated in the negative resistance region are placed across a high Q parallel LC circuit as the frequency determining section. For oscillation to occur the negative resistance should be numerically less than the dynamic resistance of the tuned circuit.

Fig. 15.22 V-/ characteristics of negative resistance oscillators

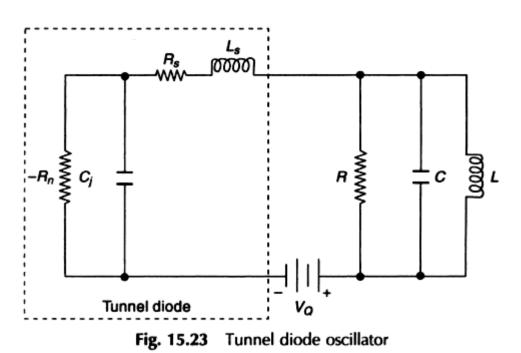

Tunnel diode oscillator Figure 15.23 shows the tunnel diode oscillator. If the parallel tank circuit with a resistance R, a capacitance C and an inductance L is connected across the tunnel diode whose negative resistance is  $-R_n$ , the net resistance  $R_{eq}$  represents R and  $-R_n$  in parallel and is given by

$$R_{eq} = \frac{-R_n \cdot R}{R - R_n}$$

If  $R > R_n$ , then  $R_{eq}$  is negative and oscillations can build-up. The oscillation amplitude then grows until it occupies a voltage range greater than the extent of the negative resistance region of the characteristics. When the operating point enters the region of positive resistance, the amplitude of oscillation is limited. To obtain the maximum output, the quiescent point must be accurately located at the center of the negative resistance region. The frequency of oscillation is given by

$$f_o = \frac{1}{2\pi\sqrt{LC}}$$

A tunnel diode has a characteristic with a negative resistance region between voltages of approximately 0.1 and 0.3 V and can be used as an oscillator at frequencies up to 100 GHz.

### 9. EXPLAIN IN DETAIL ABOUT FIXED AMPLITUDE SWEEP.

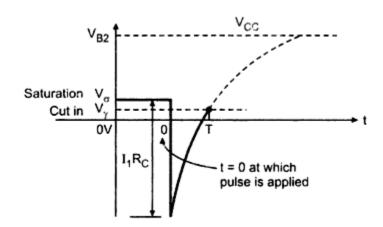

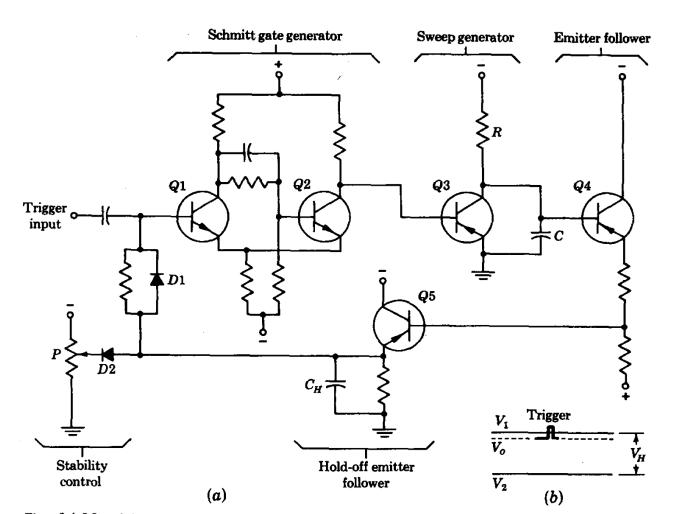

An excellent method<sup>4</sup> of obtaining a fixed-amplitude time base is to replace the monostable gate with a bistable circuit and to add a feedback loop from the output back to the input of the binary via the "hold-off circuit,"

The gate generator is an emitter-coupled binary (a Schmitt circuit) with a large hysteresis voltage  $V_H$  (Sec. 10-11). Initially transistor Q5 is cut off and diode D2 is conducting, so that the stability-control P may be used to

Fig. 14-12 (a) A technique for generating a time-base waveform of fixed amplitude. (b) The Schmitt critical levels are  $V_1$  and  $V_2$ . The base of Q1 is initially at  $V_0$ . An input trigger causes a transition, and then the voltage fed back from the sweep drives the base of Q1 toward  $V_2$ , where the reverse transition takes place.

adjust the bias of QI to be  $V_o$  just below the upper triggering which is level  $V_1$ , as indicated in Fig. 14-12b. Hence, QI is off, Q2 is on, and Q3 is in saturation, so that the voltage across the sweep capacitor C is clamped to  $V_{CE}(\text{sat})$ . The trigger input waveform consists of positive and negative sync pulses (obtained by shaping the input signal). A negative pulse is bypassed by D1 but a positive signal larger than  $V_1 - V_o$  causes a transition in the binary. The resulting positive step at Q2 reverse-biases Q3 and initiates a negative-going sweep voltage across C. The emitter follower Q4 is used for the sake of its high input impedance.

sweep to the hold-off emitter follower Q5, which, as noted, is initially cut off. After some time elapses, the negative-going sweep turns on Q5. The falling voltage at the emitter of Q5 eventually causes D2 to become reverse-biased. Thereafter, the base of Q1 is free to follow the negative-going output voltage of Q5. Because of the hysteresis of the binary circuit, this reduction in voltage at the input to Q1 will not immediately cause a reversal of state of the binary. But eventually, at a definite sweep amplitude the input to Q1 is brought to the lower triggering level  $V_2$  of Fig. 14-12b. The emittercoupled binary makes a reverse transition at this time  $T_s$ , so that Q3 is again driven into saturation and capacitor C starts to discharge.

As the capacitor C discharges, the transistor Q5 returns to cutoff. Eventually the circuit will settle itself again in its initial state, with diode D2 conducting and the base of Q1 at the level  $V_o$  just slightly below  $V_1$ . However, before this initial state may be attained the hold-off capacitor  $C_H$  must discharge through the emitter resistor of Q5 to allow the anode side of D2 to return to its initial level. The presence of  $C_H$ , therefore, delays the return to the initial state and allows time for capacitor C to discharge completely before the gate generator is able to respond to the next sync pulse. Since the time required to allow C to discharge depends on its capacitance, the hold-off capacitor  $C_H$  is switched when C is switched to change sweep speed.

It is possible to operate the time base in a free-running fashion by rendering inoperative the clamping action of the diode D2. In this case, at the termination of one sweep and without the need for a triggering signal, the base of Q1 will eventually rise to the point where a second sweep is initiated. Ordinarily, however, driven operation is employed. In this case, in the absence of a triggering signal, the sweep-stability control is adjusted just slightly below the voltage  $V_1$ , where free-running operation is restrained. Thereafter, as explained above, a triggering signal initiates the formation of the time base.

#### **10.EXPLAIN IN DETAIL ABOUT CONSTANT CURRENT SWEEP.**

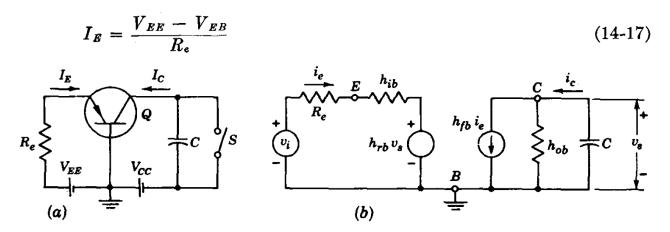

Except for very small values of collector-to-base voltage, the collector current of a transistor in the common-base configuration is very nearly constant when the emitter current is held fixed (Fig. 6-12). We may use this characteristic to generate a quite linear sweep by causing a constant current to flow into a capacitor. In the circuit of Fig. 14-13a, if  $V_{EB}$  is the emitter-to-base voltage, the emitter current is

Fig. 14-13 (a) The constant collector current of a CB transistor is used to charge a capacitor linearly; (b) the small-signal model from which to calculate the slope error  $(v_i = V_{RB} - V_{\gamma} \equiv V_i)$ .

Assuming, for the moment, that  $V_{EB}$  remains constant with time after the switch S is opened, then the collector current will be a constant whose nominal value is  $I_C = h_{FB}I_E \approx -\alpha I_E$ , and the capacitor will charge linearly with time.

To inquire into the sources of nonlinearity we shall replace the transistor by an equivalent circuit using CB hybrid parameters (Sec. 1-3). This model is valid only for changes from the quiescent values. Hence, let us define the initial condition as one where the transistor is just brought to the point of conduction by an emitter threshold bias of  $V_{\gamma}$  (Sec. 6-17) and a collector voltage  $V_{CC}$ . The equivalent circuit from which to determine the sweep voltage  $v_{s}$  is indicated in Fig. 14-13b, where the effective input signal  $v_{i}$  (the change from the quiescent value) is  $v_{i} = V_{EE} - V_{\gamma} \equiv V_{i}$ . Since only variations from the initial condition are under consideration, then the supply  $V_{CC}$ is replaced by its internal impedance (assumed to be negligible). Kirchhoff's voltage law applied to the input mesh and KCL applied to the output node of Fig. 14-13b yield, respectively,

$$v_i = i_s (R_s + h_{ib}) + h_{rb} v_s = V_i$$

(14-18)

$$i_c = i_s h_{fb} + h_{ob} v_s = -C \frac{dv_s}{dt}$$

(14-19)

Subject to the initial condition that  $v_s = 0$  at t = 0, the solution to these equations is

$$v_{\epsilon} = \frac{\alpha \tau V_{i}}{C(R_{\epsilon} + h_{ib})} \left(1 - \epsilon^{-t/\tau}\right) \tag{14-20}$$

where  $\alpha = -h_{fb}$ ,  $V_i = V_{EE} - V_{\gamma}$ , and

$$\frac{1}{\tau} = \frac{1}{C} \left( h_{ob} + \frac{\alpha h_{rb}}{R_s + h_{ib}} \right) \tag{14-21}$$

Expanding the exponential into a power series in  $t/\tau$  and retaining only the first term,

$$v_s = \frac{\alpha V_i t}{C(R_s + h_{ib})} \tag{14-22}$$

This result is consistent with Fig. 14-13b, which gives an emitter current of  $i_{\bullet} = V_i/(R_{\bullet} + h_{ib})$  at t = 0+ and a short-circuit collector current  $\alpha$  times as large. If the capacitor current were to remain constant at this value, then  $v_{\bullet} = \alpha i_{\bullet} t/C$ , in agreement with Eq. (14-22).

The sweep amplitude  $V_s$  is obtained from Eq. (14-22) with  $t = T_s$ . The slope error, given by Eq. (14-9), is

$$e_s = \frac{T_s}{\tau} = \frac{V_s}{V_i} \left[ h_{rb} + \frac{h_{ab}}{\alpha} \left( R_s + h_{ib} \right) \right]$$

(14-23)

where use was made of Eqs. (14-21) and (14-22). The generator  $h_{rb}v_s$ , representing the reaction of the collector voltage on the input circuit, causes the emitter current to change as the sweep forms. The first term in Eq. (14-23) results from this change in emitter current. The fact that the collector current is not precisely constant (even for constant emitter current) because of the shunting effect of  $h_{ob}$  gives rise to a slope error whose value is given by the second term in Eq. (14-23).

#### Approved by AICTE, New Delhi & Affiliated to Pondicherry University, Puducherry Approved by AICTE, New Delhi & Affiliated to Pondicherry University, Puducherry B-A. Pondy - Villupuram Main Road, Ariyur, Puducherry - 605 102. ASPIRE TO EXCEL

# **UNIT – III COMBINATIONAL CIRCUITS**

Binary arithmetic –BCD addition and subtraction–Code converters-Parity generator–Binary to BCD and BCD to binary conversions–Design of combination circuits using NAND and NOR gates–Design of encoders, decoders, multiplexers, demultiplexer – Serial adders–Binary multiplier – Simplification of k-map, Flip-Flops: RS, D, JKand T types.

# 11 MARKS

# 1. DISCUSS ABOUT VARIOUS NUMBER SYSTEMS WITH EXAMPLES AND PERFORM CONVERSTIONS. []

### Definition:

- > Number system is a basic for counting various items. It is of following types

- ✓ Decimal number system

- ✓ Binary number system

- ✓ Octal system

- ✓ Hexa decimal system

#### Decimal number system

- > The decimal number system has ten digits, 0 to 9.

- Since there are ten distinct digits used in decimal system therefore the decimal number system has a base (or radix) of 10.

- > The weights for whole numbers are positive power of ten that increases from right to left beginning with  $10^0 = 1$

- $\dots 10^4, 10^3, 10^2, 10^1, 10^0$

- > For fractional numbers the weights are negative power of 10 that decrease from left to right beginning with  $10^{-1}$

$$\dots \dots \dots \dots 10^4, 10^3, 10^2, 10^1, 10^0, 10^{-1}, 10^{-2}, 10^{-3}, \dots$$

Decimal point

Represent number 98 in power of 10.

$N = 9 \times 10^{1} + 8 \times 10^{0}$

Represent number 98.72 in power of 10.

$N = 9 \times 10^{1} + 8 \times 10^{0} + 7 \times 10^{-1} + 2 \times 10^{-2}$

Binary number system

- > The binary number system is less complicated than decimal. The two binary digits are 0 and 1.

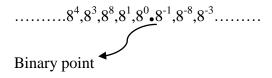

- ➢ Here the base is 2. The weightage is given as

$.....2^{4}, 2^{3}, 2^{2}, 2^{1}, 2^{0}, 2^{-1}, 2^{-2}, 2^{-3}....$ Binary point

Right most bit is called Least significant bit [LSB] and left most bit is called most significant bit [MSB]

Represent binary number 1101.101 in power of 2 and find its decimal equivalent. Representing given binary number in power of 2 we have,  $N = 1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 1 \times 2^{0} + 1 \times 2^{-1}$   $+ 0 \times 2^{-2} + 1 \times 2^{-3}$  = 8 + 4 + 0 + 1 + 0.5 + 0 + 0.125 $= 13.625_{10}$

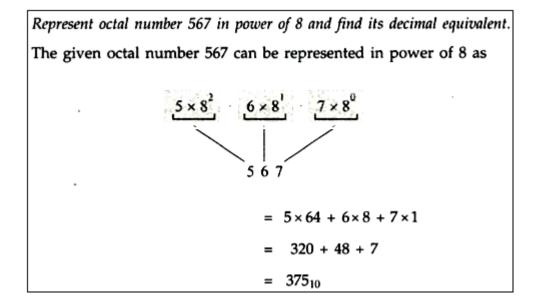

#### Octal number system

- > The octal number system is composed of eight digits which are 0,1,2,3,4,5,6,7

- ▶ It has base of 8. The weightage is given as

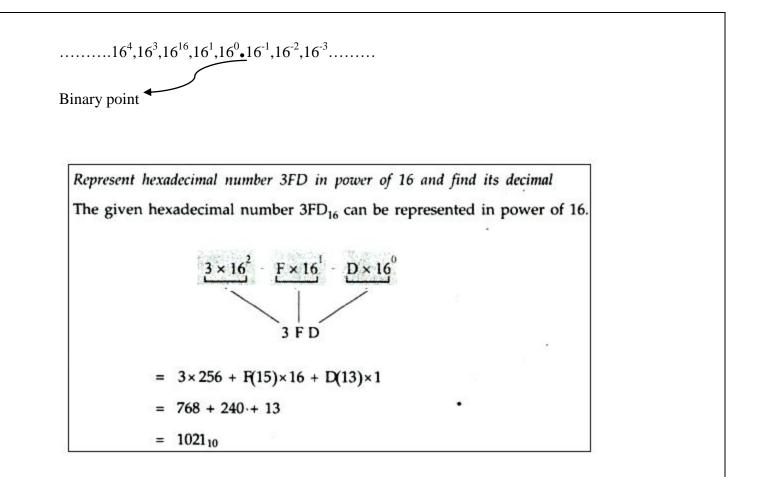

#### Hexa decimal number system

- > The octal number system is composed of 16 digits which are 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

- > It has base of 8. The weightage is given as

| Numbering S | òys |  |

|-------------|-----|--|

| System      |     |  |

| Binary      |     |  |

| Octal       |     |  |

| Decimal     |     |  |

| Hexadecima  | I   |  |

|             |     |  |

|             |     |  |

|             |     |  |

|             |     |  |

| DECIMAL | BINARY | OCTAL | HEXA | Hexadecimal |

|---------|--------|-------|------|-------------|

| 0       | 0000   | 0     | 0    |             |

| 1       | 0001   | 1     | 1    |             |

| 2       | 0010   | 2     | 2    |             |

| 3       | 0011   | 3     | 3    |             |

| 4       | 0100   | 4     | 4    |             |

| 5       | 0101   | 5     | 5    |             |

| 6       | 0110   | 6     | 6    |             |

| 7       | 0111   | 7     | 7    |             |

| 8       | 1000   | 10    | 8    |             |

| 9       | 1001   | 11    | 9    |             |

| 10      | 1010   | 12    | А    |             |

| 11      | 1011   | 13    | В    |             |

| 12      | 1100   | 14    | С    |             |

| 13      | 1101   | 15    | D    |             |

| 14      | 1110   | 16    | Е    |             |

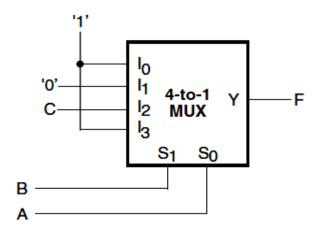

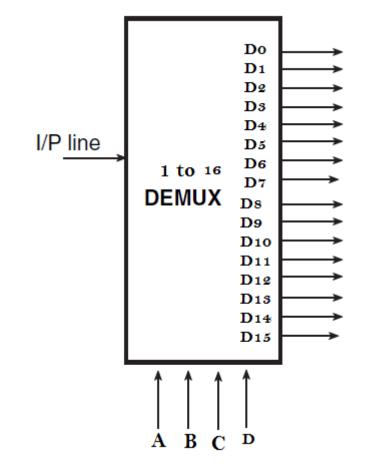

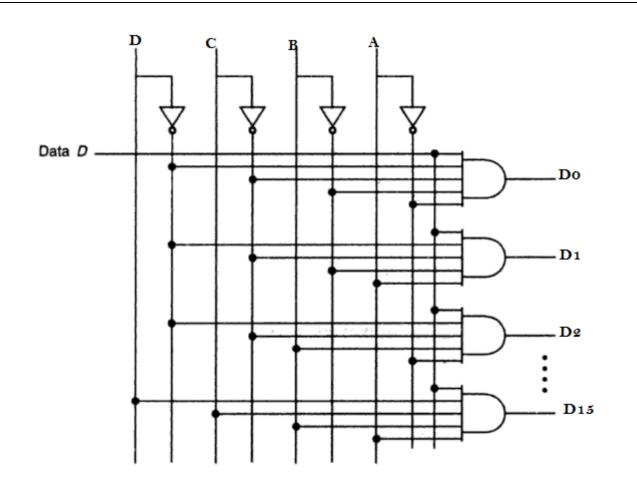

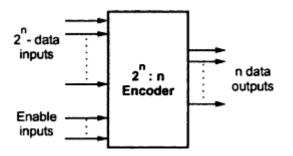

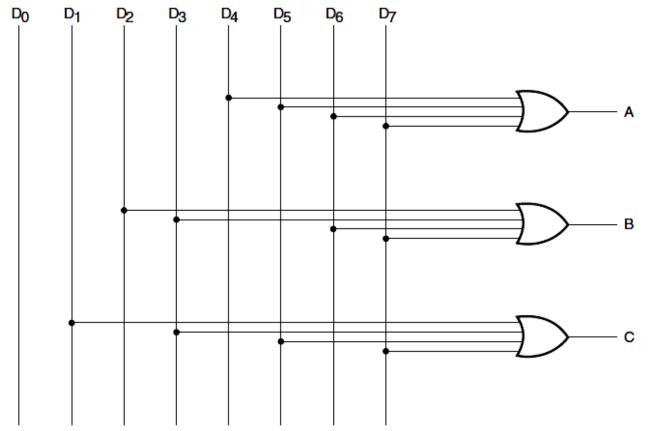

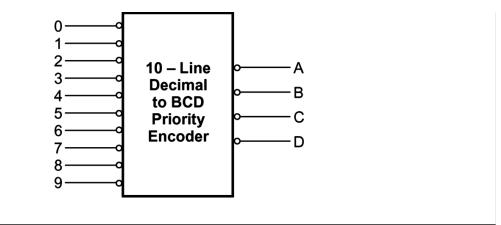

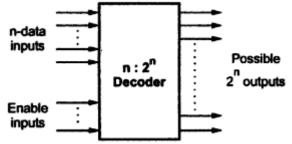

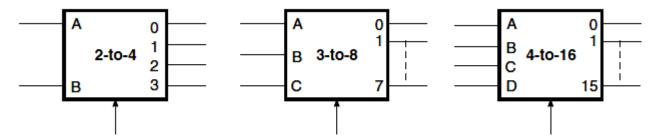

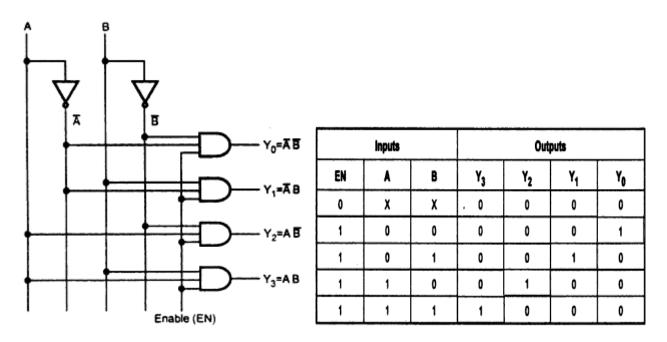

| 15      | 1111   | 17    | F    | 3           |