#### VLSI Design – Notes

#### Unit-1

**CMOS Technology:** Introduction to MOS transistors and VLSI fabrication(NMOS, PMOS, CMOS and BiCMOS)- Introduction to power reduction techniques-Dynamic Power Reduction-Static Power Reduction- NMOS and CMOS inverter-Determination of pull up to pull down ratios – propagation delays – power dissipation - Stick Diagram -MOS layers - design rules and layout- choice of layers and Scaling.

#### **Basic Introduction:**

**CMOS** or Complementary Metal Oxide Semiconductor is a combination of NMOS and PMOS transistors. NMOS is an N-type Metal Oxide Semiconductor, and PMOS is a P-type Metal Oxide Semiconductor. N-type is a type of pentavalent impurities, and P-type is a type of trivalent impurities doped on the semiconductor. The three terminals of the transistors are Gate (G), Source (S), and Drain (D). The doping of p-type/n-type is applied on the D and S terminals.

| Basis of<br>Difference | CMOS Technology                                                                                                       | NMOS Technology                                                                                                    |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Full form              | CMOS stands for Complementary Metal Oxide Semiconductor.                                                              | NMOS stands for N-channel Metal Oxide Semiconductor.                                                               |

| Definition             | A metal oxide semiconductor technology that combines both PMOS and NMOS technologies is called CMOS.                  | A metal oxide semiconductor technology that uses N-type channel between source and drain terminals is called NMOS. |

| Operation              | The CMOS performs its operation by employing symmetrical as well as complementary pairs of P-type and N-type MOSFETs. |                                                                                                                    |

| Logic level            | The logic level of CMOS is 0 V / 5 V.                                                                                 | The logic level of NMOS depends on the $\boldsymbol{\beta}$ ratio as well as noise margins.                        |

| Layout                 | CMOS has more regular layout.                                                                                         | NMOS has irregular layout.                                                                                         |

| Power<br>dissipation   | In case of CMOS, the power dissipation is zero, when it is in standby mode.                                           | The power dissipates in NMOS, when its output is zero (0).                                                         |

| Power supply           | For CMOS, the power supply may vary from 1.5 V to 15 V.                                                               | For NMOS, the power supply is fixed depending on $V_{\text{DD}}.$                                                  |

| Packing density        | CMOS has less packing density. Where, it requires 2N devices for N inputs.                                            | The packing density of NMOS is high. It requires (N+1) devices for N inputs.                                       |

| Load to drive<br>ratio | CMOS has load / drive ratio 1:1 or 2:1.                                                                               | NMOS has load / drive ratio 4:1.                                                                                   |

| Transmission           | The transmission gate of CMOS allows to                                                                               | The transmission gate of NMOS allows to                                                                            |

| gate                     | pass both '0' and '1' logic well.                                                                                     | pass only the logic '0' well. If it pass logic '1', then it will have VT drop. |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Static power consumption | CMOS consumes low static power.                                                                                       | NMOS consumes relatively more static power.                                    |

| Noise immunity           | CMOS has high noise immunity.                                                                                         | NMOS has comparatively low noise immunity.                                     |

| Applications             | The CMOS is used to design various types of digital logic circuits, microprocessors, microcontrollers, memories, etc. | C                                                                              |

#### 1. NMOS Fabrication

The doping on the NMOS will be a Pentavalent (five valence electrons) impurity, such as **boron** and **antimony**. It has a p-substrate on which the n-type channel is created. As the name implies, the majority carriers participating in the current are electrons. The movement of electrons is fast as compared to the holes. Thus, NMOS is faster than the PMOS.

The NMOS fabrication includes eight steps, which are listed as follows:

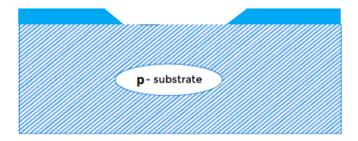

#### Step 1: Processing the substrate

The first step is to create a **p-type substrate**. The p-type has trivalent impurities (three valence electrons), such as boron with a concentration upto 1016/cm<sup>3</sup>. A pure thin film of the silicon wafer is selected on which the p-type impurities are applied as crystals. The diameter of the wafer can be upto 0.15m or 150mm. The chosen wafer material is silicon because it is a clean and high-quality semiconductor material preferred for fabrication.

#### Step 2: Silicon dioxide layer

Silicon dioxide is made up of two materials silicon (Si) and oxygen ( $O_2$ ). It is also known as **oxide**. Silicon has a stable structure and is considered as the most abundant metal available on the Earth. It is combined with oxygen that acts as an insulator or conductor under various conditions.

SiO2 layer is grown over the surface of the p-type substrate to prevent it from external factors. It also acts as a barrier to the dopants applied on the layer during the processing. The silicon dioxide thickness is very small, around 0.000001m or 1um.

Step 3: Photoresist material is applied on the SiO<sub>2</sub> layer

The silicon dioxide layer is covered with the photoresist material. It is a **light-sensitive** material that forms the coating over the surface of the SiO<sub>2</sub> layer. It is useful in reducing the size of the transistors.

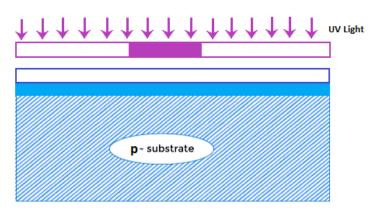

After the photoresist is applied on the silicon dioxide layer, a mask with the desired pattern is used as a medium to expose UV (Ultra-Violet) lights. The UV light through the mask reaches the photoresist material. The exposed resist remains on the surface and the unexposed part is removed from the surface.

Step 4: Etching the regions

The unexposed window is removed from the surface and the regions are etched together to form a clean wafer surface. It is shown below:

#### Step 5: Formation of Gate

The remaining photoresist layer is removed from the wafer. A thin silicon dioxide layer of 0.0000001m or 0.1 um is grown over the surface. The polysilicon is further added to the surface that forms a gate structure, which is deposited by CVD process. The Chemical Vapor Deposition produces solid materials of high quality. The polysilicon is preferred for the gate because of its high melting point. Its properties are also similar to that of  $SiO_2$ .

Note: The number of doping concentrations, the thickness of the layer, and the resistivity are the three essential elements to be considered for the fabrication process.

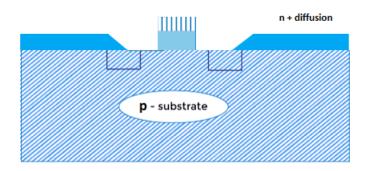

Step 6: Creating the area for drain and source terminals

The thin oxide layer on the surface of the silicon wafer is removed and the n-type impurities are inserted with the help of the diffusion process in the specified exposed area. It forms the n-channel at the source and drain terminals. The wafer is first heated at a very high temperature and the gas in passed into it. The area exposed is filled with the gas containing n-type impurities, such as phosphorous.

**Step 7:** SiO<sub>2</sub> and photoresist is again deposited on the source and drain terminals

The same process is again carried to protect the S and D terminals. The oxide layer was removed from the surface of the wafer to create the two terminals, as discussed in step 6. The silicon dioxide and the photoresist are deposited, etched, and masked to protect it. The contact holes are left exposed for the connections.

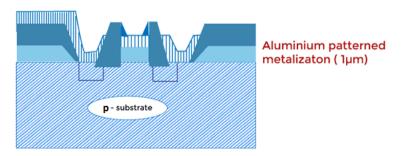

Step 8: Making of the metal layer

It is almost the last step of the NMOS fabrication process. The metal layer of aluminum is deposited on the surface of wafer including the contact holes. The thickness of the aluminum is around 1um. The metal layer is further masked and etched to form the required interconnection pattern.

#### nMOS fabrication process

The layer of different materials was applied to the silicon wafer at each step. Thus, the NMOS fabrication process involves the deposition of four major layers. It includes silicon dioxide, photoresist, polysilicon, and the aluminum metal layer.

\*\*\*\*\*\*\*\*\*\*

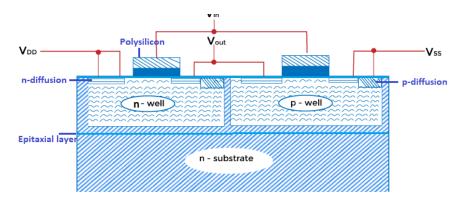

## 2. N-well Fabrication Or CMOS Fabrication process.

It is a CMOS fabrication process. It means that the PMOS and NMOS are fabricated in different ways. PMOS is created by placing it in the n-well that has a p-type channel. The NMOS is created similarly as discussed above, i.e., on the substrate. Hence, the fabrication of CMOS is known as N-TUB.

The steps involved in the N-TUB fabrication process are as follows:

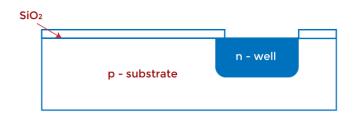

## 1. Wafer

The silicon wafer is selected for doping p-type impurities on it. The doped wafer formed will be the p-type substrate with the trivalent impurities.

#### 2. Oxidation of wafer

The Silicon dioxide layer or oxide layer is created on the surface that protects the substrate. Silicon is one of the metals that are easily available with properties suitable for the fabrication process.

| Silicon dioxide |  |

|-----------------|--|

|                 |  |

|                 |  |

|                 |  |

|                 |  |

|                 |  |

| p - substrate   |  |

#### 3. Photoresist deposition

The photoresist material is deposited on the wafer. It allows the formation of the n-well on the p-type substrate.

#### 4. N-well Mask

The n-well mask is exposed on the wafer with a particular pattern. The soft part or the unexposed part of the photo resist material is removed to expose the  $SiO_2$  layer.

#### 5. Oxide Etch

As discussed, the right part of the wafer is not covered by the photoresist. It is due to the area left for the formation of the n-well. To protect it, the oxide layer is etched with the **Hydrofluoric acid**. The silicon atoms of the SiO<sub>2</sub> layer and the fluoride atoms of HF acid form the strong bond. The silicon wafer is now ready to be exposed to the n-well area.

The leftover photoresist material is removed with the help of the etching process.

#### 6. N-well formation

The diffusion process is used to make the n-well on the right side of the wafer. Diffusion is a method of adding impurities from a high concentration region towards a low concentration region. We can also use the ion implantation process to create an n-well.

#### 7. Oxide removal

The remaining oxide on the surface of the wafer is stripped off with the help of HF acid. The oxide protects and needs to be removed to create a gate junction. It is done to expose the n-well formed in the above step directly.

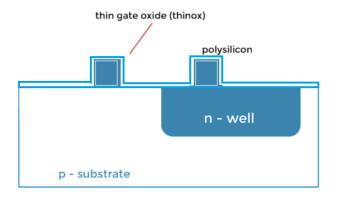

#### 8. Gate formation

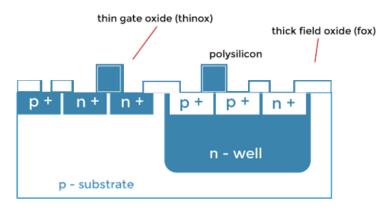

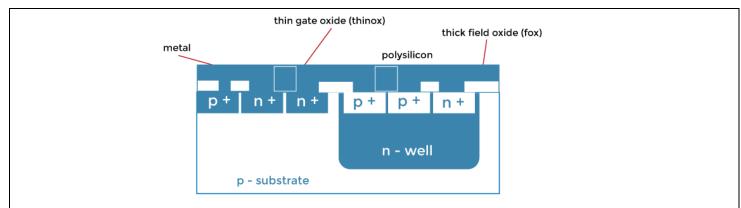

The polysilicon is added to the surface that forms a gate structure deposited by CVD process. It is a heavily doped layer of polysilicon present over the thinox, which is a type of thin gate oxide.

#### 9. Poly patterning

The wafer surface is exposed with the photoresist and the mask to create the two G terminals. It is because CMOS is a combination of NMOS and PMOS, and both have separate gates, as shown below:

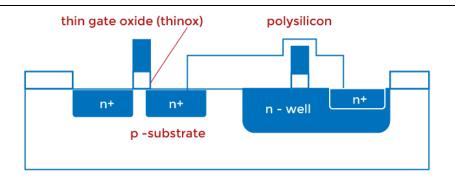

#### 10. Diffusion pattern

A protective layer of oxide and photoresist is again applied on the wafer to protect the two gate terminals.

#### 11. Creating area for source and drain

To create the area for S and D, the protective oxide is removed present on the surface of the wafer. It creates the two vacant areas.

#### 12. N-diffusion regions

The two vacant areas include two source terminals and two drain terminals on each side. The n+ diffusion regions are created by injecting the n+ impurities to those vacant areas. It automatically forms the S and D terminals adjacent to the gate. The n-well on the right side is also created through n+ diffusion.

The wafer is heated at a high temperature to create the n-well regions through the diffusion process.

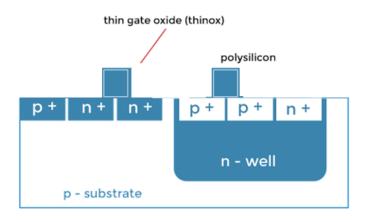

#### 13. P-diffusion

The NMOS has n+ S and D regions, while the PMOS has p+ regions. The n+ regions are already created with the help of above step. Next, the p+ diffusion mask is used that completes the formation of all the active regions of the MOS transistors.

#### 14. Field oxide

To insulate the wafer, the field oxide  $(SiO_2)$  is deposited on its surface.

#### 15. Metal formation

The metal layer of aluminum is deposited on the surface of wafer including the contact holes. It also fills the cut holes. It is patterned with the help of metal mask.

The entire process of the N-TUB fabrication can be summarized with the help of flow diagram shown below:

The above process shows the formation of NMOS (left side) and the PMOS transistors. We can also create an inverted circuit fabricated using the same steps. It consists of the PMOS and the NMOS (right side) transistors. The NMOS transistors perform better as compared to PMOS. Thus, n-wells are created to overcome the poor performance of the PMOS.

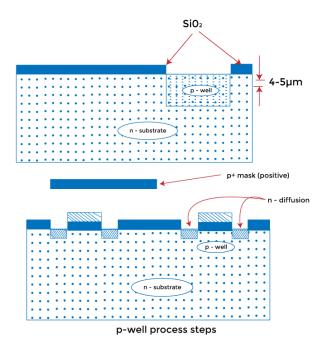

#### 3. P-TUB Fabrication Or P-well Fabrication

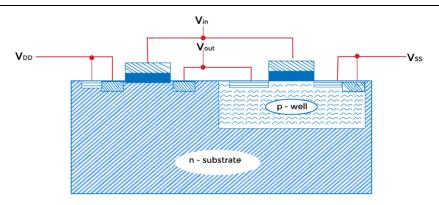

It is also a CMOS fabrication process. The NMOS transistors are created by placing them in the **p-well** with a ptype channel. The PMOS is created on the n-type substrate. Hence, the fabrication of NMOS is known as P-TUB.

Here, the substrate is n-type, and the doping on the source and drain regions is p-type. A p-well is diffused into the substrate through the diffusion process. The doping concentration and depth of the p-well affect the n-type devices' voltage. Thus, special care is required. The deeper the wells, the larger the surface area it may require.

P-TUB combines the PMOS and the NMOS (right side). The n-type acts as a substrate for the PMOS, and the pwell acts as the substrate for the NMOS. These two areas are electrically isolated. The p-well CMOS inverter is shown below:

The masking, diffusion, etc. are similar to that of N-TUB. The various mask used in the steps for fabrication are used to defines the areas for deep wells, thick stripped oxide deposition, contacts areas, interconnections, deposition of polysilicon layer, p-diffusions, and metal layer patterns.

#### 4. Twin-TUB Fabrication

Twin-TUB is a combination of p-well and n-well processes formed on the same substrate. It is also known as **dual well process**. The high resistivity n-type substrate with both n-well and p-well regions is created, as shown below:

It is an inverting arrangement of twin-tub. The separate transistors and their arrangement help to optimize the n-type devices, p-type devices, and other parameters, such as body effect and threshold voltage. The wafer has two layers. The top layer is the epitaxial layer and the main substrate layer is of n-type.

The steps of the twin-TUB fabrication are as follows:

Step 1: Deposition of thin oxide layer of silicon dioxide (SiO<sub>2</sub>).

**Step 2:** The deposition of **silicon nitride** layer using the CVD process. It has various advantages, such as high temperature stability and light weight.

**Step 3:** The third step includes creating trenches and filling them with SiO2, which is an insulating material. The trenches are created to prevent the current leakage.

**Step 4:** The oxide and nitride is removes to deposit the n-well and p-well regions with the help of diffusion.

**Step 5:** The p-well and the n-well mask are used to dispose of the specific areas on both sides. The implant and annealing are required to adjust the doping concentration of the two wells. The annealing process reduces the hardness for efficient doping.

**Step 6:** A thin layer of  $SiO_2$  and polysilicon is applied on the surface of the silicon wafer.

**Step 7:** The source, gate, and drain regions are created using the diffusion process.

Step 8: The oxide and nitride layer is again deposited.

**Step 9:** The metal layer of aluminum is deposited on the surface of wafer including the contact holes. It also fills the cut holes.

Step 10: A protective glass layer is deposited on the transistor in the last step.

#### 5. CMOS fabrication by SOI technology:-

The SOI (Silicon-on-Insulator) process involves several steps to create a thin layer of silicon on top of an insulating substrate, typically silicon dioxide. The following are the typical steps involved in the SOI process:

- 1. Substrate Preparation: The first step in the SOI process is to prepare the substrate, which involves cleaning and polishing the surface to ensure that it is free of contaminants and defects.

- 2. Buried Oxide Formation: The next step is to create a layer of silicon dioxide on the surface of the substrate. This is typically done using a process called thermal oxidation, which involves heating the substrate in the presence of oxygen.

- 3. Silicon Layer Deposition: Once the silicon dioxide layer has been formed, a layer of silicon is deposited on top of it. This is typically done using a process called chemical vapor deposition (CVD), which involves heating a gas that contains silicon to deposit a layer of silicon on the substrate.

- 4. Silicon Layer Thinning: The next step is to thin the silicon layer to the desired thickness. This is typically done using a process called ion implantation, which involves bombarding the silicon with ions to create a thin, uniform layer.

- 5. Annealing: Once the silicon layer has been thinned, the substrate is heated in a process called annealing. This step helps to repair any defects in the silicon layer and improves the overall quality of the SOI substrate.

- 6. Device Fabrication: The final step in the SOI process is to fabricate devices on the SOI substrate. This typically involves using lithography and etching techniques to create patterns in the silicon layer, which can then be used to create transistors, diodes, and other electronic components.

Overall, the SOI process involves several steps to create a thin layer of silicon on top of an insulating substrate. While the process is more complex and expensive than traditional bulk silicon processing, it offers several advantages in terms of improved device performance and radiation hardness.

## Advantages:

- 1. Reduced Parasitic Capacitance: In traditional bulk silicon processing, parasitic capacitance can reduce device performance. SOI reduces parasitic capacitance because the insulating layer isolates the silicon from the substrate, reducing interference and allowing for faster operation.

- 2. Improved Transistor Performance: SOI technology improves transistor performance because it reduces the effects of device-to-device interactions. The thin insulating layer and the substrate reduce the number of charged particles near the transistor channel, allowing for faster switching and lower leakage currents.

- 3. Radiation Hardness: SOI is also more radiation-hard than traditional bulk silicon because of its reduced parasitic capacitance and improved transistor performance. This makes SOI technology an attractive option for applications such as military and aerospace.

- 4. Reduced Power Consumption: The reduced parasitic capacitance and improved transistor performance in SOI technology can lead to reduced power consumption in devices.

#### Disadvantages:

- 1. High Cost: The SOI process is more expensive than traditional bulk silicon processing because it involves additional manufacturing steps and requires specialized equipment.

- 2. Thermal Issues: The thin insulating layer in SOI can cause thermal issues, such as localized heating, which can reduce device reliability and performance.

- 3. Substrate Stress: The insulating layer in SOI can create stress in the substrate, which can cause defects in the silicon layer and reduce device performance.

- 4. Design Complexity: SOI technology requires specialized design considerations, such as the need for floating-body effects and parasitic bipolar transistors.

11

#### 6. Dynamic and Static Power

| Dynamic Power Reduction                                                                                                                                           | Static Power Reduction                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Reduces power consumption when the circuit is switching or changing state                                                                                         | Reduces power consumption when the circuit is in a steady state                                                                 |

| Achieved through techniques such as clock gating,<br>power gating, and dynamic voltage and frequency<br>scaling (DVFS)                                            | Achieved through techniques such as reducing supply voltage, threshold voltage scaling, and transistor sizing                   |

| Dynamic power reduction techniques typically result in larger power savings                                                                                       | Static power reduction techniques typically result in smaller power savings compared to dynamic techniques                      |

| Suitable for applications where the circuit operates with high activity factors                                                                                   | Suitable for applications where the circuit operates with low activity factors                                                  |

| May result in a decrease in circuit performance due to<br>the need for extra circuitry for control and<br>management of the dynamic power reduction<br>techniques | May not affect circuit performance or may result in a small increase in circuit performance                                     |

| Examples of dynamic power reduction techniques include clock gating, power gating, and dynamic voltage and frequency scaling (DVFS)                               | Examples of static power reduction techniques include reducing supply voltage, threshold voltage scaling, and transistor sizing |

Overall, dynamic power reduction techniques focus on reducing power consumption during the switching or changing of circuit states, while static power reduction techniques focus on reducing power consumption during steady-state operation. Both types of power reduction techniques have their own advantages and disadvantages, and the choice of which technique to use depends on the specific requirements of the application.

The formulas for dynamic power and static power are as follows:

#### Dynamic Power = 0.5 x Capacitance x Voltage^2 x Frequency

Static Power = Leakage Current x Supply Voltage

where:

- Capacitance is the effective capacitance of the circuit (including wires, transistors, and other components)

- Voltage is the operating voltage of the circuit

- Frequency is the operating frequency of the circuit

- Leakage Current is the current that flows through a transistor when it is supposed to be turned off

- Supply Voltage is the voltage supplied to the circuit.

Dynamic power reduction techniques focus on reducing the capacitance, voltage, and frequency of the circuit, while static power reduction techniques focus on reducing the leakage current and supply voltage of the circuit. By reducing these parameters, the power consumption of the circuit can be reduced, resulting in energy savings and increased battery life in portable devices.

\*\*\*\*\*\*\*

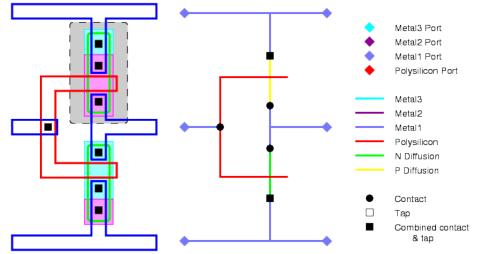

## 7. Stick diagram and layout

## • Mask Layout and Stick Diagram for a CMOS Inverter

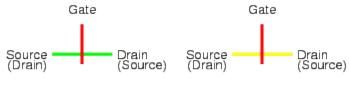

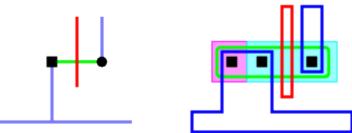

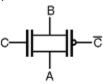

#### Transistors

A transistor exists where a polysilicon stick crosses either an N diffusion stick (NMOS transistor) or a P diffusion stick (PMOS transistor).

NMOS

PMOS

Note that there is no difference in the construction of a transistor source and a transistor drain. The source is determined as the source of conductors (electrons for NMOS / holes for PMOS) when current flows through the channel. In some pass transistor circuits, the source and drain may swap over during use.

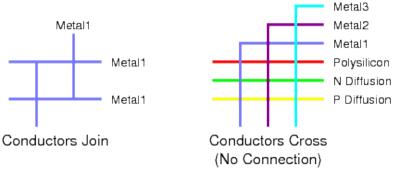

#### Implied Connections and Crossovers

Where two sticks of the same colour meet or cross there is always a connection. Where two sticks of different colours meet or cross there is no implied connection.

Note that N and P diffusions may not cross each other. Where poly crosses diffusion we have a transistor (see above).

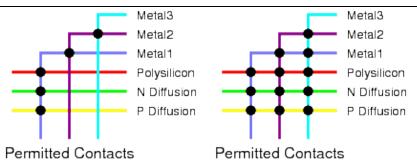

#### Contacts

A connection may be explicitly defined using a filled black circle. In the general case a connection is permitted where the mask layers will be separated by just one layer of insulator (through which a "contact cut" may be defined). Thus P diffusion may connect to Metal1 but not directly to Metal2.

(Assuming no stacked contacts) (Assuming stacked contacts)

In a process where stacked contacts are permitted, we may draw a contact between non-adjacent conductors; e.g. between Poly and Metal3, in which case the connection to intermediate layers (Metal1 and Metal2) is implied.

#### • Taps

The tap represents a connection to something we can't see; either the N-Well (not shown on our stick diagram) or the wafer substrate. A tap is defined using an unfilled black square. Here there will be only one conductor crossing the square (Metal1 power or ground rail).

An N-Well Tap is inferred where the connection is from a power rail while a Substrate Tap is inferred where the connection is from a ground rail.

#### • Combined Contacts & Taps

We can often save space by using a combined contact and tap. Here the tap shares the same Active Area as the contact. A combined contact and tap is defined using a filled black square in place of the source contact (filled black circle).

A combined contact and tap can only be used where the end of a diffusion stick coincides with a contact to the power or ground rail.

#### • Stick Diagram Colour Code

| •                  |                  |  |

|--------------------|------------------|--|

| P Diffusion        | : Yellow/Brown   |  |

| N Diffusion        | : Green          |  |

| Polysilicon        | : Red            |  |

| Metal1             | : Blue           |  |

| Metal2             | : Purple/Magenta |  |

| Metal3             | : Cyan/Turquoise |  |

| Contacts<br>& Taps | : Black          |  |

Layout rules:

- 1. Stick diagram is a simple schematic representation of the layout of an integrated circuit. It shows the relative positions and sizes of the different components and interconnects on the chip. A stick diagram can be drawn by hand or using a computer-aided design (CAD) tool.

- The basic components of the MOS technology used in integrated circuits are the substrate, gate oxide, polysilicon gate electrode, and metal interconnects. The stick diagram shows the position and size of each of these components in the layout.

- 3. Layout rules are guidelines that specify the minimum dimensions and spacing requirements for various elements of the layout, such as the width and spacing of the metal interconnects, the minimum feature size of the transistor gate electrode, and the spacing between adjacent transistors.

- 4. The layout rules ensure that the final layout can be reliably fabricated using the available manufacturing technology. The rules also ensure the reliability and performance of the integrated circuit.

- 5. When creating a stick diagram, the designer should follow the layout rules to ensure that the final layout is manufacturable and reliable. The stick diagram can then be used as a basis for creating a more detailed layout.

- 6. Once the stick diagram is complete, the designer can use a CAD tool to create a more detailed layout. The CAD tool will automatically enforce the layout rules to ensure that the final layout is manufacturable and reliable.

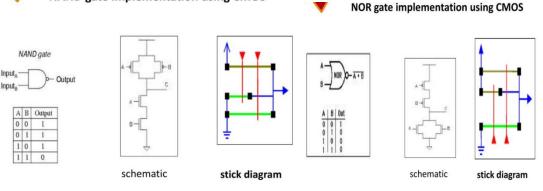

## 8. Draw the stick diagram and layout of inverter, NAND and NOR gates

NAND gate implementation using CMOS

## CMOS-Layout-Design

Layout of Logic gates:

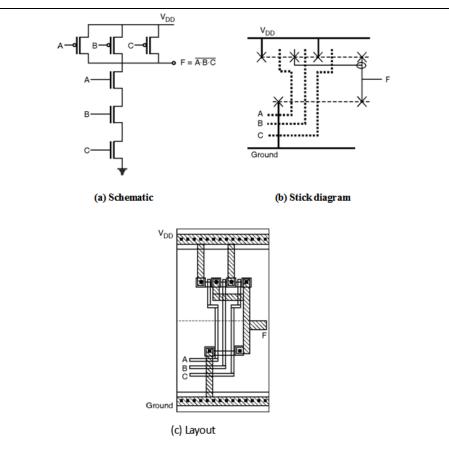

## Three Input NAND Gate :

Figure below shows, the schematic, stick diagram and layout of three input NAND gate.

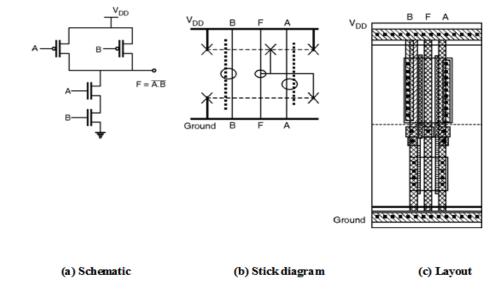

#### Two Input NAND Gate :

Figure below shows the schematic, stick diagram and layout of two input NAND gate implemented using complementary CMOS logic.

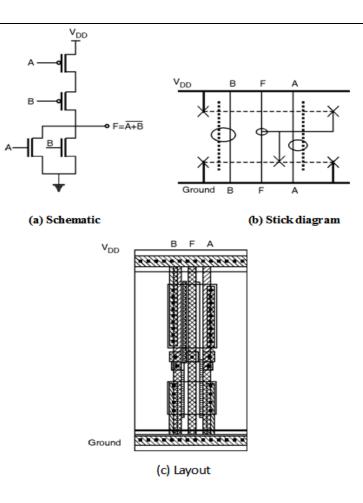

#### Two Input NOR Gate :

Figure below shows the schematic, stick diagram and layout of two input NOR gate implemented using complementary CMOS logic.

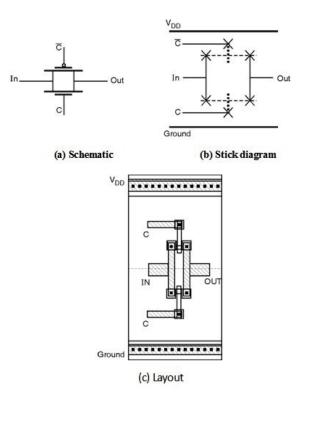

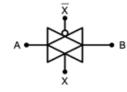

#### Transmission Gate :

Figure below shows the schematic, stick diagram and layout of the transmission gate.

#### 9. CMOS Lambda design rules

CMOS Lambda design rules are a set of guidelines for the physical layout of complementary metaloxide-semiconductor (CMOS) circuits. The term "lambda" refers to the minimum feature size of the process, which is typically represented as a multiple of the wavelength of light used in photolithography. For example, a 0.18 micron process might be referred to as a "0.18 micron Lambda" process, where the feature size is approximately one-half of the wavelength of the light used in photolithography.

Here are some common CMOS Lambda design rules:

- 1. Minimum feature size: The minimum feature size, or the smallest dimension that can be reliably patterned, is typically 0.5 to 0.7 times the Lambda. For example, in a 0.18 micron Lambda process, the minimum feature size might be 0.1 to 0.13 microns.

- 2. Minimum spacing between features: The minimum spacing between adjacent features should be at least twice the minimum feature size. This helps to prevent short circuits between adjacent components.

- 3. Active area spacing: The spacing between the active areas of adjacent transistors should be at least 3 times the minimum feature size. This helps to reduce capacitive coupling between adjacent transistors.

- 4. Metal width and spacing: The minimum width of a metal line is typically 2 to 3 times the minimum feature size. The spacing between adjacent metal lines should be at least twice the metal width.

- 5. Via size: The size of a via, which connects one metal layer to another, should be at least the same as the minimum metal width.

- 6. Contact size: The size of a contact, which connects a metal layer to the underlying active area, should be at least the same as the minimum feature size.

- 7. Gate spacing: The spacing between the gate and the active area of a transistor should be at least 2 to 3 times the minimum feature size. This helps to prevent leakage between the gate and the active area. These are just a few of the many design rules that must be followed when creating CMOS circuits. The specific rules may vary depending on the process technology and the requirements of the circuit being designed.

#### CMOS ' $\lambda$ ' Design Rules :

The MOSIS stands for MOS Implementation Service is the IC fabrication service available to universities for layout, simulation, and test the completed designs. The MOSIS rules are scalable  $\lambda$  rules.

- The MOSIS design rules are as follows :

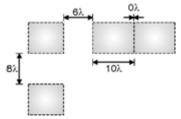

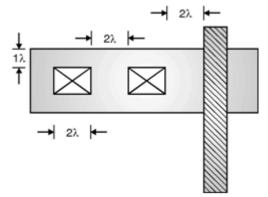

- (1) Rules for N-well as shown in Figure below.

- 1. Minimum width =  $10\lambda$

- 2. Wells at same potential with spacing =  $6\lambda$

- 3. Wells at same potential =  $0\lambda$

- 4. Wells of different type, spacing =  $8\lambda$

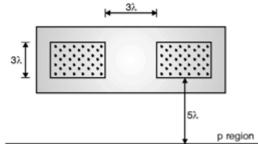

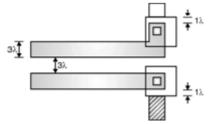

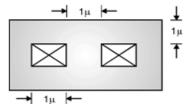

- (2) Rules for Active area shown in Figure below.

- 1. Minimum width =  $3\lambda$

2. Minimum spacing =  $3\lambda$

3. Source/Drain active to well

edge = 5λ

4. Substrate/well contact active

to well edge =  $3\lambda$

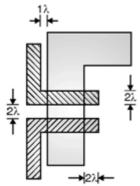

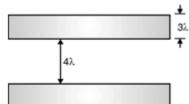

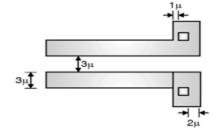

3) Rules for poly 1 as shown in Figure below.

- 1. Minimum width =  $2\lambda$

- 2. Minimum spacing =  $2\lambda$

- 3. Minimum gate extension of active =  $2\lambda$

- 4. Minimum field poly to active =  $1\lambda$

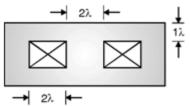

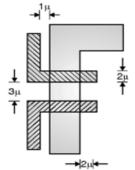

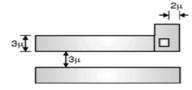

(4) Rules for contact to poly 1 as shown in Figure below.

2  $\lambda$ ×1. Exact contact size = 2  $\lambda$

- 2. Minimum poly 1 overlap = 1  $\lambda$

- 3. Minimum contact spacing = 2  $\lambda$

$2\lambda 2$ . Minimum active overlap =  $1\lambda 3$ . Minimum contact spacing =  $2\lambda 4$ . Minimum spacing to gate of transistor =  $2\lambda \times (5)$  Rules for contact to active as shown in Figure below. 1. Exact contact size =  $2\lambda$

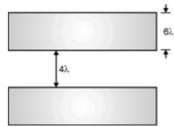

- (6) Rules for metal 1 as shown in Figure below.

- 1. Minimum width =  $3\lambda$

- 2. Minimum spacing =  $3\lambda$

- 3. Minimum overlap of poly contact =  $1\lambda$

- 4. Minimum overlap of active contact =  $1\lambda$

(7) Rules for via 1 as shown in Figure below.

$\lambda$ ×1. Minimum size =  $2\lambda$

- 2. Minimum spacing =  $3\lambda$

- 3. Minimum overlap by metal 1 =  $1\lambda$

(8) Rules for metal 2 as shown in Figure below.

1. Minimum size =  $3\lambda$

2. Minimum spacing =  $4\lambda$

(9) Rules for metal 3 as shown in Figure below.

1. Minimum width =  $6\lambda$

#### **Design Rule Check :**

In order to ensure that none of the design rules are violated CAD tools named Design Rule Checking (DRC) is used. If DRC is not verified then it leads to the non functional design.

The layout rules are grouped in three categories that are transistor rules, contact and via rules and well and substrate contact rules.

#### Transistor rules :

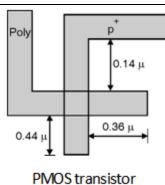

m which is the minimum width of active layer. $\mu$ m which is minimum width of polysilicon, whereas the width of the transistor is atleast 0.3  $\mu$ The transistor can be created by overlapping the the active and polysilicon layers. The minimum length of transistor equals 0.24

Figure below shows the layout of PMOS transistor.

Fig1-Design-Rule-Check

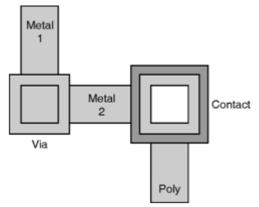

Contact and Via rules :

A contact forms an interconnection between metal and active or polysilicon layer whereas via forms an interconnection between two metal lines. A contact or via is formed by overlapping the two interconnecting layers and provides a contact hole filled with metal between the two. Figure below shows the contacts and via used in layout.

Fig1-Design-Rule-Check

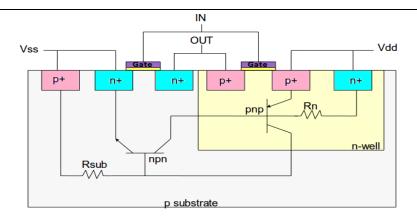

Well and substrate contact rules :

For digital circuit design it is important for the well and substrate regions to be connected to the supply voltages. If this is not done then a resistive path is created between the substrate contact of the transistors and the supply rails which leads to parasitic effects such as latch up.

## **CMOS-Layout-Design**

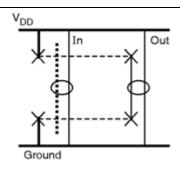

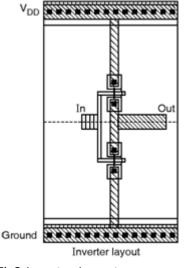

Inverter Layout :

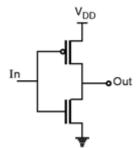

The schematic diagram of the inverter is as shown in Figure.

Fig1-Inverter-Layout The stick diagram of the schematic shown in Figure.

Fig2-Inverter-Layout

Here, the most important point to note is that as we change the placing of the components in the schematic the stick diagram and hence, the layout of the circuit will change accordingly. For example, if we place the components vertically the stick diagram will be vertical and if we place the components horizontally the stick diagram will be horizontal. Figure below shows the physical layout of inverter which is drawn in tanner tool.

Fig2-Inverter-Layout

#### \*\*\*\*\*\*\*\*\*\*\*

#### **10. Micron-Design-Rules**

Design Rules : Industry uses the micron design rules and code designs in terms of these micron dimensions. The micron design rules are as follows : ( $\mu$ )Micron

(1) Rules for N-well as shown in Figure below.

$\mu$ 1. Width = 3

(2) Rules for active area as shown in Figure below.

$\mu$ 1. Minimum size = 3

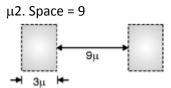

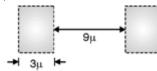

$\mu$ 2. Minimum spacing = 3

$\mu$ 2. N+ active to N-well = 7

(3) Rules for poly 1 as shown in Figure below.

$\mu$ 1. Width = 2

$\mu$ 2. Spacing = 3

$\mu$ 3. Gate overlap of active = 2

$\mu$ 4. Field poly 1 to active = 1

(4) Rules for contact to poly 1 as shown in Figure below.

$\mu$  2×  $\mu$ 1. Exact contact size = 2

$\mu$ 2. Minimum poly overlap = 1

$\mu$ 3. Minimum contact spacing = 2

(5) Rules for contact to active as shown in Figure below.

$\mu$  2×  $\mu$ 1. Exact contact size = 2

- $\mu$ 2. Minimum active overlap = 1

- $\mu$ 3. Minimum contact spacing = 2

- $\mu$ 4. Minimum spacing to gate = 2

- (6) Rules for metal 1 as shown in Figure below.

- $\mu$ 1. Width = 3

- $\mu$ 2. Spacing = 3

- $\mu$ 3. Overlap of contact = 1

- $\mu$ 4. Overlap of via = 2

- (7) Rules for metal 2 as shown in Figure below.

- $\mu$ 1. Width = 3

- $\mu$ 2. Space = 3

- $\mu$ 3. Metal 2 overlap of via = 2

#### .....

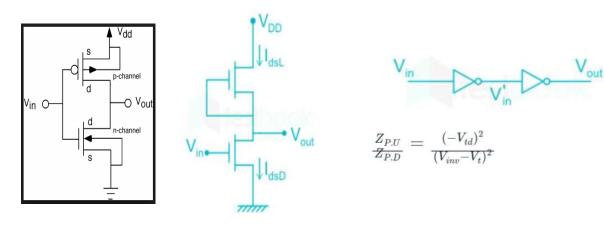

## **11.** Determination of Pull up to pull down ratio.

The pull-up to pull-down ratio is an important consideration in the design of CMOS circuits, as it affects the speed, power consumption, and noise immunity of the circuit. The pull-up to pull-down ratio is defined as the ratio of the resistance of the pull-up network to the resistance of the pull-down network in a CMOS inverter.

In general, the pull-up to pull-down ratio should be as close to 1 as possible to achieve balanced rise and fall times and minimize power consumption. However, the pull-up to pull-down ratio can also affect the noise margin and stability of the circuit. For example, a smaller pull-up to pull-down ratio can result in a lower noise margin but a faster switching speed, while a larger pull-up to pull-down ratio can result in a higher noise margin but a slower switching speed.

The determination of the pull-up to pull-down ratio can be done through simulation or analytical calculations. Here are some steps for the analytical calculation method:

- 1. Determine the switching threshold voltage (Vth) of the inverter. This is the input voltage at which the output voltage switches from high to low or low to high.

- 2. Calculate the resistance of the pull-up network (Rp) and pull-down network (Rn) using the following equations:

$$\begin{split} R_p &= V_{dd} / (I_{leak} + I_{sat}(p) * (V_{dd} - V_{th})) \\ R_n &= V_{dd} / (I_{leak} + I_{sat}(n) * V_{th}) \\ \text{where} \end{split}$$

V<sub>dd</sub> is the supply voltage,

$I_{leak}$  is the leakage current,

I<sub>sat</sub>(p) and I<sub>sat</sub>(n) are the saturation currents of the PMOS and NMOS transistors, respectively.

- 3. Calculate the pull-up to pull-down ratio  $(R_p/R_n)$  and evaluate its effect on the noise margin, switching speed, and power consumption of the circuit.

- 4. Adjust the size of the transistors in the pull-up and pull-down networks to achieve the desired pull-up to pull-down ratio.

It is important to note that the determination of the pull-up to pull-down ratio is highly dependent on the specific requirements of the circuit being designed and should be optimized based on the desired trade-offs between speed, power consumption, and noise immunity.

## 12. Comparing NMOS , PMOS CMOS and BiCMOS

#### NMOS:

- NMOS stands for "N-type Metal-Oxide-Semiconductor".

- It is a type of transistor that uses n-type semiconductor material for the channel.

- In NMOS, the gate voltage is typically higher than the source voltage to turn the transistor ON.

- NMOS is used primarily in digital circuits due to its fast switching speed and low power consumption.

- However, NMOS is not suitable for analog circuits due to its high output impedance and low noise immunity.

#### PMOS:

- PMOS stands for "P-type Metal-Oxide-Semiconductor".

- It is a type of transistor that uses p-type semiconductor material for the channel.

- In PMOS, the gate voltage is typically lower than the source voltage to turn the transistor ON.

- PMOS is used primarily in digital circuits due to its slow switching speed and high power consumption.

- However, PMOS is not suitable for analog circuits due to its high output impedance and low noise immunity.

#### CMOS:

- CMOS stands for "Complementary Metal-Oxide-Semiconductor".

- It is a type of transistor that uses both n-type and p-type semiconductor materials for the channel.

- In CMOS, both NMOS and PMOS transistors are used together in a complementary pair to achieve low power consumption and high noise immunity.

- CMOS is used extensively in digital circuits, including microprocessors, memory, and logic circuits.

#### BiCMOS:

- BiCMOS stands for "Bipolar Complementary Metal-Oxide-Semiconductor".

- It combines both bipolar junction transistors (BJTs) and CMOS transistors on the same chip.

- BiCMOS is used in applications that require high-speed switching, high current drive, and high voltage operation.

- BiCMOS is commonly used in mixed-signal circuits, such as ADCs, DACs, and voltage regulators.

| Parameter                 | NMOS                | PMOS                | CMOS                                                   | BiCMOS                                         |

|---------------------------|---------------------|---------------------|--------------------------------------------------------|------------------------------------------------|

| Device Type               | N-Channel<br>MOSFET | P-Channel<br>MOSFET | Complementary MOSFET (Both N-<br>and P-Channel MOSFET) | Combination of Bipolar<br>and CMOS transistors |

| Voltage polarity          | Negative            | Positive            | Both                                                   | Both                                           |

| Switching speed           | Fast                | Slow                | Fast                                                   | Very Fast                                      |

| Power<br>consumption      | Low                 | High                | Low                                                    | Very Low                                       |

| Noise immunity            | Low                 | High                | High                                                   | Very High                                      |

| Fabrication<br>complexity | Low                 | High                | Medium                                                 | High                                           |

| Input impedance           | Low                 | High                | Very High                                              | Very High                                      |

| Output<br>impedance       | High                | Low                 | Very Low                                               | Very Low                                       |

| Output swing              | Large               | Small               | Large                                                  | Large                                          |

| Voltage gain              | High                | Low                 | Very High                                              | High                                           |

| Current gain              | Low                 | High                | N/A                                                    | High                                           |

| Application               | Digital             | Digital             | Digital                                                | Analog and Digital                             |

#### Comparing NMOS, PMOS CMOS and BiCMOS

#### **VLSI** Design -Notes

#### UNIT II

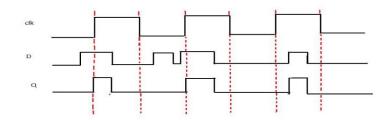

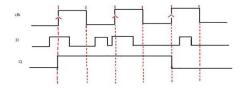

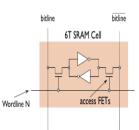

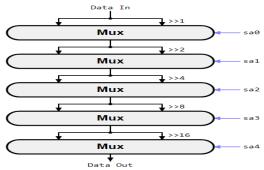

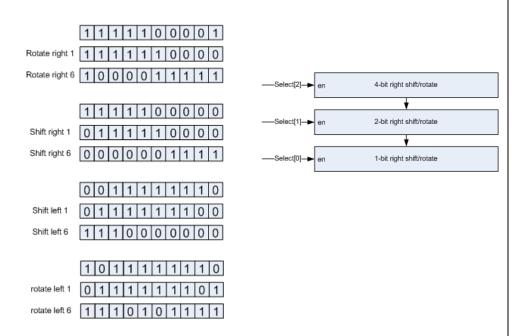

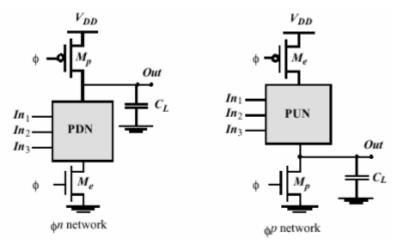

**Combinational And Sequential Circuit Design :** Pass transistor and transmission gates-inverter-NAND gates and NOR Gates for n MOS, CMOS and Bi CMOS – parity generator – multiplexers- code converters – Programmable Logic Devices (nMOS PLA and CMOS PLA) – Clocked sequential circuits – D-Latch and D- Flip-Flop –Memories (DRAM cell, SRAM Cell and Pseudo Static RAM cell) – Inverting and Non-inverting Registers – Barrel Shifter.

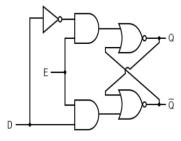

#### 1. Transmission-Gate | Pass-Transistor-Logic

Transmission Gate Logic: The transmission gate logic is used to solve the voltage drop problem of the pass transistor logic. This technique uses the complementary properties of NMOS and PMOS transistors. NMOS devices passes a strong '0' but a weak '1' while PMOS transistors pass a strong '1' but a weak '0'. The transmission gate combines the best of the two devices by placing an NMOS transistor in parallel with a PMOS transistor as shown in Figure below. The control signals to the transmission gate C and <sup>----</sup>C are complementary to each other. The transmission gate is mainly a bi-directional switch enabled by the gate signal 'C'. When C = 1 both MOSFETs are ON and the signal pass through the gate i.e. A = B if C = 1. Whereas C = 0 makes the MOSFETs cut off creating an open circuit between nodes A and B.

#### Transmission gate

In this section CMOS logic circuits that are based on transmission gate are implemented. This indicates the use of transmission gate to implement logic circuits.

#### **Basic Structure:**

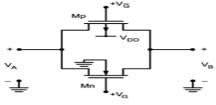

The basic structure of transmission gate is shown in Figure below which consists of NMOS and PMOS transistors. Here, VG is applied to NMOS, and (VDD- VG) applied to the PMOS.

CMOS transmission gate

The transmission gate work voltage-controlled switch. When VG is high, NMOS and PMOS are conducting hence switch is closed. Therefore, conduction path between left and right sides exist.

When VG is low, then the MOSFETs are in cutoff and switch is open. Therefore, there is no direct relationship between VA and VB.

Figure below shows the symbol of transmission gate controlled by switching signals X and X\* that are applied to the gates of NMOS and PMOS respectively.

| Х | A | В |

|---|---|---|

| 1 | 0 | 0 |

| 1 | 1 | 2 |

| ŏ | ĭ | ? |

(a) TG symbol

(b) Operation Transmission gate symbol

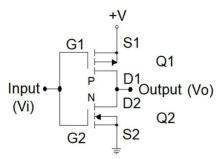

#### 2. The CMOS Inverter or NOT Gate

A NOT gate reverses the input logic state. Figure 1 shows a NOT gate employing two series-connected enhancement-type MOSFETS, one n-channel (NMOS) and one p-channel (PMOS).

Figure 1. A CMOS NOT gate.

The input is connected to the gate terminal of the two transistors, and the output is connected to both drain terminals.

Applying +V (logic 1) to the input (Vi), transistor Q2 is "on," and transistor Q1 remains "off." Under this condition, the output voltage (Vo) is close to 0 V (logic 0).

Connecting the input to ground (Vi = 0 V), transistor Q2 is "off," and transistor Q1 is "on." Now, the output voltage is close to +V (logic 1).

Table 1 summarizes these results.

| А | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

**Table 1.** The truth table for a NOT circuit.

#### The CMOS NAND Gate

NAND denotes NOT-AND.

Table 2 shows the truth table for a NAND circuit.

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table 2. The truth table for a two-input NAND circuit.

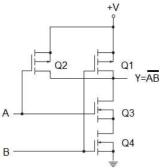

*Figure 2* shows a CMOS two-input NAND gate. P-channel transistors Q1 and Q2 are connected in parallel between +V and the output terminal. N-channel transistors Q3 and Q4 are connected in series between the output terminal and ground.

Figure 2. A CMOS two-input NAND gate.

With Q3 and Q4 transistors "on" and Q1 and Q2 transistors "off," the output is a logic 0. This condition happens when both inputs, A and B, are logic 1, confirming the lowest row in the above truth table.

With logic 0 in inputs A and B, Q3 and Q4 transistors are "off," and Q1 and Q2 transistors are "on," producing a logic 1 output. This is consistent with the first row of the truth table.

When one of the inputs is a logic "1" and the other one is a logic "0", either Q3 is "off" and Q2 is "on" or Q4 is "off" and Q1 is "on." The output in both cases is a logic "1," validating the second and the third rows of the truth table.

#### The NOR Gate

NOR signifies NOT-OR.

Table 3 shows the truth table for a NOR circuit.

| А | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Table 3. The truth table for a two-input NOR circuit.

The output of a NOR gate is logic 1 with logic 0 in both inputs. The outcomes for other input combinations are logic 0.

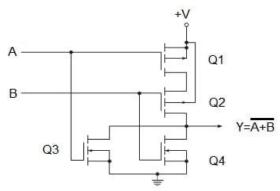

*Figure 3* shows a CMOS two-input NOR gate. P-channel transistors Q1 and Q2 are connected in series between +V and the output terminal. N-channel transistors Q3 and Q4 are connected in parallel between the output and ground.

Figure 3. A CMOS two-input NOR gate.

When both inputs, A and B, are logic 0, Q1 and Q2 are "on," and Q3 and Q4 are "off," and the output is logic 1. This confirms the first row of the truth table above.

With both inputs logic 1, Q3 and Q4 are "on," and Q1 and Q2 are "off," producing a logic 0 output that confirms the last row of the truth table. For the two remaining input combinations, either Q1 is "off" and Q3 is "on" or Q2 is "off" and is Q4 "on". In these cases, the output is logic 0 which is consistent with the above truth table.

\*\*\*\*\*\*

- **3. Programmable Logic Devices (PLD)** is the integrated circuits. They contain an array of AND gates & another array of OR gates. There are three kinds of PLDs based on the type of arrays, which has programmable feature.

- Programmable Read Only Memory(PROM)

- Programmable Array Logic(PAL)

- Programmable Logic Array(PLA)

The process of entering the information into these devices is known as programming. Basically, users can program these devices or ICs electrically in order to implement the Boolean functions based on the requirement. Here, the term programming refers to hardware programming but not software programming.

#### Programmable Read Only Memory PROM

*Read Only Memory (ROM)* is a memory device, which stores the binary information permanently. That means, we can't change that stored information by any means later. If the ROM has programmable feature, then it is called as Programmable ROM PROM. The user has the flexibility to program the binary information electrically once by using PROM programmer.

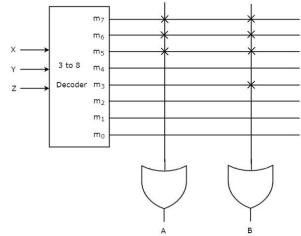

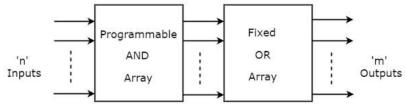

**PROM** is a programmable logic device that has fixed AND array & Programmable OR array. The block diagram of PROM is shown in the following figure.

Here, the inputs of AND gates are not of programmable type. So, we have to generate  $2^n$  product terms by using  $2^n$  AND gates having n inputs each. We

can implement these product terms by using nx2<sup>n</sup> decoder. So, this decoder generates 'n' min terms.

Here, the inputs of OR gates are programmable. That means, we can program any number of required product terms, since all the outputs of AND gates are applied as inputs to each OR gate. Therefore, the outputs of PROM will be in the form of sum of min terms.

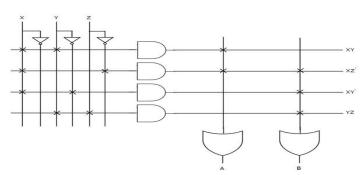

#### Example

#### Let us implement the following Boolean functions using PROM.

A(X,Y,Z)=∑m(5,6,7)

B(X,Y,Z)=∑m(3,5,6,7)

The given two functions are in sum of min terms form and each function is having three variables X, Y & Z. So, we require a 3 to 8 decoder and two programmable OR gates for producing these two functions. The corresponding PROM is shown in the following figure.

Here, 3 to 8 decoder generates eight min terms. The two programmable OR gates have the access of all these min terms. But, only the required min terms are programmed in order to produce the respective Boolean functions by each OR gate. The symbol 'X' is used for programmable connections.

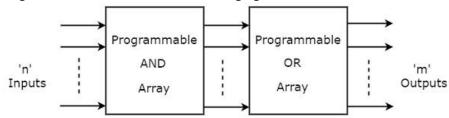

#### Programmable Array Logic (PAL)

PAL is a programmable logic device that has Programmable AND array & fixed OR array. The advantage of PAL is that we can generate only the required

product terms of Boolean function instead of generating all the min terms by using programmable AND gates. The block diagram of PAL is shown in the following figure.

Here, the inputs of AND gates are programmable. That means each AND gate has both normal and complemented inputs of variables. So, based on the requirement, we can program any of those inputs. So, we can generate only the required product terms by using these AND gates.

Here, the inputs of OR gates are not of programmable type. So, the number of inputs to each OR gate will be of fixed type. Hence, apply those required product terms to each OR gate as inputs. Therefore, the outputs of PAL will be in the form of sum of products form.

#### Example

#### Let us implement the following Boolean functions using PAL.

#### A=XY+XZ'

#### A=XY'+YZ'

The given two functions are in sum of products form. There are two product terms present in each Boolean function. So, we require four programmable AND gates & two fixed OR gates for producing those two functions. The corresponding PAL is shown in the following figure.

The programmable AND gates have the access of both normal and complemented inputs of variables. In the above figure, the inputs X, X', Y, Y', Z & Z', are available at the inputs of each AND gate. So, program only the

7

required literals in order to generate one product term by each AND gate. The symbol 'X' is used for programmable connections.

Here, the inputs of OR gates are of fixed type. So, the necessary product terms are connected to inputs of each OR gate. So that the OR gates produce the respective Boolean functions. The symbol '.' is used for fixed connections.

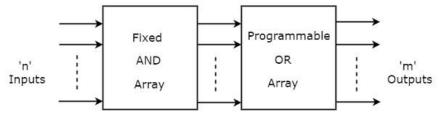

#### Programmable Logic Array (PLA)

PLA is a programmable logic device that has both Programmable AND array & Programmable OR array. Hence, it is the most flexible PLD. The block diagram of PLA is shown in the following figure.

Here, the inputs of AND gates are programmable. That means each AND gate has both normal and complemented inputs of variables. So, based on the requirement, we can program any of those inputs. So, we can generate only the required product terms by using these AND gates.

Here, the inputs of OR gates are also programmable. So, we can program any number of required product terms, since all the outputs of AND gates are applied as inputs to each OR gate. Therefore, the outputs of PAL will be in the form of sum of products form.

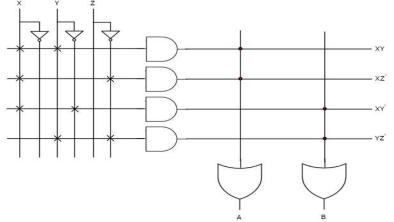

#### Example

#### Let us implement the following Boolean functions using PLA. A=XY+XZ'

#### B=XY'+YZ+XZ'

The given two functions are in sum of products form. The number of product terms present in the given Boolean functions A & B are two and three respectively. One product term, Z'X' is common in each function.

So, we require four programmable AND gates & two programmable OR gates for producing those two functions. The corresponding PLA is shown in the following figure.

The programmable AND gates have the access of both normal and complemented inputs of variables. In the above figure, the inputs X, X', Y, Y', Z & Z', are available at the inputs of each AND gate. So, program only the required literals in order to generate one product term by each AND gate.

All these product terms are available at the inputs of each programmable OR gate. But, only program the required product terms in order to produce the respective Boolean functions by each OR gate. The symbol 'X' is used for programmable connections.

#### \*\*\*\*\*\*\*

#### 4. Difference between PAL and PLA

The Difference between PAL and PLA in Tabular Form mainly includes PAL and PLA full form, construction, availability, flexibility, cost, number of functions, and speed which are discussed below.

| Programmable Array Logic (PAL)           | Programmable Logic Array (PLA)      |

|------------------------------------------|-------------------------------------|

| The full form of PAL is                  | The full form of the PLA is a       |

| programmable array logic                 | programmable logic array            |

|                                          | The construction of PLA can be done |

| The construction of PAL can be done      | using the programmable collection   |

| using the programmable collection        | of AND & fixed collection of OR     |

| of AND & OR gates                        | gates.                              |

| The availability of PAL is less prolific | The availability of PLA is more     |

| The flexibility of PAL programming is    |                                     |

| more                                     | The flexibility of PLA is less      |

| The cost of a PAL is expensive           | The cost of PLA is middle range     |

| The number of functions                  | The number of functions             |

| implemented in PAL is large              | implemented in PLA is limited       |

| The speed of PAL is slow                 | The speed of PLA is high            |

#### \*\*\*\*\*\*

## 5. Multipler

Multiplexer is a combinational circuit that has maximum of 2<sup>n</sup> data inputs, 'n' selection lines and single output line. One of these data inputs will be connected to the output based on the values of selection lines.

Since there are 'n' selection lines, there will be  $2^n$  possible combinations of zeros and ones. So, each combination will select only one data input. Multiplexer is also called as Mux.

## 4x1 Multiplexer

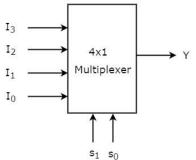

4x1 Multiplexer has four data inputs  $I_3$ ,  $I_2$ ,  $I_1 \& I_0$ , two selection lines  $s_1 \& s_0$  and one output Y. The block diagram of 4x1 Multiplexer is shown in the following figure.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines. Truth table of 4x1 Multiplexer is shown below.

| Selection Lines |                | Output         |

|-----------------|----------------|----------------|

| S <sub>1</sub>  | S <sub>0</sub> | Y              |

| 0               | 0              | I <sub>0</sub> |

| 0               | 1              | I <sub>1</sub> |

| 1               | 0              | l <sub>2</sub> |

| 1               | 1              | I <sub>3</sub> |

From Truth table, we can directly write the Boolean function for output, Y as

# $Y = S_1'S_0'I_0 + S_1'S_0I_1 + S_1S_0'I_2 + S_1S_0I_3$

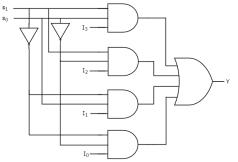

We can implement this Boolean function using Inverters, AND gates & OR gate. The circuit diagram of 4x1 multiplexer is shown in the following figure.

We can easily understand the operation of the above circuit. Similarly, you can implement 8x1 Multiplexer and 16x1 multiplexer by following the same procedure.

#### Implementation of Higher-order Multiplexers.

Now, let us implement the following two higher-order Multiplexers using lower-order Multiplexers.

- 8x1 Multiplexer

- 16x1 Multiplexer

8x1 Multiplexer

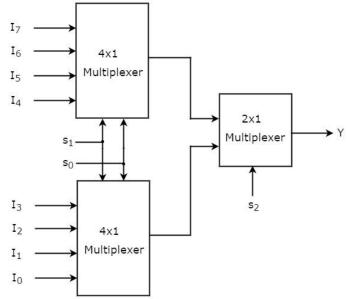

In this section, let us implement 8x1 Multiplexer using 4x1 Multiplexers and 2x1 Multiplexer. We know that 4x1 Multiplexer has 4 data inputs, 2 selection lines and one output. Whereas, 8x1 Multiplexer has 8 data inputs, 3 selection lines and one output.

So, we require two 4x1 Multiplexers in first stage in order to get the 8 data inputs. Since, each 4x1 Multiplexer produces one output, we require a 2x1 Multiplexer in second stage by considering the outputs of first stage as inputs and to produce the final output.

Let the 8x1 Multiplexer has eight data inputs  $I_7$  to  $I_0$ , three selection lines  $s_2$ ,  $s_1$  & s0 and one output Y. The Truth table of 8x1 Multiplexer is shown below.

Selection Inputs Output

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Y              |

|----------------|----------------|----------------|----------------|

| 0              | 0              | 0              | I <sub>0</sub> |

| 0              | 0              | 1              | I <sub>1</sub> |

| 0              | 1              | 0              | I <sub>2</sub> |

| 0              | 1              | 1              | I <sub>3</sub> |

| 1              | 0              | 0              | I <sub>4</sub> |

| 1              | 0              | 1              | I <sub>5</sub> |

| 1              | 1              | 0              | I <sub>6</sub> |

| 1              | 1              | 1              | l <sub>7</sub> |

We can implement 8x1 Multiplexer using lower order Multiplexers easily by considering the above Truth table. The block diagram of 8x1 Multiplexer is shown in the following figure.

The same selection lines,  $s_1 \& s_0$  are applied to both 4x1 Multiplexers. The data inputs of upper 4x1 Multiplexer are  $I_7$  to  $I_4$  and the data inputs of lower 4x1 Multiplexer are  $I_3$  to  $I_0$ . Therefore, each 4x1 Multiplexer produces an output based on the values of selection lines,  $s_1 \& s_0$ .

The outputs of first stage 4x1 Multiplexers are applied as inputs of 2x1 Multiplexer that is present in second stage. The other selection line,  $s_2$  is applied to 2x1 Multiplexer.

- If s<sub>2</sub> is zero, then the output of 2x1 Multiplexer will be one of the 4 inputs I<sub>3</sub> to I<sub>0</sub> based on the values of selection lines s<sub>1</sub> & s<sub>0</sub>.

- If  $s_2$  is one, then the output of 2x1 Multiplexer will be one of the 4 inputs  $I_7$  to  $I_4$  based on the values of selection lines  $s_1 \& s_0$ .

Therefore, the overall combination of two 4x1 Multiplexers and one 2x1 Multiplexer performs as one 8x1 Multiplexer.

\*\*\*\*\*\*

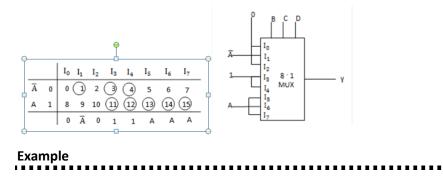

#### Example: Implementation of given function using 8 to 1 multiplexer

$F(A,B,C,D) = \Sigma (1,3,4,11,12,13,14,15)$

#### Solution.

Total number of variable n = 4 (A,B,C,D)

Number of select lines: n-1= 3 (B, C, D)

The given function has 4 variable, so 16 possible minterms (0 - 15) are entered in the implementation table.

All the minterms are divided into 2 groups

The first group (0-7) minterms are entered in the first row (Variable A =0)

The second group (8–15) minterms are entered in the second row (Variable A= 1)

Circle the minterm number as per function, which you have to implement (in this case it's 1,3,4,11,12,13,14,15)

Find out the multiplexer input as per above given steps.

Implement the following Boolean function using 8 : 1 MUX

F(A,B,C,D) = Σ m(0,1,2,4,6,9,12,14)

# Solution.

Select lines are B, C and D

Follow all the steps as per above points.

# Example

Implement the following Boolean function with 8 : 1 multiplexer

# F(A,B,C,D) = ∏M (0,3,5,6,8,9,10,12,14)

# Solution

The given maxterms are inverted to obtain minterms. From the minterms, we can implement the above Boolean function by using 8 : 1

multiplexer. Select lines are B, C and D, the input variable is A.

$F(A,B,C,D) = \Sigma m(1,2,4,7,11,13,15)$

# Example

# Implement the following Boolean function with 8 : 1 multiplexer

# $F(A,B,C,D) = \Sigma m (0,2,6,10,11,12,13) + \Sigma d(3,8,14)$

### Solution.

The Boolean function has three don't care conditions which can be treated as either 0's or 1's. In this example don't care condition is consider as

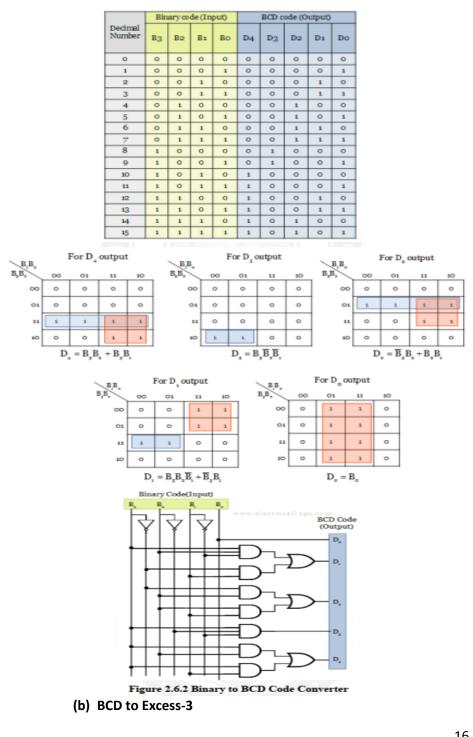

#### 3. Code converter

- Binary to BCD Conversion

- BCD to Binary Conversion

- BCD to Excess-3

- Excess-3 to BCD

(a) Binary to BCD Conversion

|                   | BC | CD cod | e (Inp | ut) | Excess-3 code (Output) |    |    | tput) |

|-------------------|----|--------|--------|-----|------------------------|----|----|-------|

| Decimal<br>Number | D3 | D2     | Dı     | Do  | E3                     | E2 | E1 | Eo    |

| 0                 | 0  | 0      | 0      | 0   | 0                      | 0  | 1  | 1     |

| 1                 | 0  | 0      | 0      | 1   | 0                      | 1  | 0  | 0     |

| 2                 | 0  | 0      | 1      | 0   | 0                      | 1  | 0  | 1     |

| 3                 | 0  | 0      | 1      | 1   | 0                      | 1  | 1  | 0     |

| 4                 | o  | 1      | o      | 0   | 0                      | 1  | 1  | 1     |

| 5                 | 0  | 1      | 0      | 1   | 1                      | 0  | 0  | 0     |

| 6                 | 0  | 1      | 1      | 0   | 1                      | 0  | 0  | 1     |

| 7                 | 0  | 1      | 1      | 1   | 1                      | 0  | 1  | 0     |

| 8                 | 1  | 0      | 0      | 0   | 1                      | 0  | 1  | 1     |

| 9                 | 1  | 0      | 0      | 1   | 1                      | 1  | 0  | 0     |

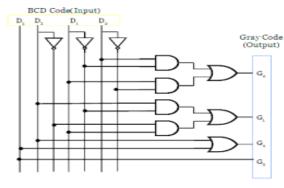

|                   | BO | CD cod | e (Inn | 111) | Gray code (Output) |    |    | (tur |

|-------------------|----|--------|--------|------|--------------------|----|----|------|

| Decimal<br>Number | D3 | D2     | D1     | Do   | G3                 | G2 | G1 | Go   |

| 0                 | 0  | 0      | 0      | 0    | 0                  | 0  | 0  | 0    |

| 1                 | 0  | 0      | 0      | 1    | 0                  | 0  | 0  | 1    |

| 2                 | 0  | 0      | 1      | 0    | 0                  | 0  | 1  | 1    |

| 3                 | 0  | 0      | 1      | 1    | 0                  | 0  | 1  | 0    |

| 4                 | o  | 1      | 0      | 0    | 0                  | 1  | 1  | o    |

| 0                 | 0  | 1      | 0      | 1    | 0                  | 1  | 1  | 1    |

| 6                 | 0  | 1      | 1      | 0    | 0                  | 1  | 0  | 1    |

| 7                 | 0  | 1      | 1      | 1    | 0                  | 1  | 0  | 0    |

| 8                 | 1  | 0      | 0      | 0    | 1                  | 1  | 0  | 0    |

| 9                 | 1  | 0      | 0      | 1    | 1                  | 1  | 0  | 1    |

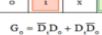

$$B_s = D_g \overline{D}_s + \overline{D}_g D_s$$

x

x

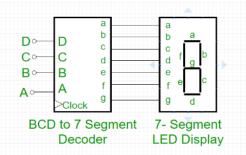

#### **BCD To 7 segments**

Truth Table - For common cathode type BCD to seven segment decoder:

| Α | В | С | D | а | b | С | d | е | f | g |

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

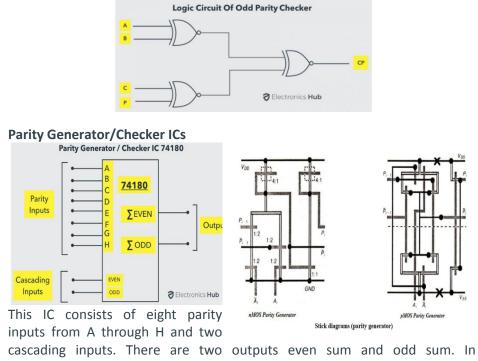

#### 6. Parity Generator and Parity Check

#### **Parity Generator**

It is combinational circuit that accepts an n-1 bit data and generates the additional bit that is to be transmitted with the bit stream. This additional or extra bit is called as a Parity Bit.

In even parity bit scheme, the parity bit is '0' if there are even number of 1s in the data stream and the parity bit is '1' if there are odd number of 1s in the data stream.

In odd parity bit scheme, the parity bit is '1' if there are even number of 1s in the data stream and the parity bit is '0' if there are odd number of 1s in the data stream. Let us discuss both even and odd parity generators.

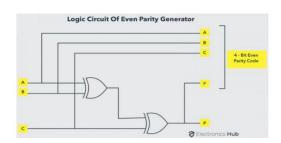

#### **Even Parity Generator**

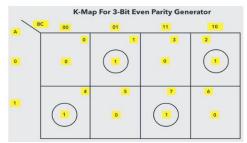

Let us assume that a 3-bit message is to be transmitted with an even parity bit. Let the three inputs A, B and C are applied to the circuit and output bit is the parity bit P. The total number of 1s must be even, to generate the even parity bit P. The figure below shows the truth table of even parity generator in which 1 is placed as parity bit in order to make all 1s as even when the number of 1s in the truth table is odd.

| 3 | -bit messa | ge | Even parity bit generator (P) |

|---|------------|----|-------------------------------|

| А | В          | с  | Y                             |

| 0 | 0          | 0  | 0                             |

| 0 | 0          | 1  | 1                             |

| 0 | 1          | 0  | 1                             |

| 0 | 1          | 1  | 0                             |

| 1 | 0          | 0  | 1                             |

| 1 | 0          | 1  | 0                             |

| 1 | 1          | 0  | 0                             |

| 1 | 1          | 1  | 1                             |

The K-map simplification for 3-bit message even parity generator is

From the above truth table, the simplified expression of the parity bit can be written as

$\mathbf{P} = \overline{\mathbf{A}} \ \overline{\mathbf{B}} \ \mathbf{C} + \overline{\mathbf{A}} \ \mathbf{B} \ \overline{\mathbf{C}} + \mathbf{A} \ \overline{\mathbf{B}} \ \overline{\mathbf{C}} + \mathbf{A} \ \mathbf{B} \ \mathbf{C}$

$=\overline{A}(\overline{B}C+\underline{B}\overline{C})+A(\overline{B}\overline{C}+BC)$

$=\overline{A}(B \oplus C) + A(\overline{B \oplus C})$

$P = A \oplus B \oplus C$

The above expression can be implemented by using two Ex-OR gates. The logic diagram of even parity generator with two Ex - OR gates is shown below. The three bit message along with the parity generated by this circuit which is transmitted to the receiving end where parity checker circuit checks whether any error is present or not.

To generate the even parity bit for a 4-bit data, three Ex-OR gates are required to add the 4-bits and their sum will be the parity bit.

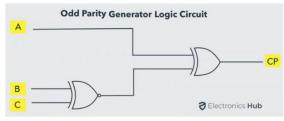

# **Odd Parity Generator**

Let us consider that the 3-bit data is to be transmitted with an odd parity bit. The three inputs are A, B and C and P is the output parity bit. The total number of bits must be odd in order to generate the odd parity bit.

In the given truth table below, 1 is placed in the parity bit in order to make the total number of bits odd when the total number of 1s in the truth table is even.

|   | 3-bit messa | ge | Odd parity bit generator (P) |

|---|-------------|----|------------------------------|

| А | в           | с  | Y                            |

| 0 | 0           | 0  | 1                            |

| 0 | 0           | 1  | 0                            |

| 0 | 1           | 0  | 0                            |

| 0 | 1           | 1  | 1                            |

| 1 | 0           | 0  | 0                            |

| 1 | 0           | 1  | 1                            |

| 1 | 1           | 0  | 1                            |

| 1 | 1           | 1  | 0                            |

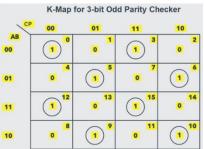

The truth table of the odd parity generator can be simplified by using K-map as

The output parity bit expression for this generator circuit is obtained as

$P = A \oplus (B \oplus C)$

The above Boolean expression can be implemented by using one Ex-OR gate and one Ex-NOR gate in order to design a 3-bit odd parity generator.

The logic circuit of this generator is shown in below figure, in which two inputs are applied at one Ex-OR gate, and this Ex-OR output and third input is applied

to the Ex-NOR gate, to produce the odd parity bit. It is also possible to design this circuit by using two Ex-OR gates and one NOT gate.

# **Parity Check**

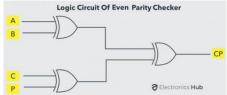

It is a logic circuit that checks for possible errors in the transmission. This circuit can be an even parity checker or odd parity checker depending on the type of parity generated at the transmission end. When this circuit is used as even parity checker, the number of input bits must always be even.

#### **Even Parity Checker**

Consider that three input message along with even parity bit is generated at the transmitting end. These 4 bits are applied as input to the parity checker circuit, which checks the possibility of error on the data. Since the data is transmitted with even parity, four bits received at circuit must have an even number of 1s.

If any error occurs, the received message consists of odd number of 1s. The output of the parity checker is denoted by PEC (Parity Error Check).

The below table shows the truth table for the Even Parity Checker in which PEC = 1 if the error occurs, i.e., the four bits received have odd number of 1s and PEC = 0 if no error occurs, i.e., if the 4-bit message has even number of 1s.

| 4- | bit receive | ed messag | D. H. H. H. C. |                                   |

|----|-------------|-----------|----------------|-----------------------------------|

| Α  | В           | С         | Р              | Parity error check C <sub>p</sub> |

| 0  | 0           | 0         | 0              | 0                                 |

| 0  | 0           | 0         | 1              | 1                                 |

| 0  | 0           | 1         | 0              | 1                                 |

| 0  | 0           | 1         | 1              | 0                                 |

| 0  | 1           | 0         | 0              | 1                                 |

| 0  | 1           | 0         | 1              | 0                                 |

| 0  | 1           | 1         | 0              | 0                                 |

| 0  | 1           | 1         | 1              | 1                                 |

| 1  | 0           | 0         | 0              | 1                                 |

| 1  | 0           | 0         | 1              | 0                                 |

| 1  | 0           | 1         | 0              | 0                                 |

| 1  | 0           | 1         | 1              | 1                                 |

| 1  | 1           | 0         | 0              | 0                                 |

| 1  | 1           | 0         | 1              | 1                                 |

| 1  | 1           | 1         | 0              | 1                                 |

| 1  | 1           | 1         | 1              | 0                                 |

The above truth table can be simplified using K-map as shown below.

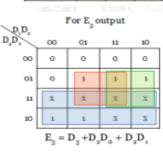

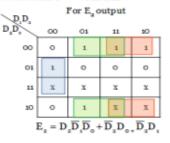

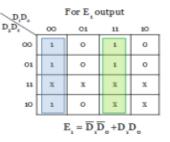

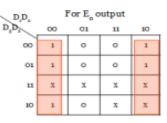

|          |         | For Even Par | ity Checker |         |

|----------|---------|--------------|-------------|---------|

| •        | P 00    | 01           | 11          | 10      |

| АВ<br>00 | 0       |              | 0           | 1 2     |

| 01       | 1 4     | 0            | 1 7         | 0       |

| 11       | 0<br>12 | 1 13         | 0           | 1 14    |

| 10       | 1 8     | 9            | 1 11        | 10<br>0 |